声明:作者是做嵌入式软件开发的,并非专业的硬件设计人员,笔记内容根据自己的经验和对协议的理解输出,肯定存在有些理解和翻译不到位的地方,有疑问请参考原始规范看

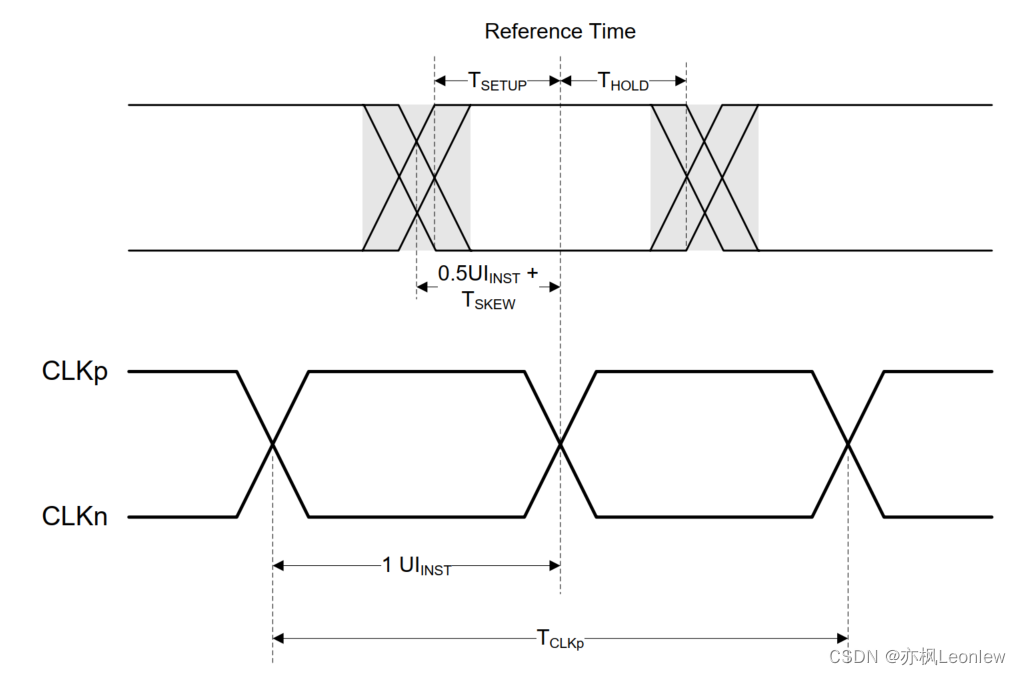

DDR时钟差分信号和Data差分信号的时序关系如下图所示:

图1 Data to Clock Timing Definitions

数据以正交于时钟的关系被发出,因此时钟信号边沿可以被接收器直接用于采样接收到的数据。

发送器要确保在一次burst传输的第一个载荷bit期间,发送一个DDR时钟的上升沿,这样第一个载荷bit能够在这个上升时钟沿上被接收器所采样,第二个载荷bit在下降沿上被采样,随后的数据bits,会在交替的上升沿和下降沿上被采样。

数据时钟时序规范

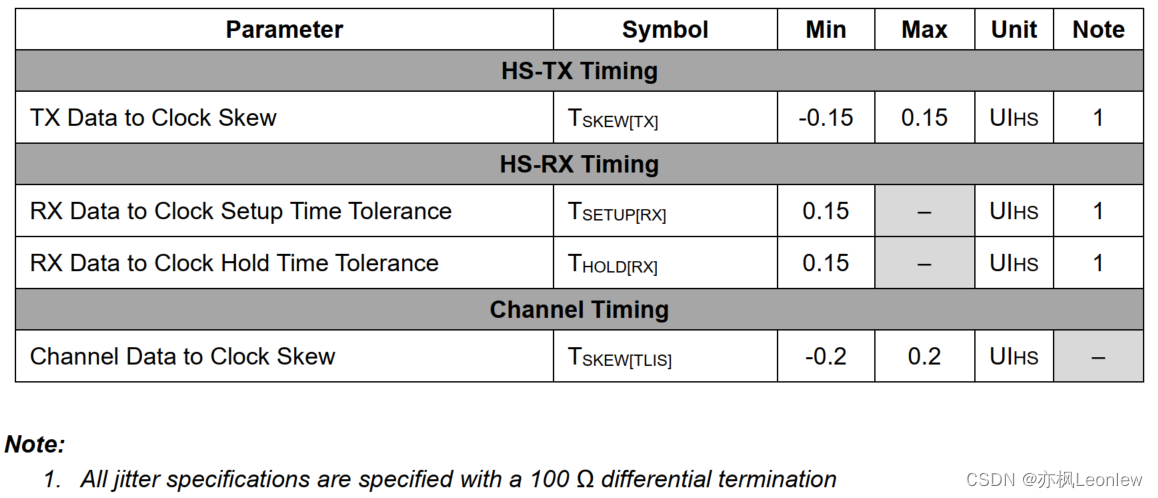

Data Rate ≥ 0.08 Gbps and ≤ 1 Gbps

图2 Data-Clock Timing Specifications for ≥ 0.08 Gbps and ≤ 1 Gbps

Skew的规范表示数据发出时间对于理想的位移½UIINST的正交时钟边沿(displaced quadrature clock edge)所允许的偏差。

和

都描述了数据和时钟之间的关系。

是在一个时钟上升沿和下降沿到来之前,数据建立的最小时间;

是在一个时钟上升或下降沿之后,数据保持的最小时间。

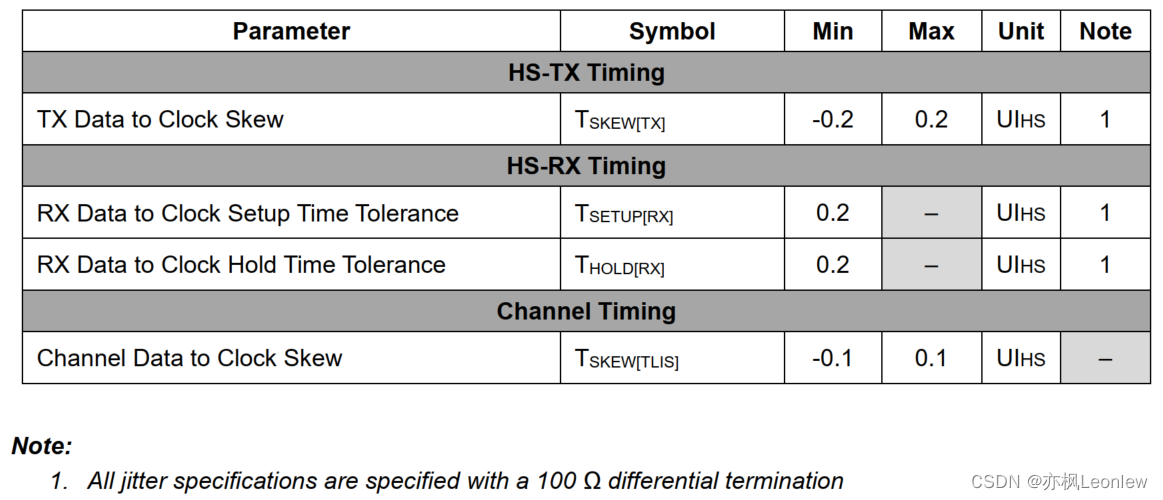

Data Rate > 1 Gbps and ≤ 1.5 Gbps

图3 Data-Clock Timing Specifications for > 1 Gbps and ≤ 1.5 Gbps

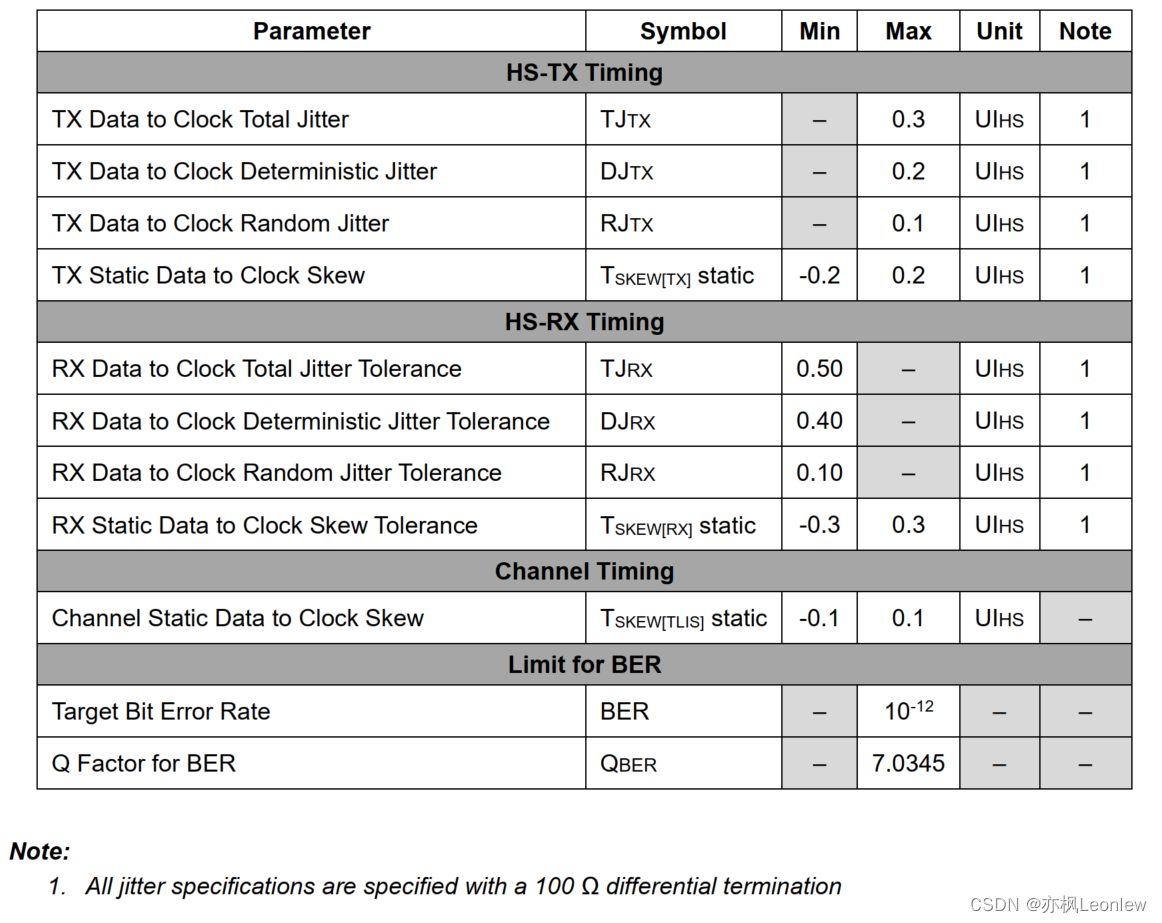

Data Rate > 1.5 Gbps and ≤ 4.5 Gbps 图4 Data-Clock Timing Specifications for > 1.5 Gbps and ≤ 4.5 Gbps

图4 Data-Clock Timing Specifications for > 1.5 Gbps and ≤ 4.5 Gbps