低功耗芯片设计是本世纪以来最重要的新兴设计方法。可以说没有低功耗设计,就没有今天的智能手机,移动设备,物联网,及高性能计算等产业。随着芯片图形尺寸越来越小,低功耗设计在现在及未来的芯片中会起到越来越重要的作用。低功耗技术也贯穿整个SoC设计的流程,可以预见的是低功耗设计也将越来越重要,所以深入理解低功耗技术是我们芯片设计进阶的必经之路

目录

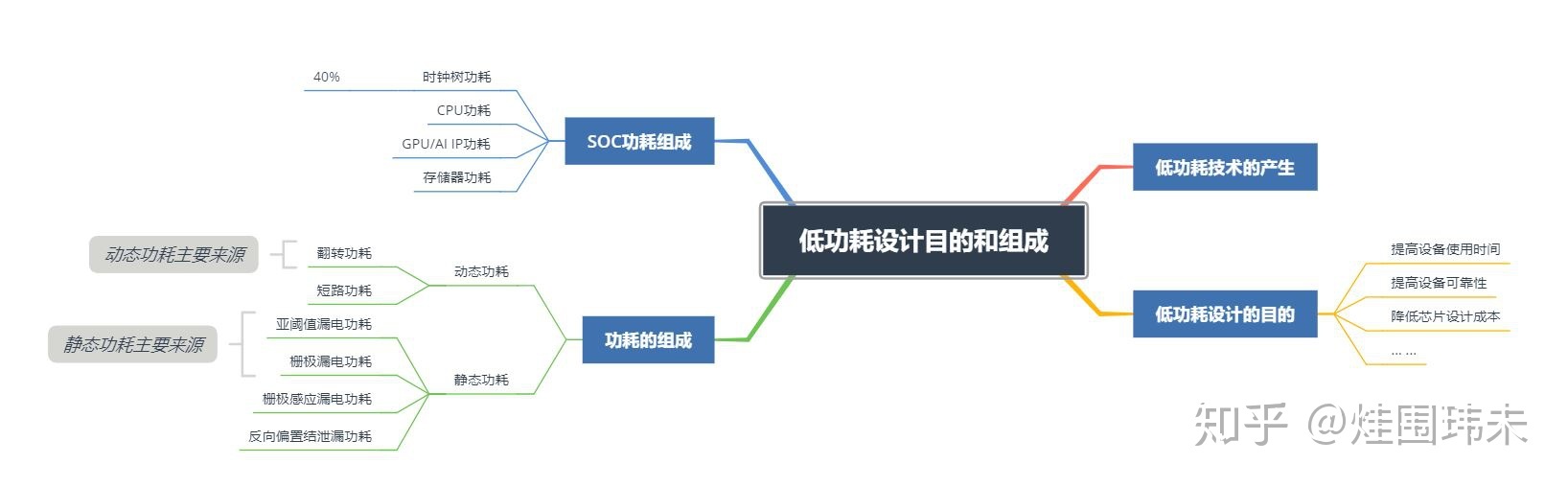

一、为什么要降低芯片功耗

二、集成电路的功耗来源

(1)动态功耗可以分为:

(2)静态功耗:

(3)动态和静态功耗总结:

三、不同结构的功耗组成

四、如何降低功耗

(1)从算法优化的角度:

(2)从模块级角度:

五、总结

一、为什么要降低芯片功耗

功耗(Power)和能量(Energy)是两个完全不同的概念,但是生活中很多人会把他们混淆起来。功耗是一个瞬时的概念,而能量是一个时间内的消耗。能量=功耗*时间。

这事儿其实好理解,原因很多,比如电源网络不好设计,芯片容易失效等等。但是最重要的我认为就三点(敲黑板):

续航太短,散热太大,成本太高。

1.提高电池供电的电子产品的使用时间(针对续航太短)。

这个是大家最直观的感受。比如手机,现在“充电五分钟,通话两小时”已经是标配了。如果是“充电两小时,通话五分钟”那场景不忍直视了。还有,电动汽车,现在的电池容量和续航里程已经是直接的竞争指标了。记得最深刻的是,当年高通骁龙820就是功耗没做好,输给了麒麟920,给了华为麒麟崛起的机会。现在华为手机电池耐用已经深入人心了。可以看到,低功耗技术直接决定商业竞争的成败,这是“几千亿的大生意”啊(手动狗头)!

2. 提高设备的可靠性(针对散热太大)

随着设备消耗能量,会产生热量。功耗越大,产生热量越快。如果不能及时散热,那么设备温度就会升高。温度升高可能导致设备不能正常工作甚至损坏。所以有些芯片会在温度升高时候,把频率降低,本来能跑2GHz的CPU,温度高了就只能跑1G,这个以前在用手机玩游戏的时候体验比较明显。你肯定不乐意用个核显还非要上个水冷。

3. 降低成本(针对成本太高)

功耗越大,产生热量越快,对封装,散热系统等要求越高。比如,低功耗的只需要塑料封装就能保证正常功能,高功耗的就可能需要陶瓷封装,成本自然就高很多。再比如,低功耗的可能自然散热就能保证正常功能,高功耗的可能需要水冷,加铜片等等,这些都会导致成本上升。成本的高低直接决定商业的成败,可能你能做出功能很强的产品,但是如果做出来没人买的起,或者同等功能下,别的公司成品低很多,那也是一个失败的产品。

所以综上所述,功耗要尽量做小就是了。

二、集成电路的功耗来源

既然要优化功耗,我们先看看功耗是怎么造成的。现代大规模集成电路里面广泛用的是CMOS, Complementary Mosfet, 互补的晶体管。原理上上下两个晶体管不同时导通,应该没有功耗,妥妥的永动机(狗头)。但实际上有非理想因素在,功耗就是这么产生的。芯片的功耗=动态功耗+静态功耗。动态功耗是设备运行时或者说信号改变时所消耗的功耗;静态功耗是设备上电但是信号没有改变时所消耗的功耗;这里要注意的是:在设备运行时,也需要消耗静态功耗的,因为设备运行时也是上电状态。功耗分类把静态功耗单独拿出来,只是为了理论分析方便。

(1)动态功耗可以分为:

- 翻转功耗(有的地方称为开关功耗,但是笔者认为这个名字不准确,因为开关包含的功耗很多,其实是从英文switching power翻译过来,从switching可以看到,名称想表现是动作。所以称为翻转功耗比较准确)。Switching power 是一个门电路对输出电容进行充电和放电需要的功耗。简单的说就是一个门电路输出从0变到1和从1变到0所需要消耗的功耗。Switching power 是动态功耗最主要的组成部分。

- 短路功耗(或者称为内部功耗,英文是internal power)。内部功耗又可以称为短路功耗,因为主要原因是由于短路造成的。短路功耗是因为在输入信号进行翻转时,信号的翻转不可能瞬时完成,因此PMOS和NMOS不可能总是一个截止另外一个导通,总有那么一段时间是使PMOS和NMOS同时导通,那么从电源VDD到地VSS之间就有了通路,就形成了短路电流。由于传输中短路持续的时间特别短,短路功耗相比翻转功耗来说小很多。所以一般情况下会忽略短路功耗,把翻转功耗就当作动态功耗,那么动态功耗的简化公式就是:

(1)

N是晶体管数量,A是翻转因子,C是寄生电容,V是电源电压,F是频率。所以power和VDD二次方成正比,和频率一次方成正比。主要降低功耗也就是围绕这几个因子来转。

(2)静态功耗:

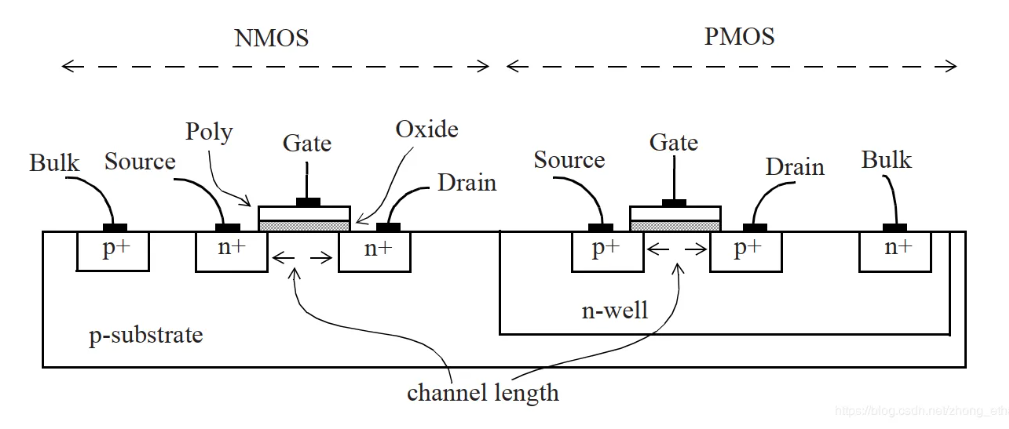

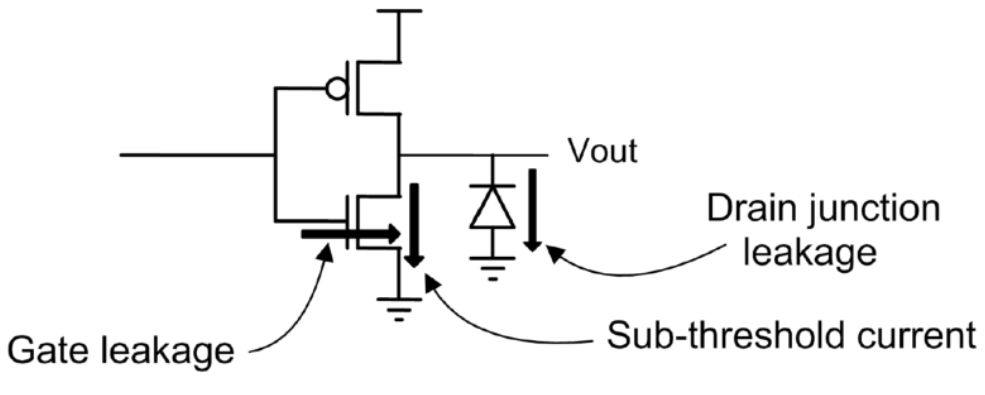

静态功耗是由于漏电流引起的,在CMOS 门中,漏电流主要来自4个源头:

- 亚阈值漏电流(Sub-threshold Leakage, ISUB): 亚阈值泄漏电流是晶体管应当截止时流过的电流。亚阈值泄漏电流随温度呈指数增长(Vth)。这大大增加了设计低功率系统的复杂性。即使在室温下的泄漏是可以接受的,在最坏的情况下,温度会超过芯片的设计目标。

- 栅极漏电流(Gate Leakage, Igate): 由于栅极氧化物隧穿和热载流子注入,从栅极直接通过氧化物流到衬底的电流。泄漏电流与介质厚度有极强的关系。工艺中通过选择合适厚度的介质将栅泄漏电流限制到一个可接受的水平上。泄漏电流还取决于栅极电压。通过使晶体管堆叠起来并使截止晶体管靠近电源/地线可以使栅泄漏电流减小。

- 栅极感应漏电流(Gate Induced Drain Leakage, IGIDL): 结泄漏电流发生在源或漏扩散区处在与衬底不同电位的情况下。结泄漏电流与其他泄漏电流相比时通常都很小。电流占比比较小,所以一般不做分析。

- 反向偏置结泄漏(Reverse Bias Junction Leakage ,IREV):由少数载流子漂移和在耗尽区产生电子/空穴对引起。电流占比比较小,所以一般不做分析。

Mos管图示

漏极电流组成图示

综上,可以把静态功耗统一为一个公式:

(2)

Ipeak为泄露电流,减少静态功耗的方法就是减小VDD和Ipeak。

(3)动态和静态功耗总结:

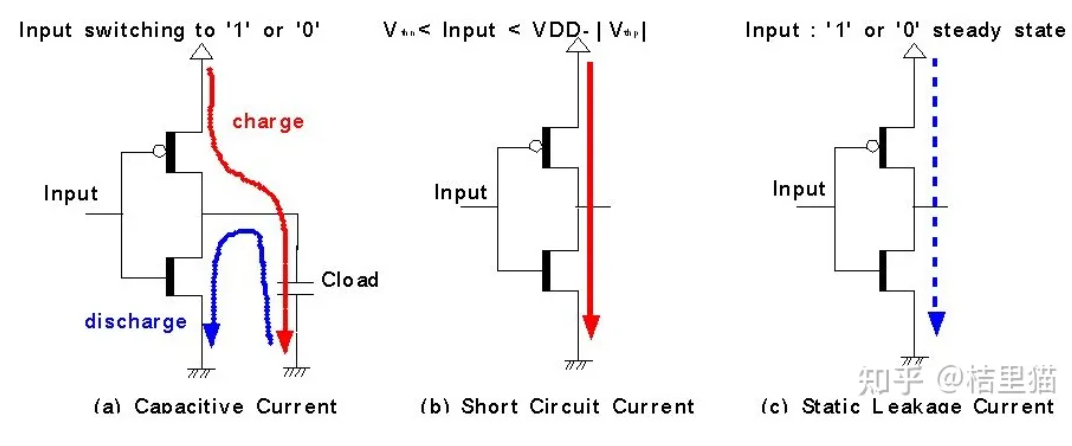

电容充放电和短路电流是动态功耗,漏电流是静态功耗。动态功耗一般来讲远大于静态功耗。抓大放小,我们这个地方主要记住大头充放电功耗怎么算的。

- 电容充放电电流。看图a, 实际上晶体管与地之间是有点容的。所以输入从0到1变化的时候会导致这个电容充放电。当input为0的时候能量从VDD冲到了电容, input 为1的时候能量直接流到地。

- 短路电流。由于晶体管非理想,存在某个电压,NMOS和PMOS都导通,导致直接有VDD到VSS的通路。产生电流。

- 漏电流。漏电流是input稳定的时候,其实VDD和VSS之间也有细微的电流流过产生功耗。

补充:

1.在电路里:

- VDD的意思:电源电压(单极器件);电源电压(4000系列数字电路);漏极电压(场效应管)。

- VCC的意思:电源电压(双极器件);电源电压(74系列数字电路);声控载波(Voice Controlled Carrier)。

- VSS的意思:通常指电路公共接地端电压或电源负极。

- VEE的意思:负电压供电;场效应管的源极(S)。

2.在电路里的晶体管上:

- VSS表示连接到场效应管的源极(Source)的电源。

- VDD表示连接到场效应管的漏极(Drain)的电源。

- VEE表示连接到三极管发射极(Emitter)的电源。

- VCC表示连接到三极管集电极(Collector)的电源

三、不同结构的功耗组成

SoC芯片中不同结构的对功耗的消耗是不一样的。有几个功耗大户如下:

- 时钟树功耗:时钟树的功耗通常占整个SOC功耗的40%左右,这是因为时钟是一直在翻转的信号,所以动态功耗特别大。所以门控时钟技术就特别重要。

- CPU: CPU是SOC主控制器,工作时CPU一般都必须要打开,随着CPU频率越来越高,功耗也越来越大。所以现在的多核,大小核就比较流行,不同场景下用不同功耗的CPU核;

- GPU: GPU是并行处理单元,由于其算力主要来自多个模块并行计算,为了正常工作,通常需要很多模块同时运算,功耗也很大,所以很多SOC都不带GPU或者默认关掉;

- 存储器:DDR这些存储器作为SOC主存也需要时刻使用,也是功耗消耗的大户。

SOC还有很大其他模块,但是时钟树,CPU/GPU, 存储器占了绝大部分的功耗。在AI芯片的时代,CCN IP也是功耗的主要来源,和GPU比较类似。

四、如何降低功耗

综上所述,对芯片的功耗进行控制是十分重要的一环,常见的手段如下:

(1)从算法优化的角度:

降低A和N:减少计算复杂度。算法最有效的做法是直接减少算法的复杂度。比如同样一个人脸识别的AI芯片,在识别精度相同的情况下,使用VGG明显比使用ResNet甚至MobileNet这些轻量化网络费功耗的多。所以算法部门一个永恒的目标是如何在不太损失精度的前提下降低计算复杂度。有时候同样一个任务精度一样计算复杂度可能会降低十倍不止。

降低A:算法优化翻转概率。这个事情比较玄学。比如训练一个神经网络,尽量让网络推理的过程中翻转概率最低。再比如算法来个自适应,在信号比较好的时候采用一个比较弱的信道估计,在信号不好的时候启动比较强的信道估计等等。

降低N:降低计算精度。对于芯片来讲,除了特殊需求,大多数计算都是定点的。那采用什么精度的定点就很容易影响功耗。比如计算神经网络的时候,由于网络自身就可以容错,算法可以不断压缩定点。比如用个8bit, 4bit看看结果如何。这部分大量运用于各类芯片。尤其神经网络,通信等等。如何降低精度有一系列的办法。采用指数压缩,分组定点化等等。举个简单的例子,可以让神经网络不通层有不同的定点化来降低计算精度。

(2)从模块级角度:

降低A:Clock Gating。一般模块级的clock gating信号都要我们手动根据设计功能加入的。比如在CPU核没有任务的时候要把CPU的clock直接关掉,节省时钟网络的功耗。

降低V:Power Gating。对于能预测长时间不用的模块,要设计power gating, 将不用的模块直接关掉。如下图所示,一个CPU系统,其实Memory可能不能掉电,Core和MAC什么的如果不用都可以power gating。power gating有一定成本(功耗和面积上都有),所以一个模块要不要做power gating要逐个分析。

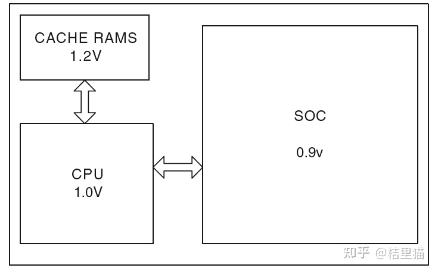

降低V:Multi-VDD。现在的芯片都比较大,没必要所有模块都跑在一个电压下。比如下面这样,CACHE RAMS电压高一点,SoC部分电压可以低一点。

降低F: Multi-Clock Domain. 和上一条往往有联动关系,这个地方还附带有另一个效果,降低F。可以根据电压域讲芯片分为若干的时钟域,有些部分时钟慢一些来减小功耗。

降低V和F:DVFS。Dynamic Voltage and Frequency Scaling。这个是现代芯片中非常常用的手段。根据业务负载自动的调整电压和频率。如下图所示,一般来讲,电压越高芯片能跑的频率也就越高。DVFS就是反其道行之。比如手机只有2G网,手机芯片就显然不用跑在最高频率。从而可以大量减少功耗。

五、总结

低功耗技术是SoC芯片设计必须掌握的技术,不是之一。因为我们正处在低功耗芯片设计的时代。如果你不懂低功耗技术,那么可能你就很难理解整个芯片设计中各种做法的原因,甚至很难听懂别人讨论时的“行话”,这些才是最致命的,可能会让人觉得你还没“入行”。

参考资料:

一文看懂CMOS集成门电路 - 知乎 (zhihu.com)

(10 封私信 / 80 条消息) 桔里猫 - 知乎 (zhihu.com)

芯片设计进阶之路——低功耗深入理解(一) - 知乎 (zhihu.com)

![[附源码]计算机毕业设计springboot电商小程序](https://img-blog.csdnimg.cn/f64b56c793b84f528a8837f773a7f4e4.png)

![[附源码]计算机毕业设计Springboot大学生志愿者服务管理系统](https://img-blog.csdnimg.cn/dd196b4ca6d54952abd4bdc894f5f4bf.png)