由于CPU和主存储器之间的速度上的不匹配限制了计算机系统的工作速度,为了提高CPU和主存之间的数据传输率,可以采用并行技术的存储器:

- 双端口存储器

- 多模块交叉存储器

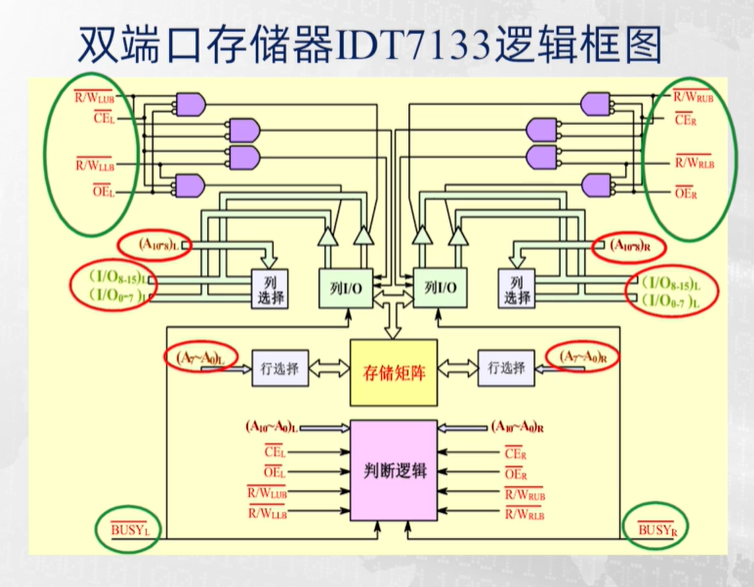

双端口存储器

- 同一个存储器具有两组相互独立的读写控制线路,是一种高速工作的存储器

- 两个端口分别具有各自的地址线、数据线和控制线

- 两个端口可对存储器中的任何位置上的数据进行独立的存取操作

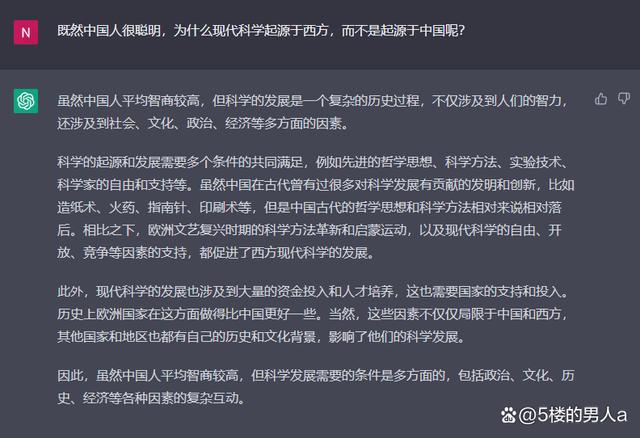

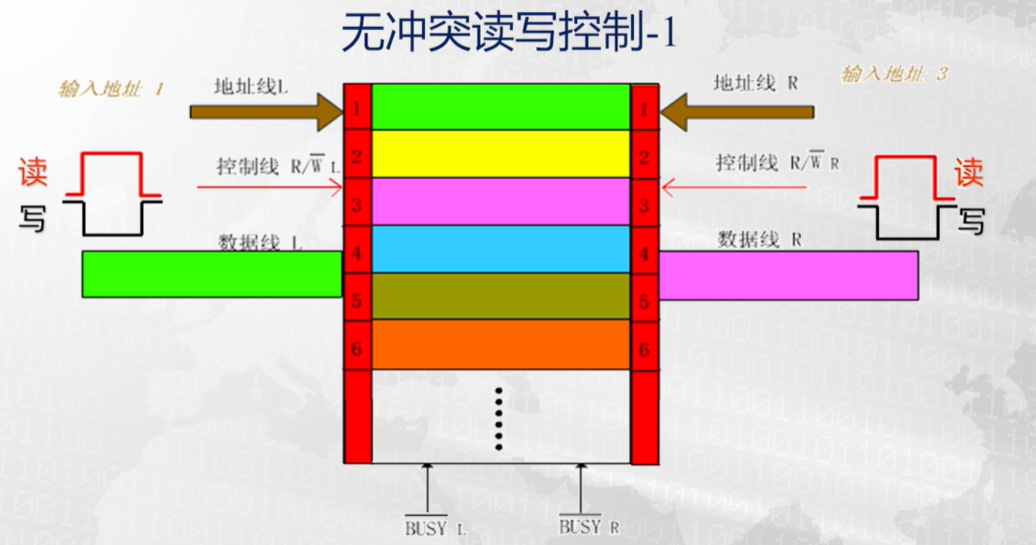

- 无冲突的读写控制1

当两个端口上的地址不相同时,在两个端口上进行读写操作,一定不会发生冲突

- 无冲突读写控制2

当两个端口地址相同,但是都进行的是读操作时,也不会发生冲突

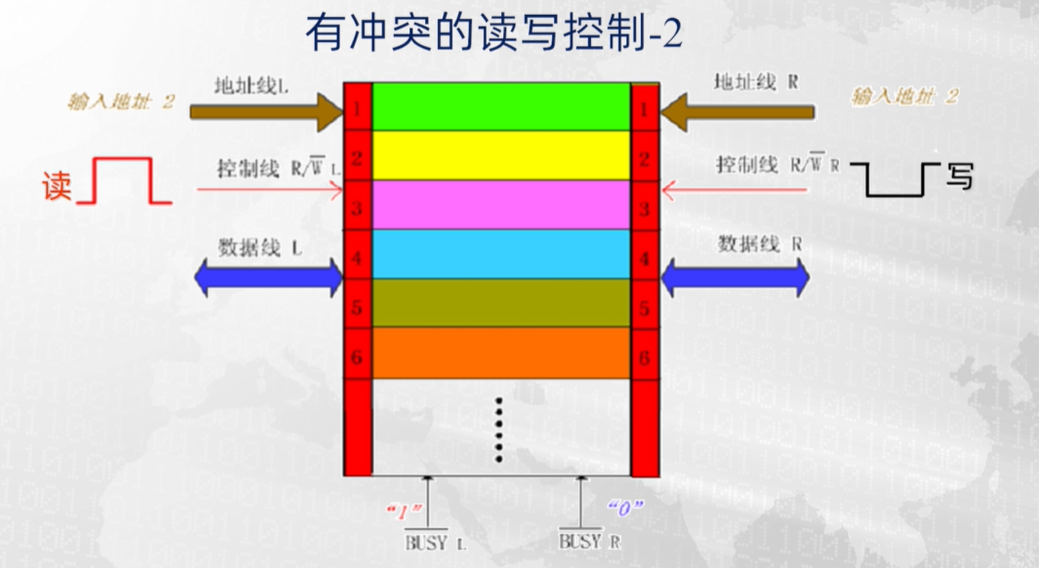

- 有冲突读写1

当两个端口至少有一个进行写操作时,就会发生冲突

当两个端口都执行写命令时,无法判断是哪个端口先写入

- 有冲突读写2

当一个端口为读,一个端口为写时,不知道是先读出还是先写入

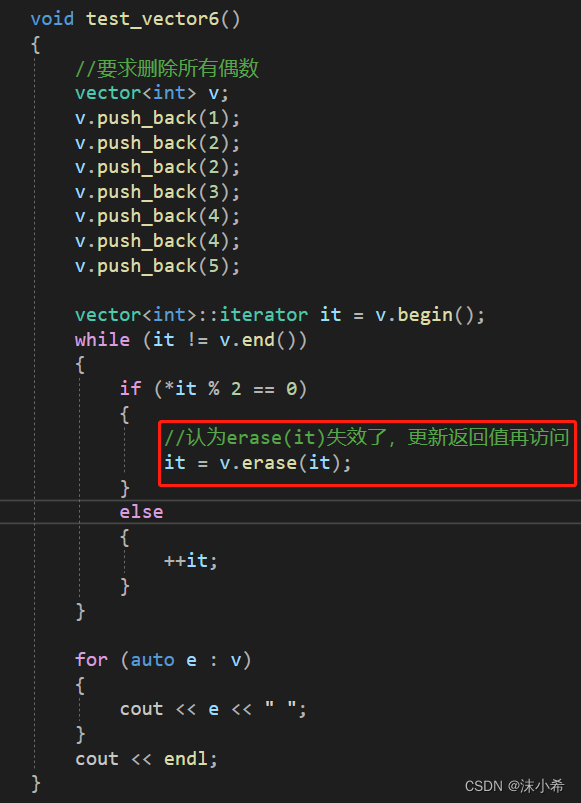

解决冲突的方法

设置 B U S Y ‾ \overline {BUSY} BUSY标志,采用仲裁逻辑,判断对哪个端口优先访问,而另一个被延迟的端口置BUSY标志为低电平,暂时关闭此端口,等到优先访问的端口完成访问,再进行复位

仲裁时根据两个端口的地址匹配或者片选使能信号有效时间决定对哪个端口进行存取

- 仲裁原则

- CE判断

如果地址匹配并且在 C E ‾ \overline{CE} CE之前有效,片上的控制逻辑在 C E L ‾ \overline{CE_L} CEL和 C E R ‾ \overline{CE_R} CER之间进行判断来选择端口

- 地址有效判断

如果 C E ‾ \overline{CE} CE在地址匹配之前先有效,片上的控制逻辑在左右地址间进行判断来选择端口

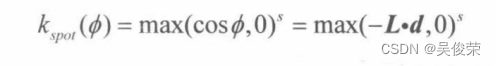

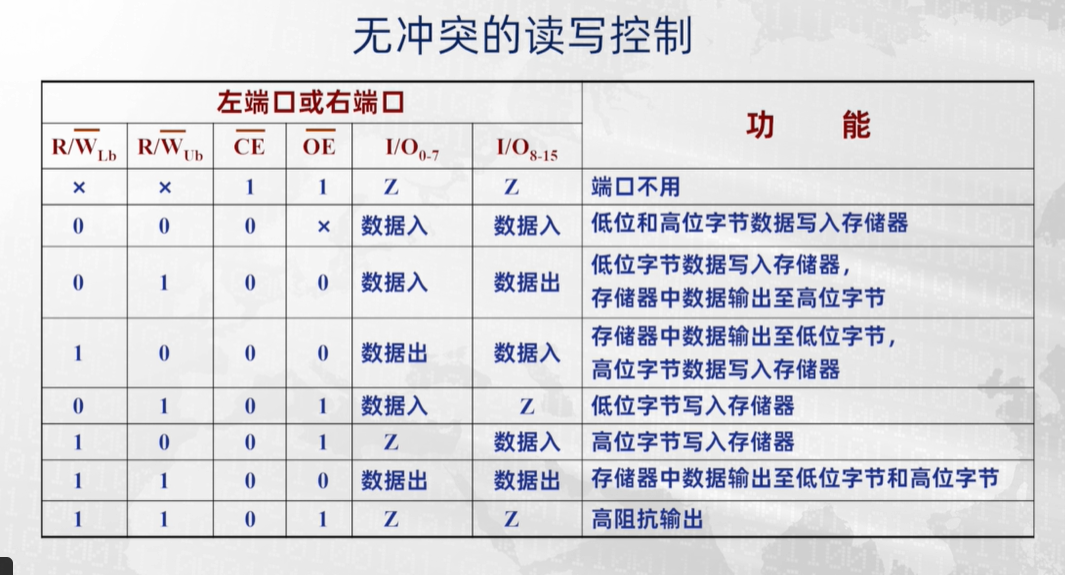

表中符号意义如下:

- LV5R:

左地址有效先于右地址50ns

- RV5L:

右地址有效先于左地址50ns

- 相同:

左右地址均在50ns内完成匹配

- LL5R:

左使能端有效先于右使能端有效50ns

- RL5L:

右使能端有效先于左使能端有效50ns

- LW5R:

左右使能端均在50ns内变为有效

在形同或者LW5R时,两边无法判断哪个优先,此时随机关闭一个端口,即设为BUSY,令两一个端口优先有效

多模块交叉存储器

双端口存储器采用的是空间并行技术,此多模块交叉存储器采用的是时间并行的技术

- 一个由若干模块组成的主存储器是线性编址的

- 地址在各模块有两种安排方式

- 顺序方式

- 交叉方式

顺序方式

- 每一个模块内的地址是连续的

- 高位地址选择不同的模块,地位地址指向模块内存储字

- 某个模块进行读取时其他模块不工作

- 某一模块出现故障时,其他模块可以照常工作

- 通过增添模块来扩充存储器容量比较方便

- 但是由于各模块串行工作,存储器的带宽受到了限制

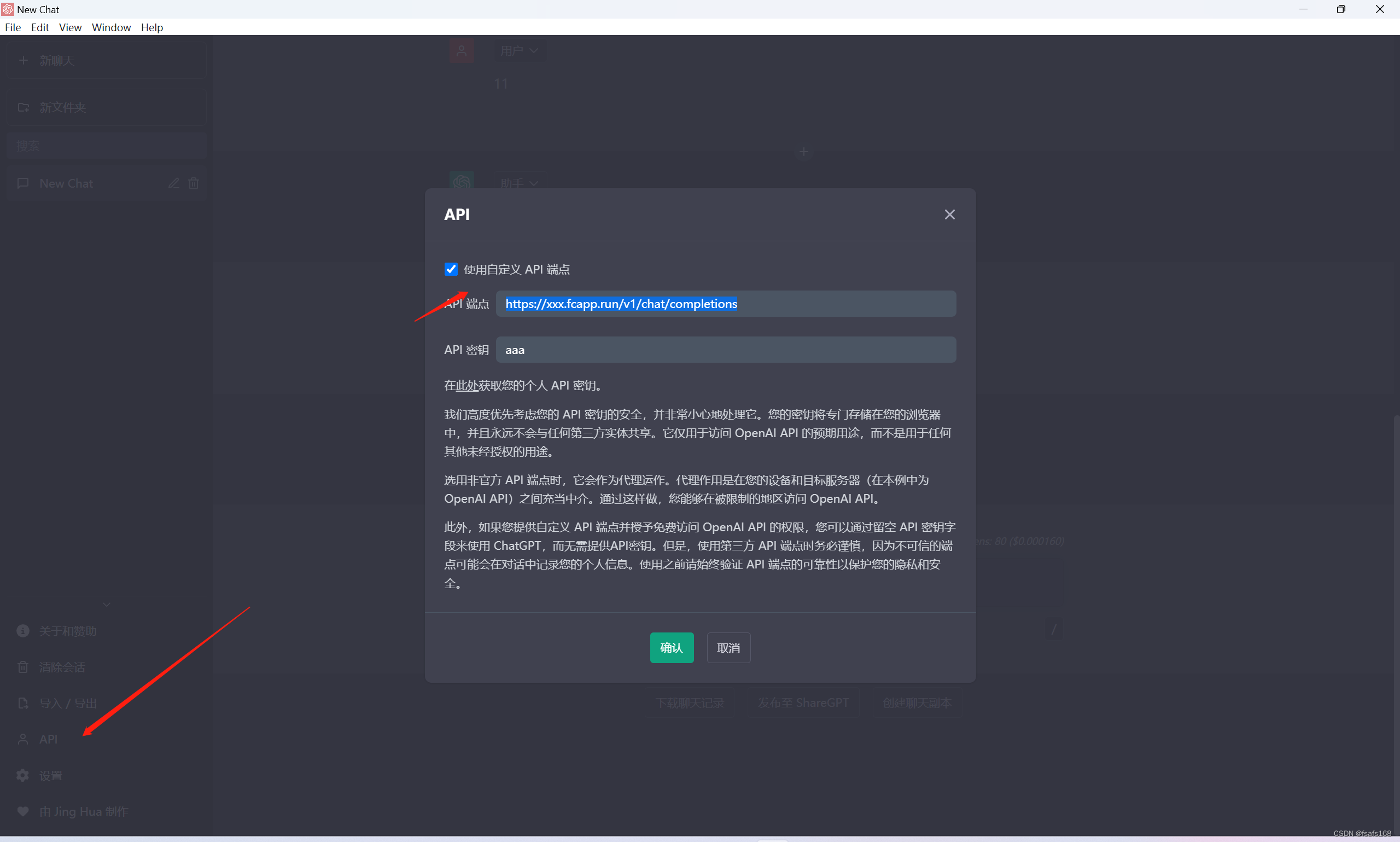

如图所示的顺序方式,内存地址使用五位即可以访问所有存储单元,存储器内分为四个模块,采用2-4译码的方式选择各个模块,即内存地址高二位进行模块选择,每一个模块有八个字,因此内存地址低三位用来选择对应的字

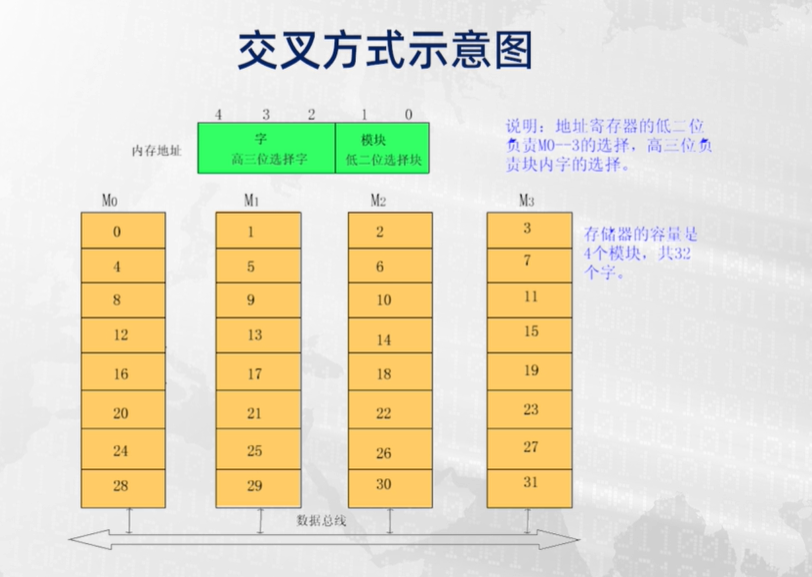

交叉方式

- 连续地址分布在相邻的不同模块内,同一个模块内的地址都是不连续的

- 地址码低字段通过译码选择不同的模块,而高位字段指向对应模块的存储字

- 连续字的成块传送可以实现多模块流水式并行存取,可以大大提高存储器的带宽

与顺序方式相反,内存地址的高三位选择对应字,而低二位选择对应模块

多模块交叉存储器的基本结构

- 每个模块各自以等同的方式与CPU传送信息

- CPU同时访问4个模块,由存储器控制部件控制它们分时使用数据总线进行信息传递

- 是一种并行存储器结构

在一个读写周期内,CPU连续访问4个模块

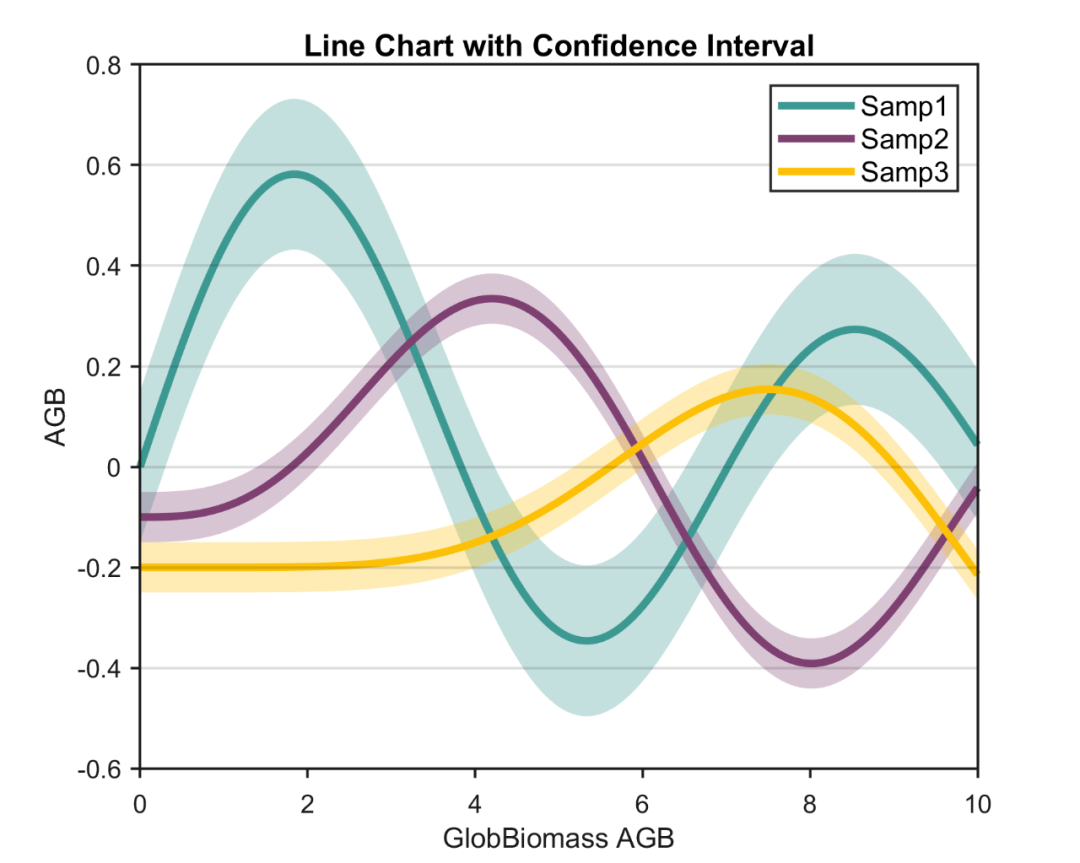

交叉存取度

-

设模块字长等于数据总线宽度,模块存取一个字的存储周期为T,总线传送周期为 τ \tau τ,存储器的交叉模块数位m,为了实现流水线存取,应当满足: T ≤ m τ T\leq m\tau T≤mτ

-

m的最小值称为交叉存取度: m m i n = T τ m_{min}=\frac{T}{\tau} mmin=τT

-

交叉方式连续存取x个字所需的时间为: t 1 = T + ( x − 1 ) τ t_1=T+(x-1)\tau t1=T+(x−1)τ

-

顺序方式连续读取x个字所需时间为: t 2 = m T t_2=mT t2=mT

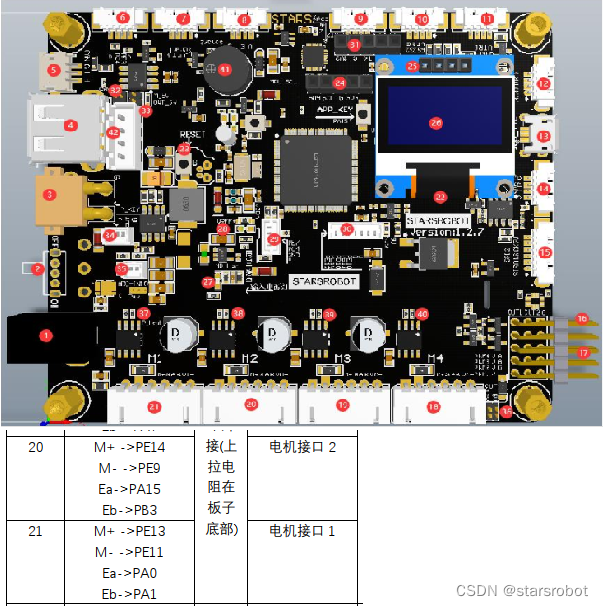

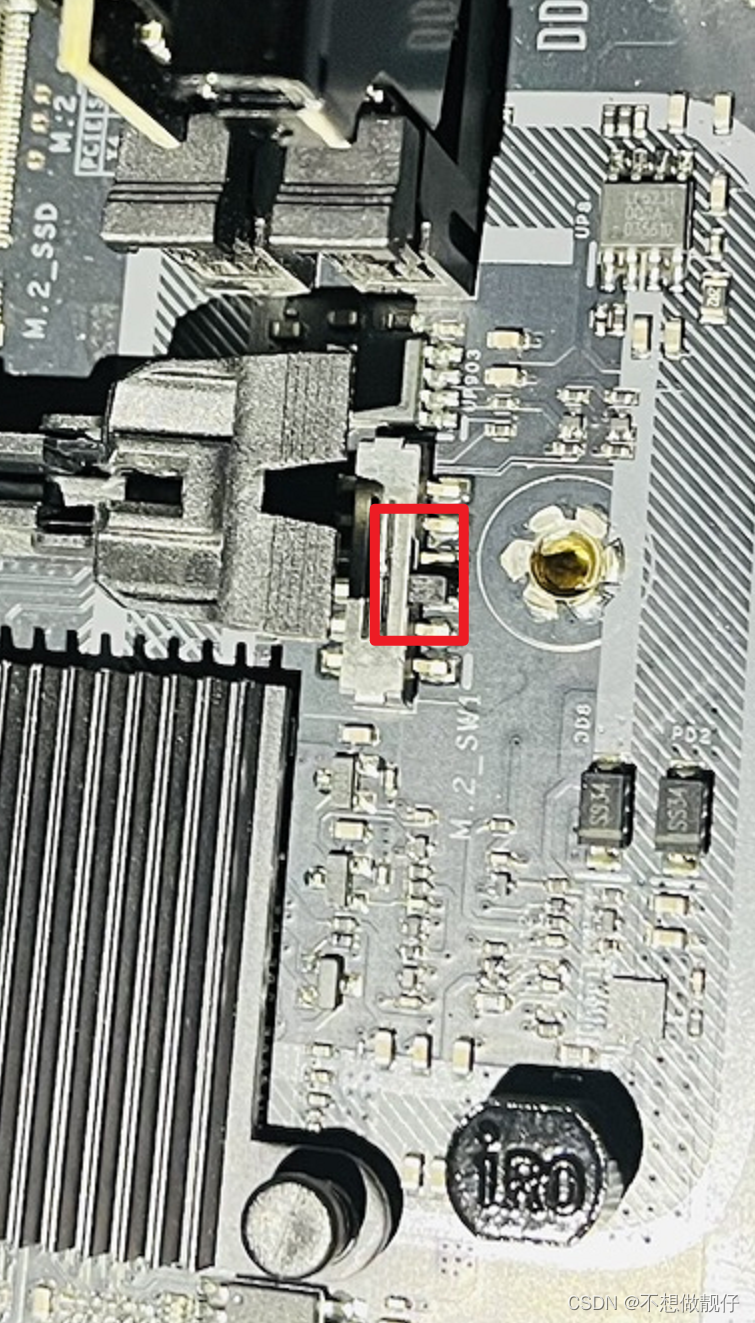

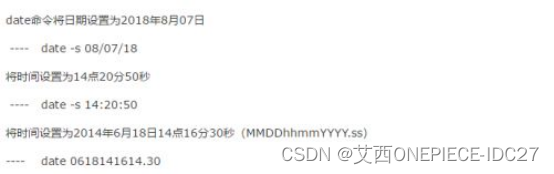

上图为一个二模块交叉存储器,通过内存地址的A2来选择模块,A1A0用EP3~EP0代替,用以控制读写等信号,中间为块内字地址,读写操作时分为行列地址两部分,头部A23~A21为存储体选择用以字扩展

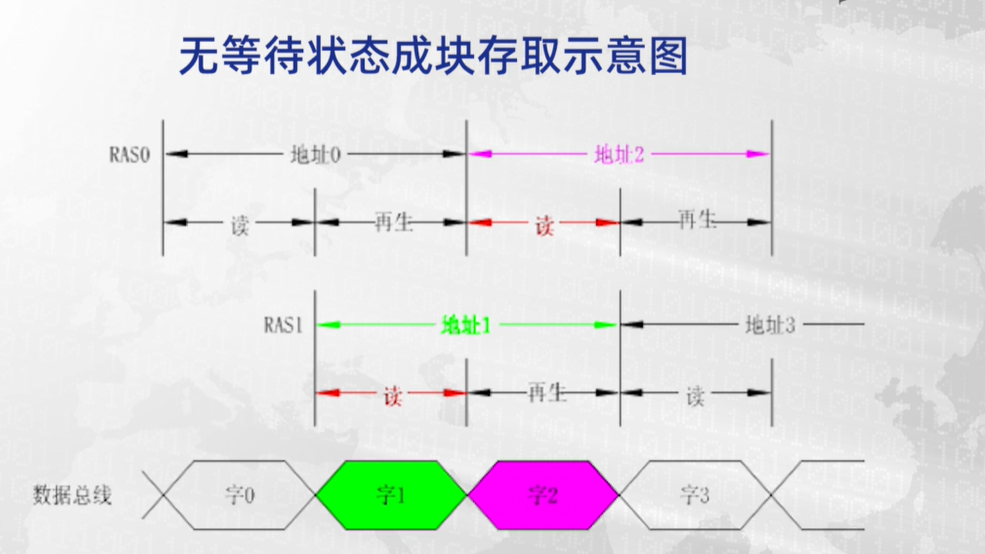

DRAM芯片的读出是一种破坏性读出,在读出后需要立即按照读出信息进行充电再生,若CPU先后两次读取的存储字使用同一个RAS*选通信号,CPU在接收到第一个存储字后必须插入等待状态,直到前一个字再生完毕后才能够开启第二个存储字的读取,而使用二模块交叉存储器,在两个字的读取之间就不必插入等待状态,因为在一个模块的等待状态时使用另外一个模块

上图为零等待成块访问的示意图