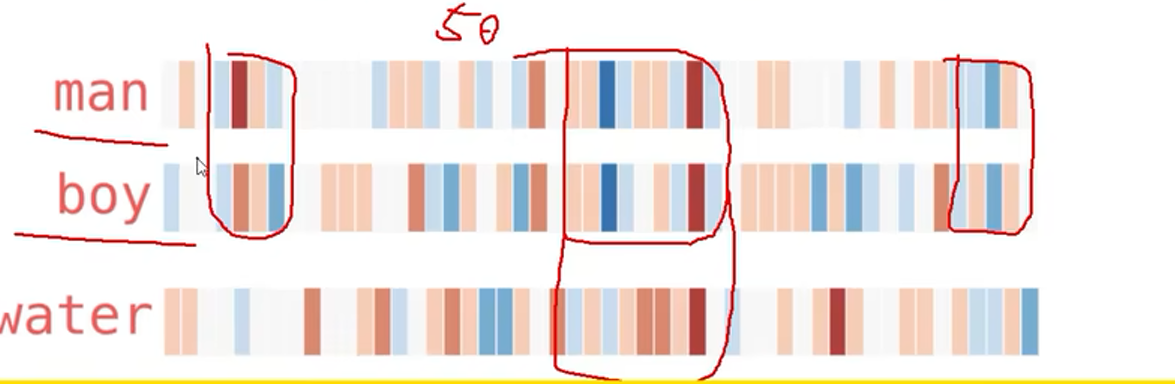

Latch比较器Noise仿真

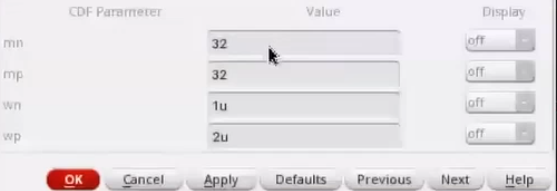

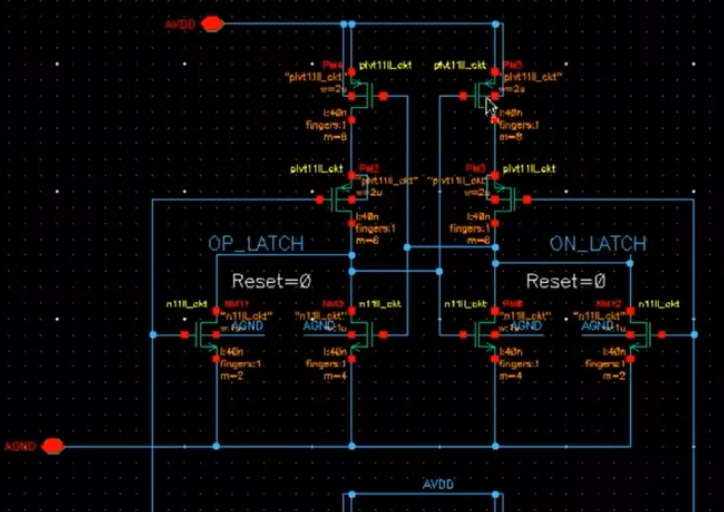

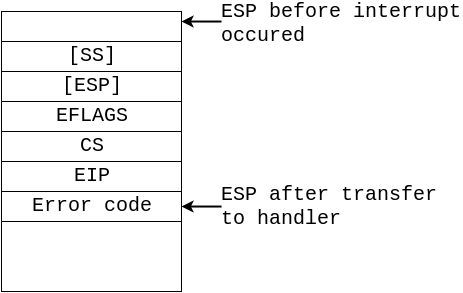

比较器后面加RS触发器,当比较器复位时,OUTP和OUTN输出为11,RS触发器锁存;当比较器比较时,OUTP和OUTN输出一正一负,RS触发器相当于反相器。

做法:改变Vin的值,测输出。当offset VN = 1sigma时,输出OUTP的值为1或者0的平均概率为0.841或者0.159(0.5+0.341 or 0.5-0.341)。当offset为0时,输出无论OUTP还是OUTN为1或者为0的几率都为0.5。

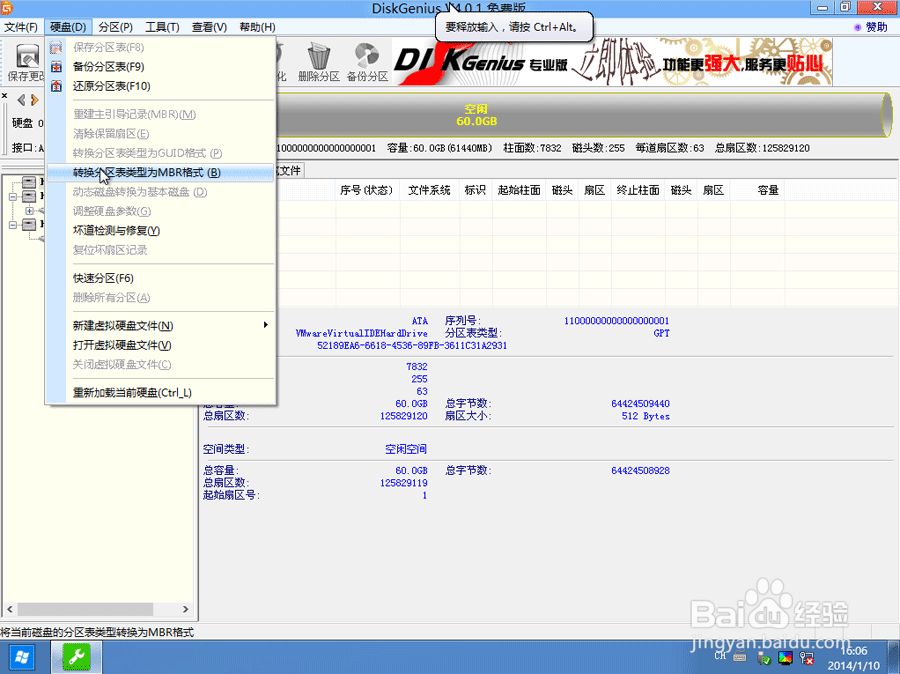

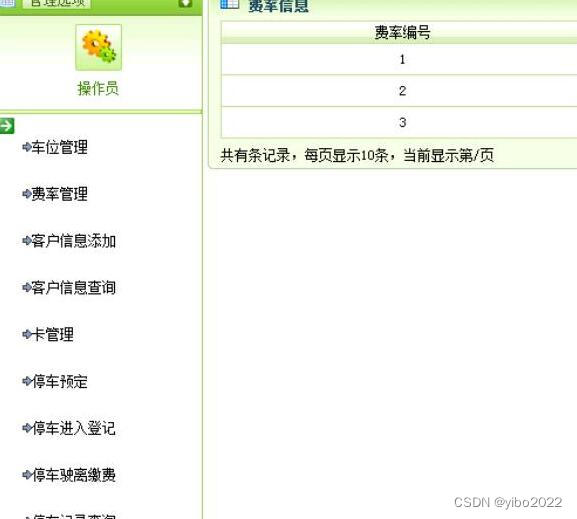

SAR ADC debug思路:

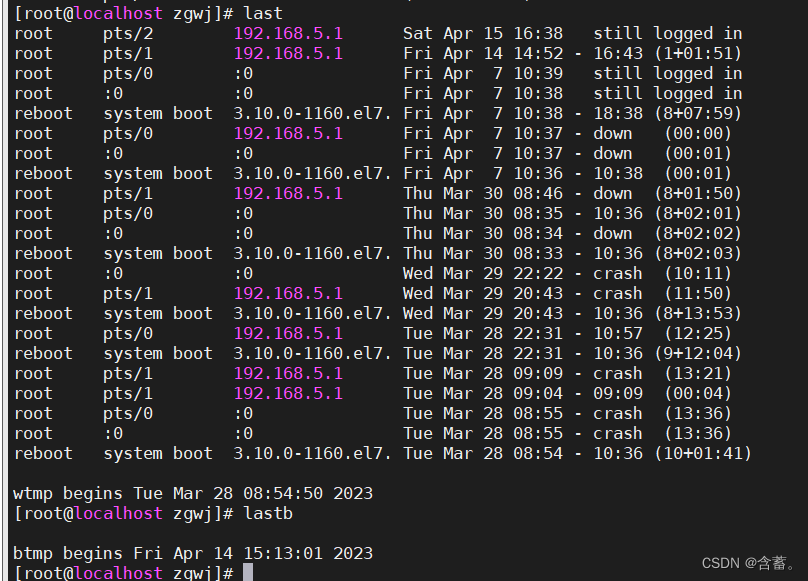

step1:Latch、Valid高速异步时钟是否正常?

速度够不够,波形丑不丑。Valid驱动触发器较多,波形比Latch信号丑。强迫症选手可以把上升沿做到10ps、5ps以内。

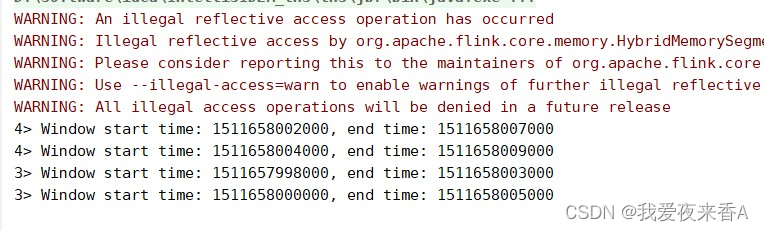

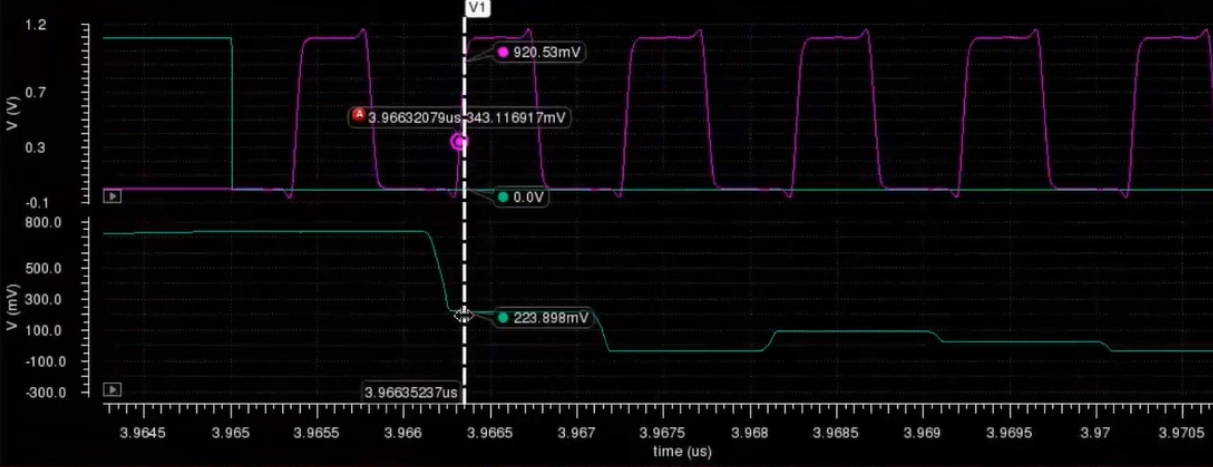

step2:看DACP和DACN是否收敛?

可以量一下,看每一次跳变多少电压,每次跳对应的权重,二进制每次跳上一次的一半。看每次抓的值是在什么位置,CDAC有没有建立好,没有建立好的话,要加冗余!比到最后,有几个mV的误差正常,不是每次都是收敛到0的,这就是量化噪声。下图输出是差分信号。

step3:看看CDAC共模是否合理

step4:看各点驱动性能是否足够导致波形变形?

像这个直接给了32个反相器驱动MSB,可能导致reference建立较慢。从而CDAC建立也慢。MSB电容为x*Cu,可以初步计算一下,一个buffer驱动几个Cu,这样后面版图也好画。而MSB最大,CDAC建立时间也需要最长。前面的D触发器有4个inv驱动32个inv的buffer,相当于一个inv驱动8个inv,有点吃力,导致MSB的reference建立时间也较长。

综上,高几位建立时间慢,所以要加冗余,冗余辅助高位的。

加了冗余之后,12位转10位要加法器实现,不用做乘法器,数字乘法器太复杂,浪费速度。做加法器,半加器全加器,要考虑进位的。

比较器

李维斯格雷改进型,噪声性能好,但是速度慢,(strong arm)叠的管子越多,越慢。

两级动态latch

校准latch offset,看另一个笔记。

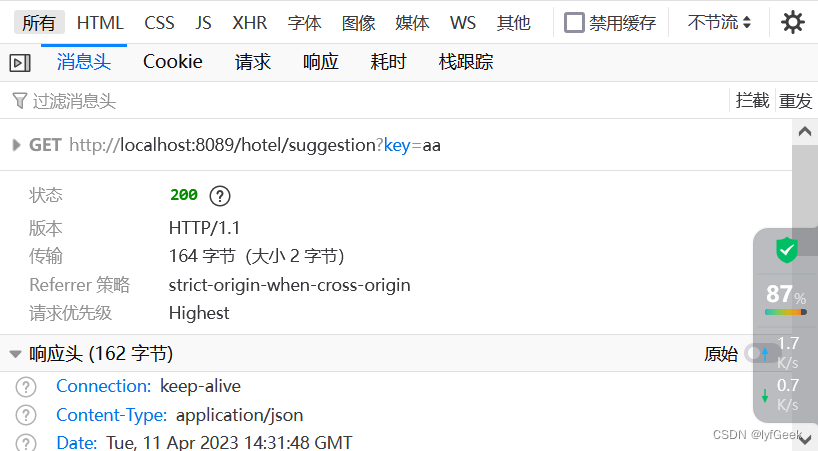

Reference Buffer

可以一个LDO,从高压往下降,自己做reference,做电源地,偷一点电源电压,比方说0.8V的供电,偷0.85V,这样速度能做快,想要性能极限,就要各种偷。可以做一个模块,检测PVT corner,类似一个PVT sensor,检测到ss,电源电压就往上抬一点,检测到ff,电源电压就往下降一点。LDO可以弄个3bit来控制,有8个档位。因为ss和ff corner下latch的速度差的蛮多的(3倍都有可能)。监测温度,监测电源电压。用环振监测,几十个inv构成环振,环振低了就提高电压,或者更改latch环路延迟,如果环振检测到偏向ff了,可以在latch环路里面插几个反相器增加延时啊。用一个低位的adc控制环路延迟。

smic40ll,70~80M比较靠谱,再大就要偷电源电压,或者用LVT器件了。

reference buffer 一般两种思路,一是片上退耦电容,用Vdd,二是做片上有源buffer。做退欧电容的话,可能CDAC抽电流的时候,可以人为在退欧电容上pump进电荷补偿。

比较的越快,CDAC变化的越快,对reference要求越高,要快速的对CDAC进行充放电,让CDAC能够快速建立。

速度降下来,enob性能可以上去,比较器加Pre-AMP嘛,增加一些静态功耗,把比较器噪声压下去。高速异步SARADC的位数上不去,主要就是高速比较器的噪声限制。

Cadence做DFT算ENOB有两种方法,一个是公式算,另一个是spectrum算,或者导出Matlab算

![]()

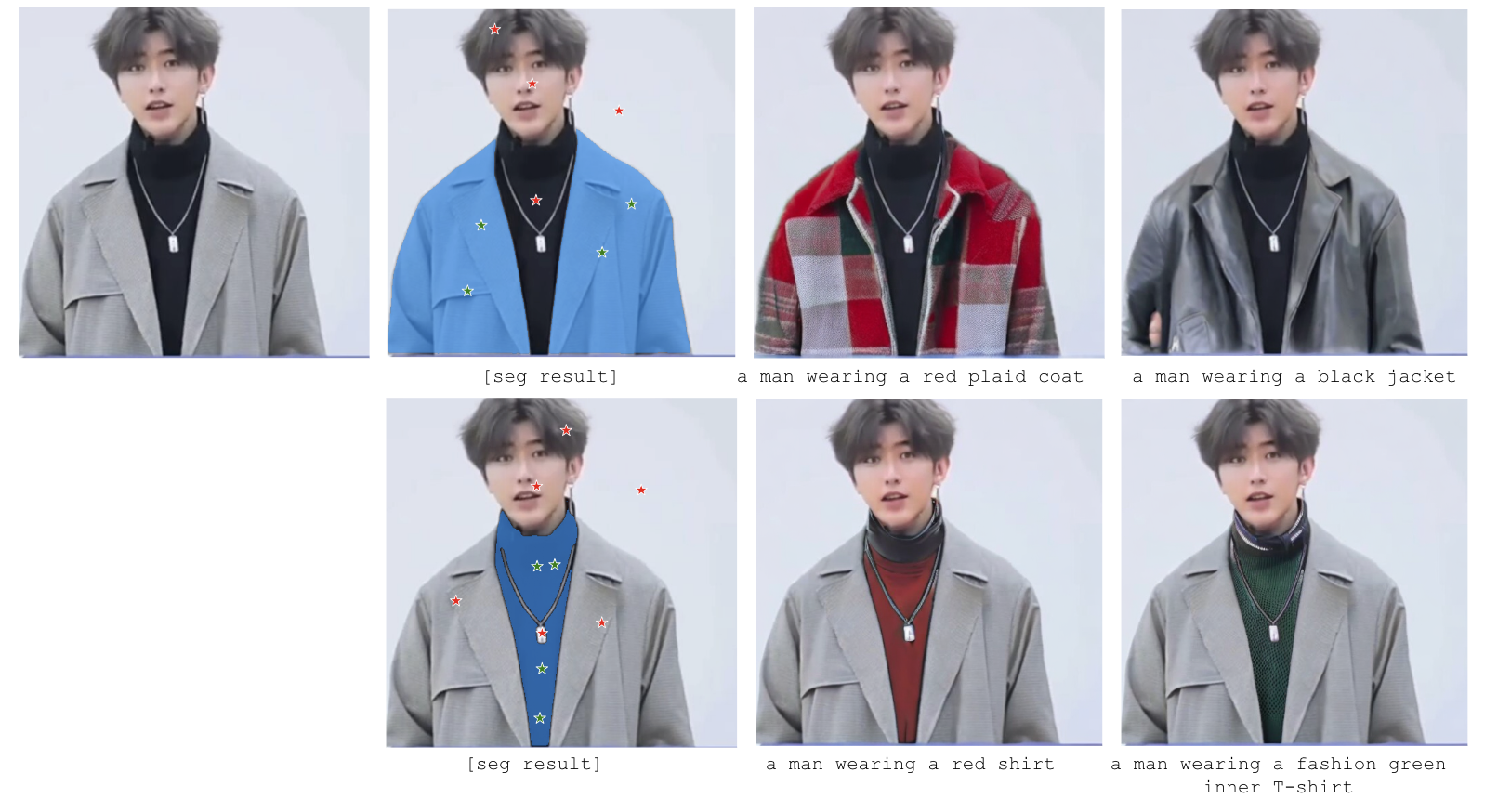

高精度sar:数字校准(一般是校准CDAC);NS噪声整形加滤波(改善比较器);多次测量取平均值。

限制精度主要就是mismatch,高速latch的噪声。想办法消除掉。

NS+pipeline+sar+数字校准,想做高速度再加上TI,多通道?

![[chapter 26][PyTorch][MNIST 测试实战】](https://img-blog.csdnimg.cn/07d671ba222e47e4b7e7524d6991f9a1.png)