目录

串一下知识点:

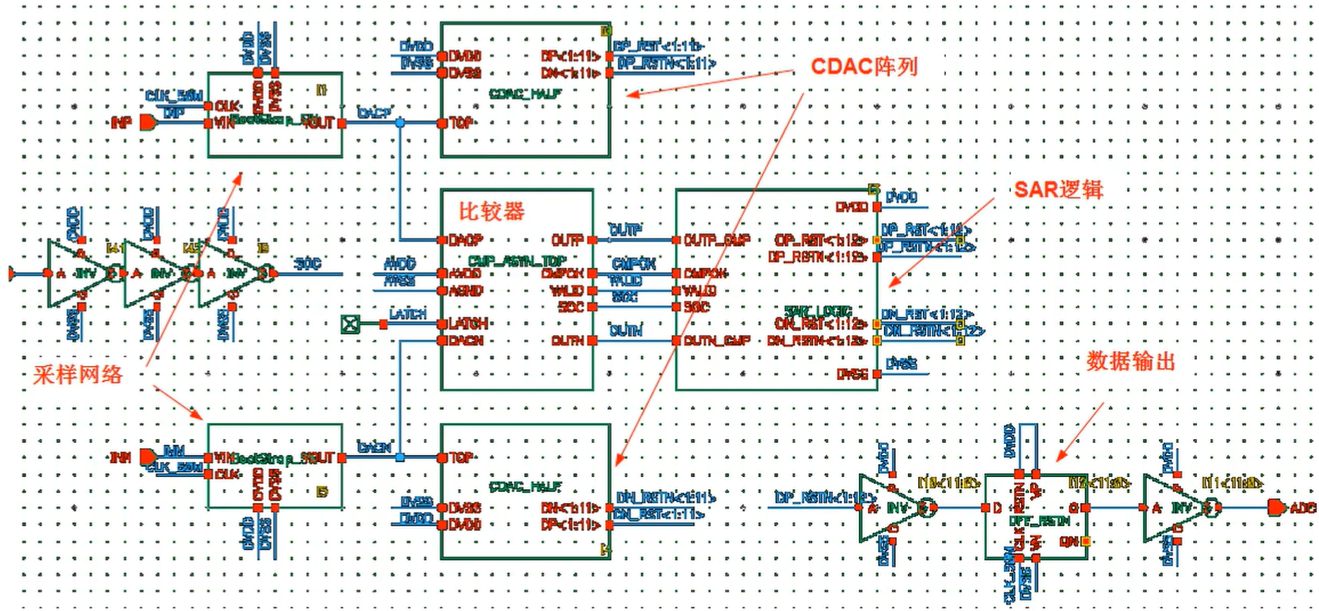

设计一个高速异步SAR ADC

设计目标:

电路架构:(具体电路看前文)

采样网络:

采样电容:

CDAC开关切换策略:

CDAC阵列冗余设计:

SAR 逻辑

比较器方案:

串一下知识点:

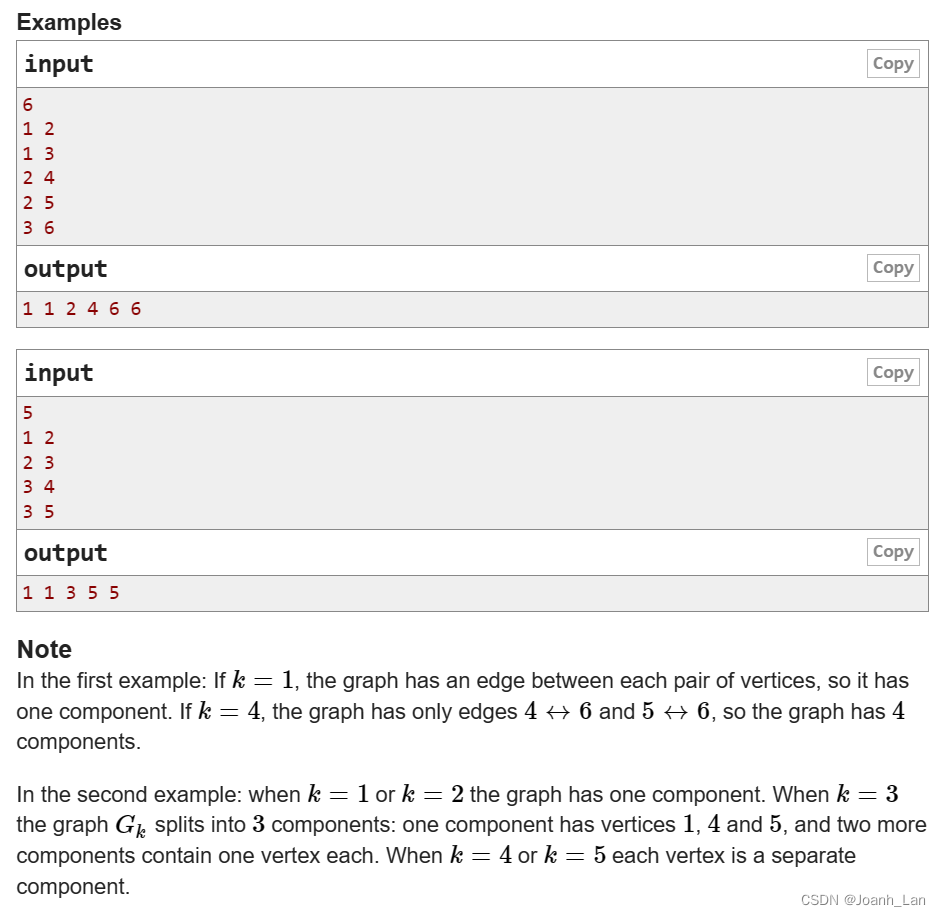

第一章:DFT。每一个做信号链的都应该会懂DFT,怎么仿真,怎么分析,每一根谱线的物理含义这些,每一根谱线都是有来头的,怎么计算得到的。后面引入的相干采样的概念。

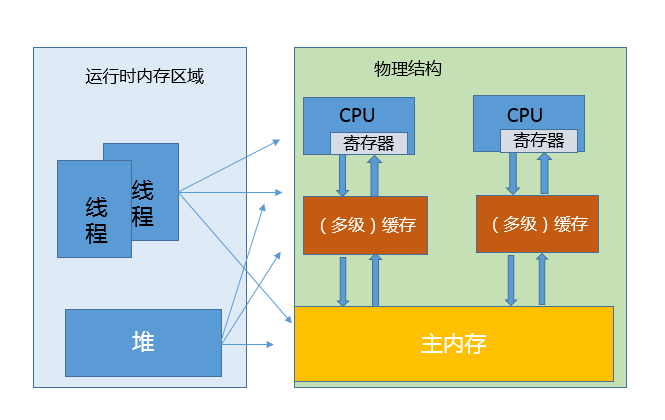

第二章:采样网络。上级板采样和下级板采样的优缺点。上级板:简单,和CDAC配合好;但是精度不高,主要体现在沟道电荷和时钟馈通,虽然全差分可以消掉一写,但是消不完全。下级板采样精度高,像开关电容,pipeline ADC很多都采用下级板采样的,有源S/H。然后介绍的一个相当重要的知识点:电荷守恒。见到开关电容就找电荷守恒,找初态终态,这样就不会晕,因为有时中间挺麻烦的。

第三章:CDAC网络。电容的随机失配,可以扩展到电阻、MOS管等所有遵循随机失配高斯分布的器件。数据统计的方法,1sigma什么意义。CDAC开关切换策略,和采样网络的搭配。

第四章:比较器。低速sar ADC的静态Pre-AMP+Latch,失调消除方法OOS、IOS。高速sarADC的Latch比较器。分析方法:将latch拆成好几个等效的放大器,逐个分析每个管子的等效输入offset。可以类推noise的分析。

第五章:sar逻辑。高速异步sar逻辑,和冗余。高速sar逻辑不要被唬住,没什么。主要是冗余,冗余的思想很重要,不光在异步sarADC中。同步sar,pipeline都有。

设计一个高速异步SAR ADC

设计目标:

位数:10bit,采样速率:50MSPS,工艺:SMIC40LL(Low Leakage),电压:1.1V,Vref:电源/地

电路架构:(具体电路看前文)

采样网络:

● 上极板采样:

■ 优点:结构简单

■ 缺点:会引入与信号相关的失真,采样精度有限,一般不超过10Bt精度

●下极板采样:

■ 优点:线性度高,采样精度可以很高

■ 缺点:结构复杂,采样之后的复位动作消耗较大能耗

● 最终方案:上极板采样

采样电容:

● 噪声约束电容:

■ 单端采样网络的噪声:KT/C(是电阻的噪声,只是噪声能用电容表示,数值和电阻无关)

■ 全差分采样网络的噪声:2*KT/C

■ 1pF电容对应的 KT/C 为 ~64uV (典型值可以记下来)

● 匹配约束电容:

■ MSB (~采样电容的一半) 为CDAC线性度的瓶颈

■ 电容越大,匹配越好;电容X4,匹配提升1倍

● 最终方案:自定义mom电容,采样电容(~1pF)

pdk电容单位电容太大,mismatch不可控。定制电容,单位电容可以做的很小,可以区分上下级板,保护好上级板。实际上,我们不是怕寄生,而是怕不知道寄生到哪里去了,用金属包起来,寄生可控,我知道寄生在哪,是什么样的,在设计的时候就能考虑进去。

CDAC开关切换策略:

● 单调开关切换策略:

■ 开始转换时比较器输入共模=AVDD/2,转换过程中比较器输入共模不断降低(或者升高)

■ 比较器输入共模过低会影响Latch比较器的速度、甚至功能。(latch对小信号放大能力较弱,甚至会出现亚稳态,比较时间过长影响到后面的功能,也可能Vcm过低使得比较器不工作了)(看前文latch分析)

● 基于Vcm的开关切换策略:

■ 需要引入一个中间电平VCM=AVDD/2

■ 在先进工艺下,AVDD/2附近的开关不容易实现

● 最终开关切换方案:

■ 采用基于VCM的开关切换策略

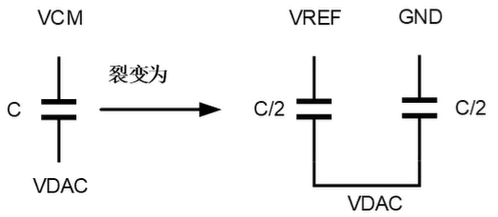

■ 采用“电容分裂”技术将一个下极板接到VCM的电容拆分成2个电容

■ 2个分裂电容的下极板分别接到VREF和GND

注意:VDD和GND要加非常大的退耦电容。

CDAC阵列冗余设计:

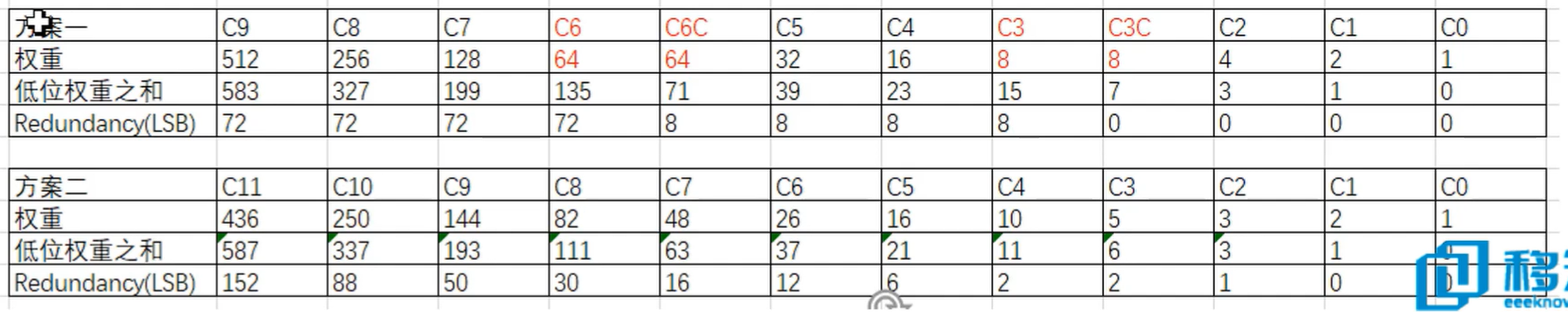

● 方案一:间隔插入Redundancy

■ 512/256/128/64/64/32/16/8/8/4/2/1

■ 通过观察可得前4次比较拥有相等的冗余量(容错量),为 72LSB;接下来3次比较冗余量为8LSB;最后4次比较不能错

● 方案二:Redundancy逐渐减小

■ 436/250/144/82/48/26/16/10/5/3/2/1

■ 通过观察可得冗余量逐渐减小,看起来分布更加合理

为什么MSB要冗余量留最大呢:因为,MSB电容最大,刚采样完成,Vref建立可能来不及,CDAC又是基于Vref建立的,而且CDAC建立也需要时间,因此会导致比较器判错。再加上Vref buffer上的噪声,比较器噪声等等。

SAR 逻辑

● 异步逻辑:

■ 避免外灌高速时钟:高速时钟工作频率接近GHz

■ 根据每一次比较所花费的时间自动划分比较周期,可以避免时间的浪费,提升转换速率

比较器方案:

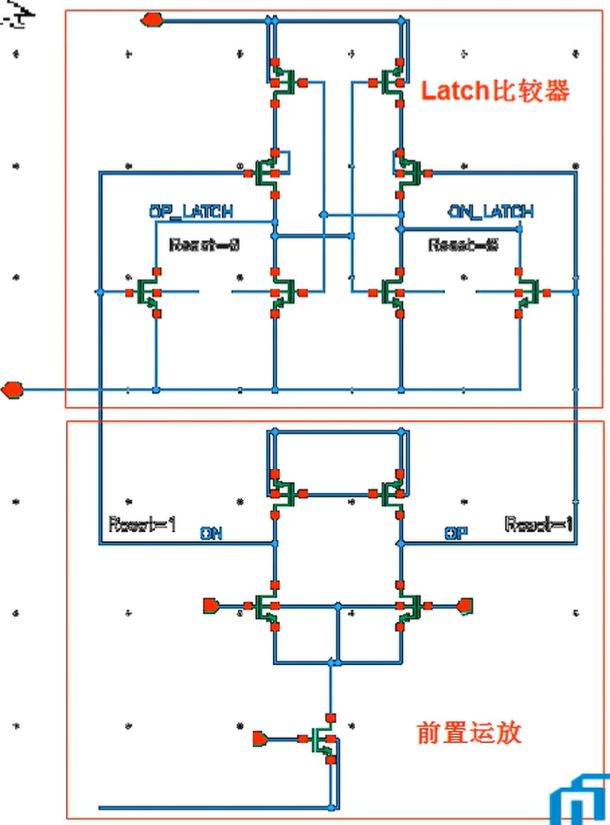

● 传统的Pre-AMP+Latch方案:

■ 需要静态功耗,不利于低功耗设计

■ Pre-AMP的 “复位” 难度较大,影响比较器速度

● 动态Latch比较器方案

■ 0静态功耗

■ 可以考虑加入动态Pre-AMP以提升Latch性能

关键电路设计:

采样开关:

● 需要注意的点:

■ 采样NMOS衬偏消除,以提高线性度

■ PMOS衬底的正确接法

■ PUMP电容的取值(相比寄生要足够大)

■ PUMP电容的上下极板的区分

■ PUMP电容可以用MOS电容实现

● 导通电阻的设计:

■ 采样时间:取50MHz的1/4,为5ns

■ 采样开关建立时间:>10*tao,tao<0.5ns

■ 采样电容:C=1pF

■ 采样电阻Ron=tao/C < 0.5ns/1pF = 500欧姆(所有corner)

CDAC网络:

● 需要注意的点:

■ 不同权重的电容下极板的驱动能力的匹配。

■ 尽量标准化设计,“某个单元”的复制,“某个单元”不仅仅包括电容,也包括驱动电路。

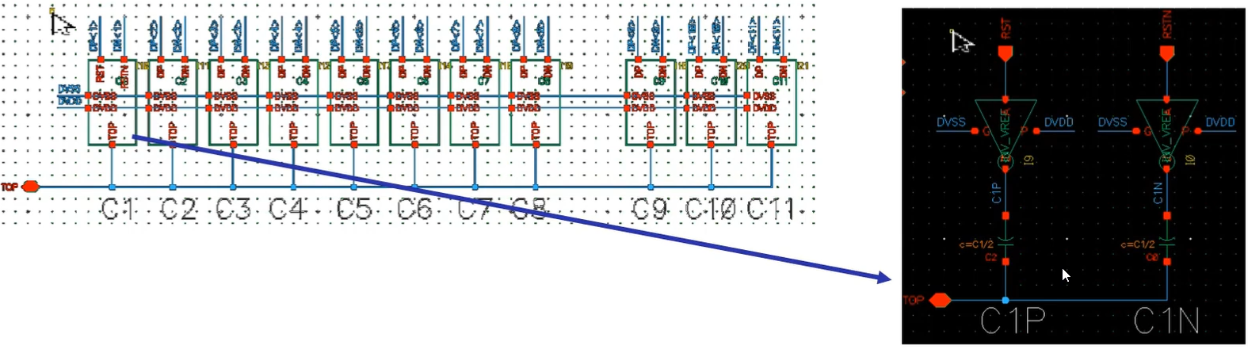

■ 10位ADC,全差分需要9个电容,做两个冗余位,总共11个电容。

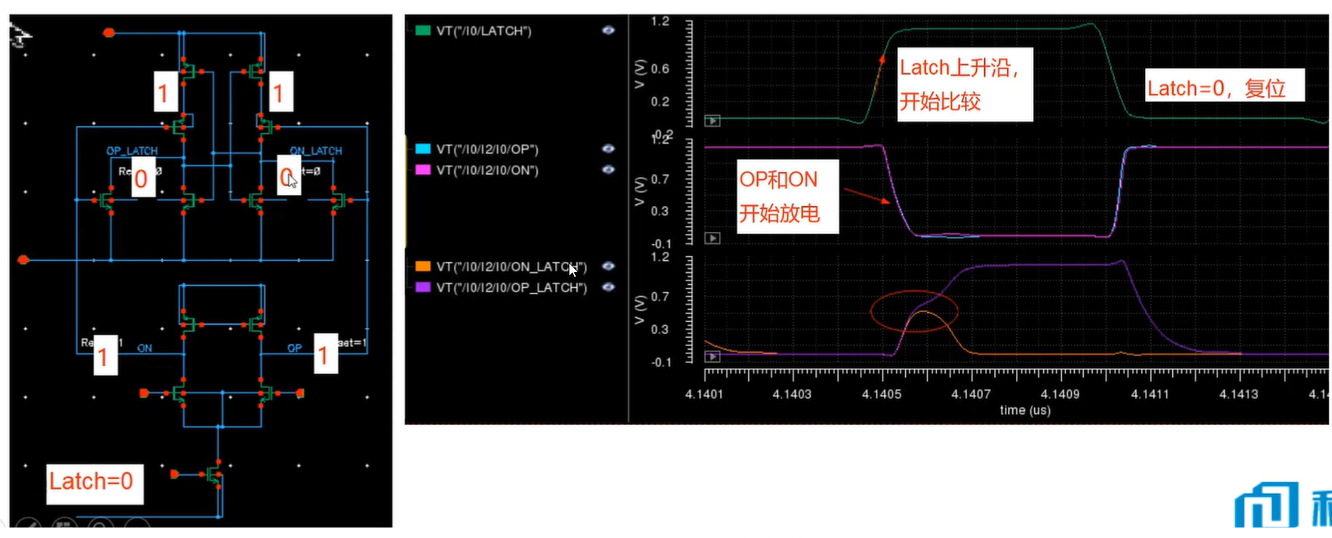

Latch比较器:

Latch = 0 ,比较器复位至0;Latch = 1 , 比较器开始比较

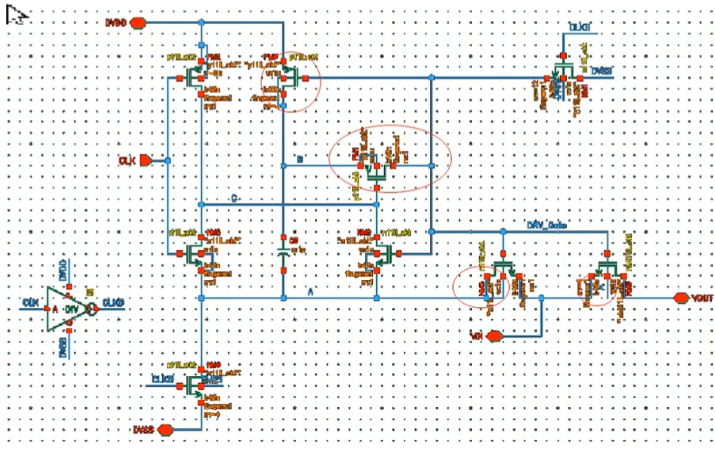

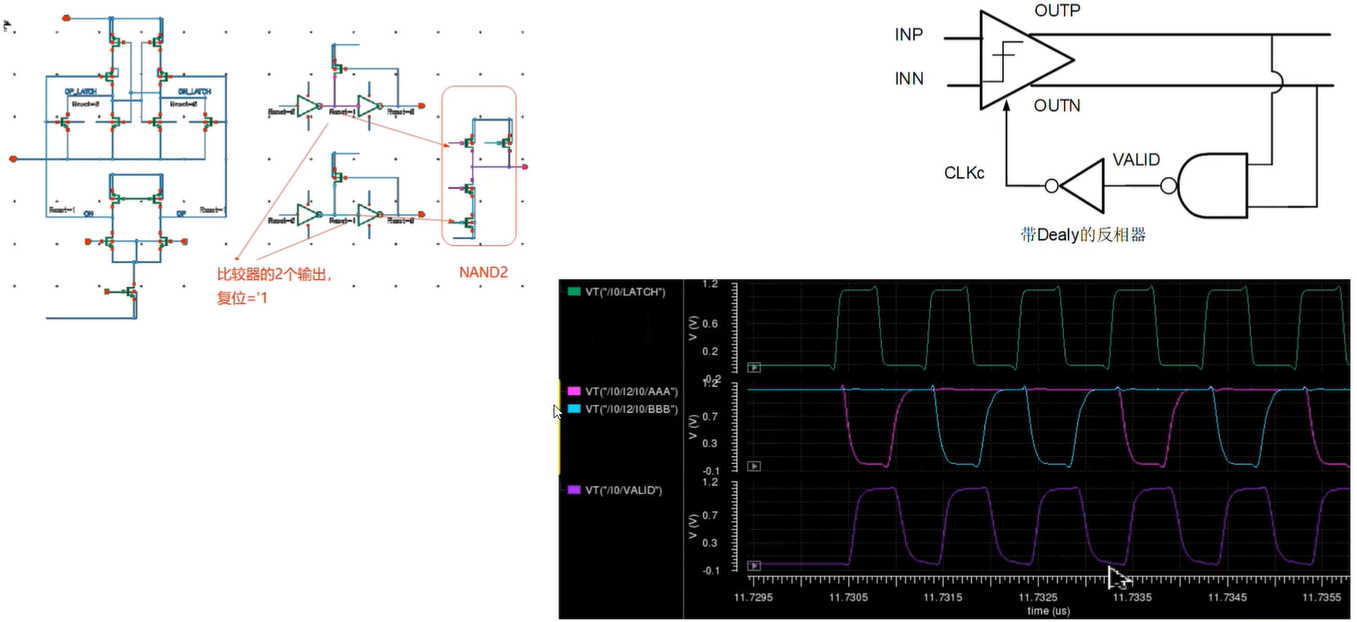

异步sar逻辑:Valid产生

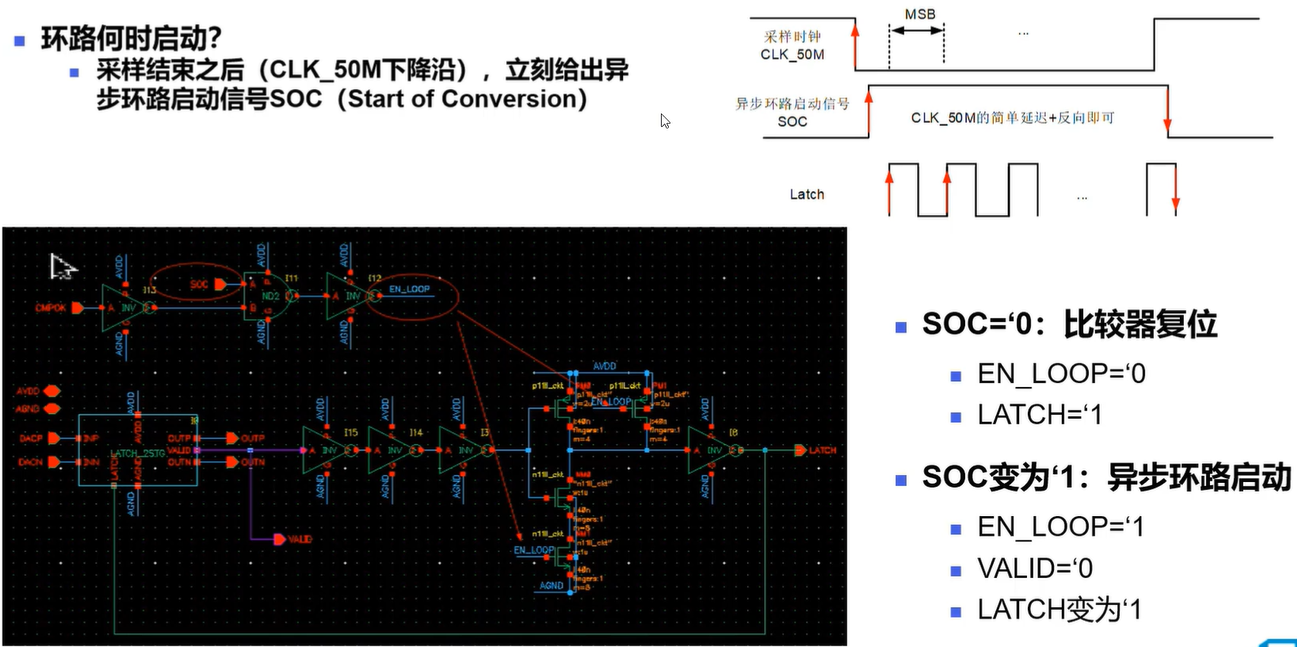

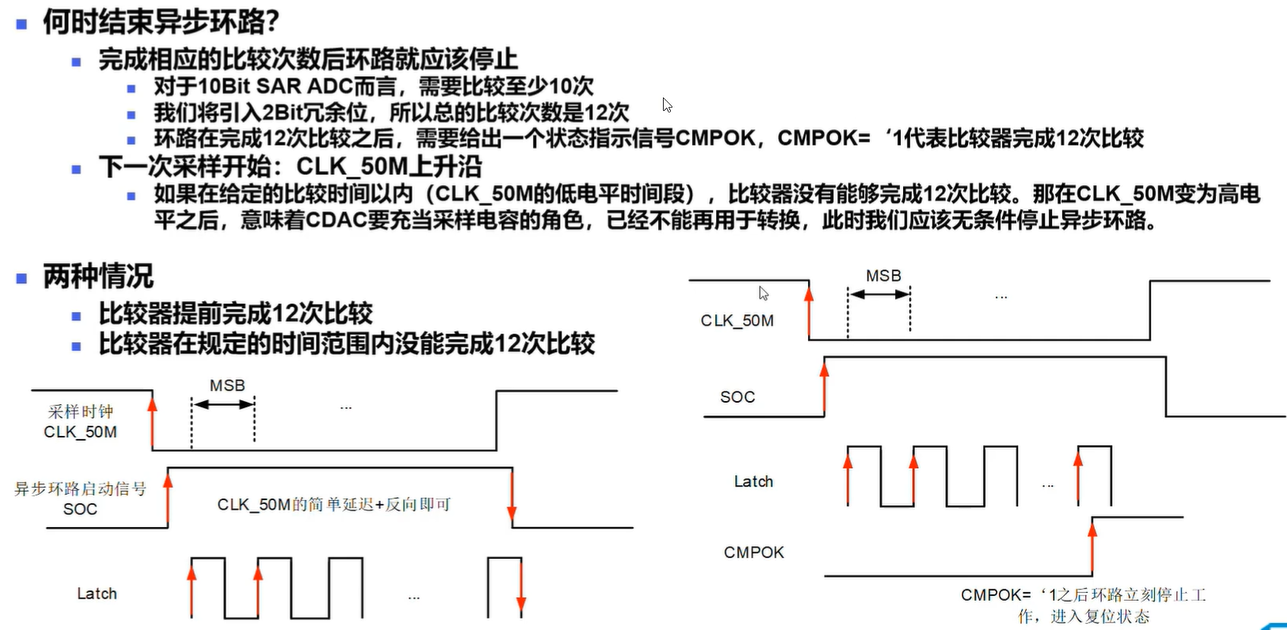

异步sar环路:环路启动和结束

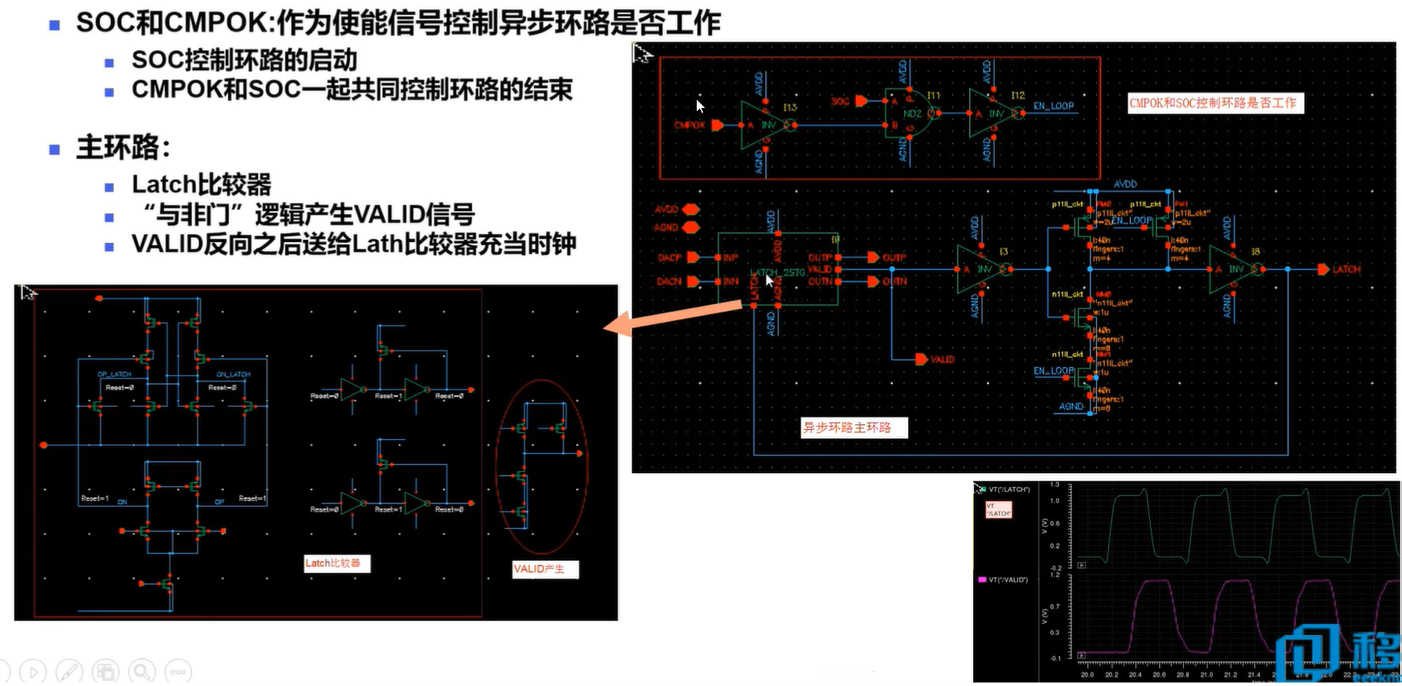

异步sar环路:电路实现

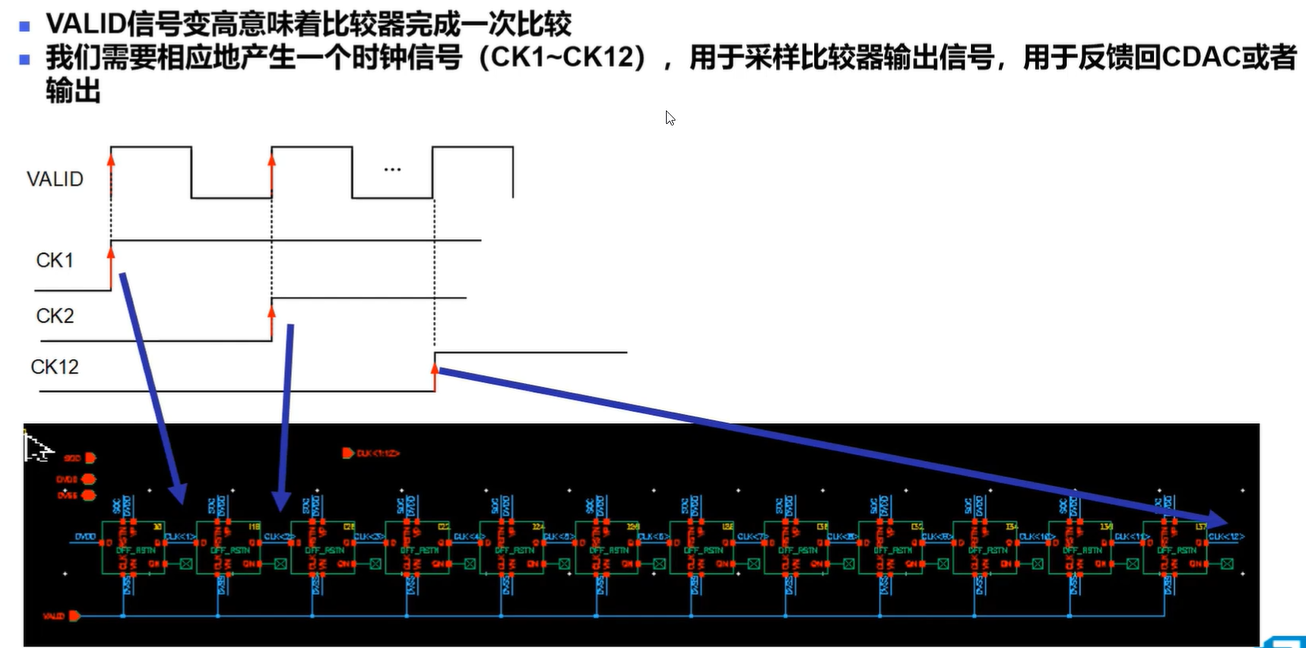

异步sar逻辑:CK1~CK12的产生

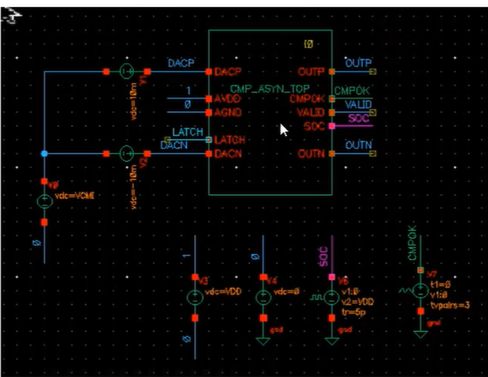

电路仿真

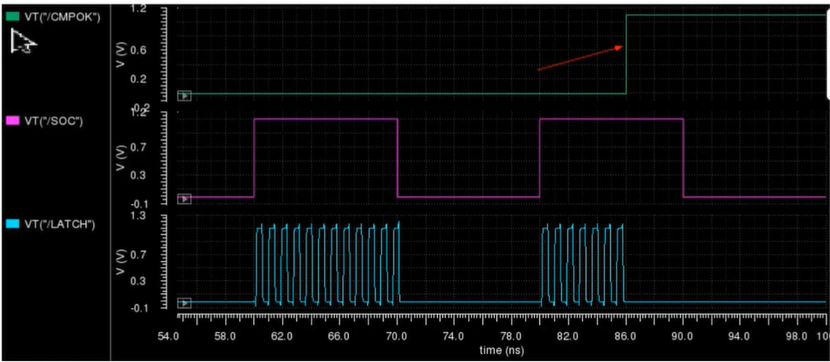

异步逻辑的仿真

关注以下几个点:

SOC对异步环路的控制

CMPOK对异步环路的控制

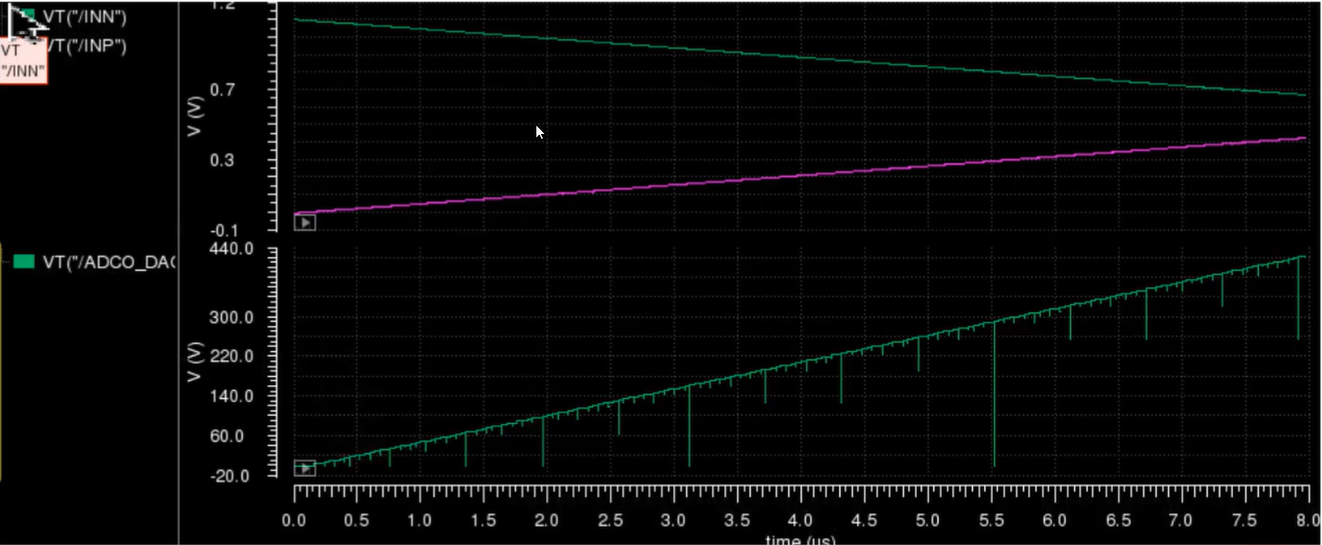

功能性仿真:Ramp输入

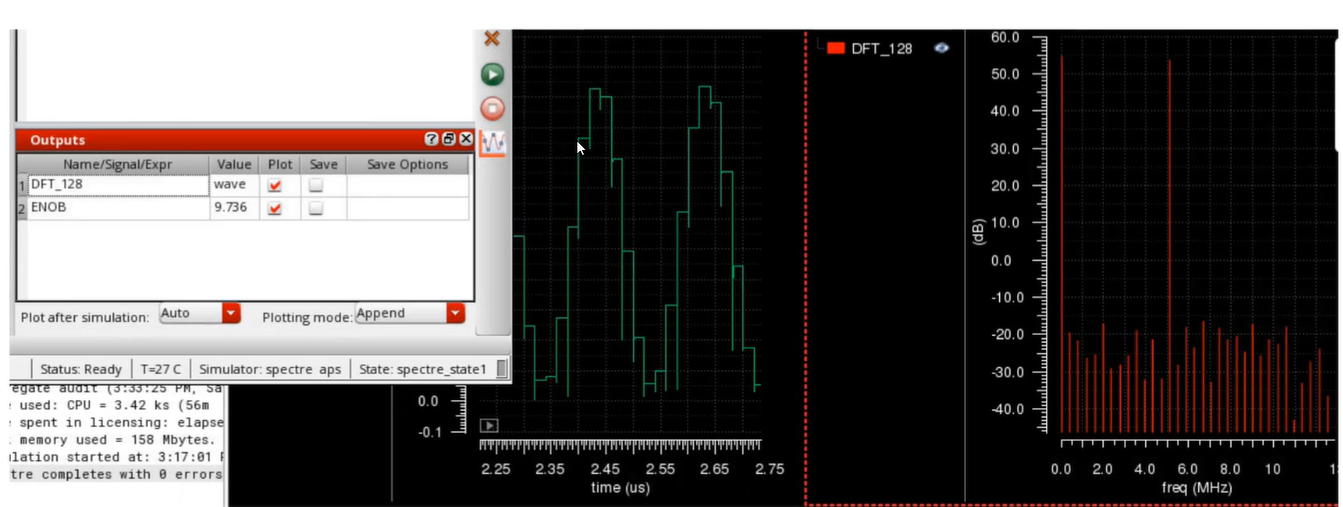

性能仿真:sin输入

性能仿真:CDAC建立情况