1.6.1 时间、产量和大众化的影响

即便没有技术进步,计算机组件的制造成本也会随着时间的推移而降低。这背后有着学习曲线的因素。

【学习曲线(from百度)】

学习曲线的定义为"在一定时间内获得的技能或知识的速率",又称练习曲线(practice curves)。

人们为了知道学习进程中的现象和进步的快慢的详情,作为以后努力的指针,应用统计图的方法作一条线,把它表示出来。它源于“二战”时期的飞机工业,当产量上升时,生产每架飞机的劳动时间会极大地下降。随后的研究表明,在许多行业都存在这种现象。学习曲线体现了熟能生巧。

学习曲线本身是根据**良率(yield)**的变化测得的,所谓良率是指成功通过测试的器件占所生产器件总数的百分比。无论是芯片、主板还是系统,使良率翻倍的设计就能使成本减半。

了解学习曲线如何提高良率,对于在一件产品生存周期的不同阶段控制成本非常重要。比如,长期以来,每兆字节DRAM的价格一直在下降。由于DRAM的定价往往与成本密切相关(出现供给不足或过度供给的时期除外),所以DRAM的价格与成本变化趋势基本一致微处理器的价格也随时间的推移而降低,但由于它们的标准化程度弱于DRAM,所以价格与成本之间的关系更复杂一些。当竞争非常激烈时,价格往往与成本密切相关,尽管微处理器供应商很少亏本销售。

产量是决定成本的第二个重要因素。产量的提高会从几个方面影响成本。第一,产量的提高减少了完成学习曲线所需的时间,该时间在一定程度上与系统(或芯片)的制造数量成正比。第二,产量的增加会提高购买与制造效率,所以会降低成本)一些设计人员根据经验估计,产量每增加一倍,成本会下降大约1%。此外,产量的增加还降低了分摊到每台计算机上的开发成本,在保持盈利的同时让成本与价格更为接近。

大众化商品(commodity)是指有多家供应商大量出售且基本相同的产品。杂货商店货架上的几乎所有产品都是大众化商品,标准的DRAM、闪存、磁盘、监视器和键盘也都是大众化商品。在过去30年里,个人计算机行业的很大一部分已经变成一项大众化商品业务,主要生产运行Microsoft Windows操作系统的台式计算机和笔记本计算机。

因为许多供应商提供几乎完全相同的产品,所以市场竞争非常激烈。当然,这种竞争会缩小成本与售价之间的距离,而且会降低成本。大众化商品的产量很高,又有明确的产品定义,这让多个供应商在为大众化产品构建组件方面展开竞争,从而降低成本。因此,由于组件供应商之间的竞争,以及供应商所能达到的产量效率,产品的总成本降低了。这种竞争导致低端计算机业务能够获得比其他细分领域更高的性价比,并在低端产生了更大的增长,尽管利润非常有限(对于所有大众化商品业务,通常都是如此)。

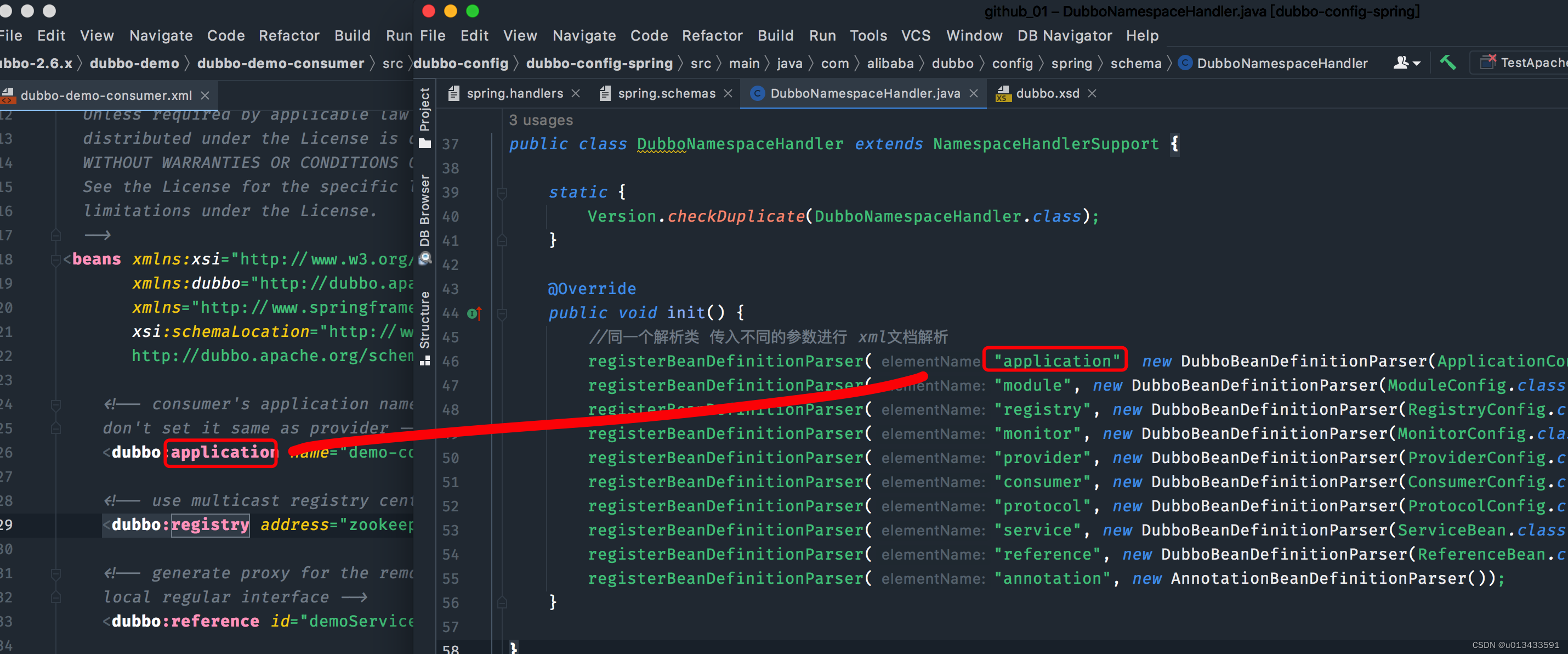

1.6.2 集成电路的成本

在竞争日益激烈的计算机市场中,标准零件(磁盘、闪存、DRAM等)的成本已成为任何系统成本的重要组成部分,集成电路的成本在不同计算机的成本中所占的比例越来越大,尤其是在高产量、成本敏感的市场中。事实上,随着PMD越来越依赖整体片上系统(systems on a chip,SOC,在单个芯片上集成一个完整系统),集成电路的成本已成为PMD成本的主体。因此,计算机设计人员只有了解芯片的成本,才能理解当前计算机的成本。

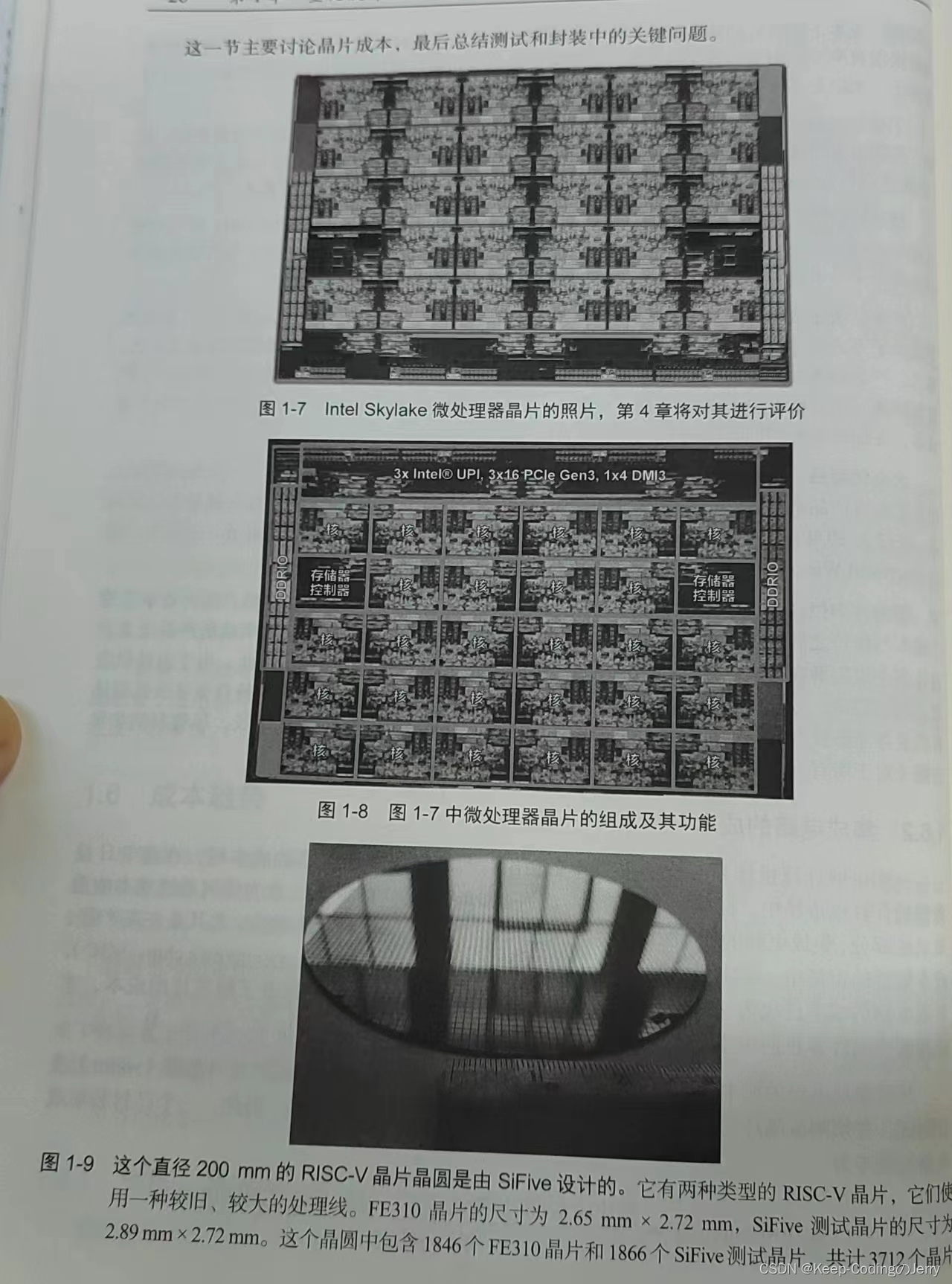

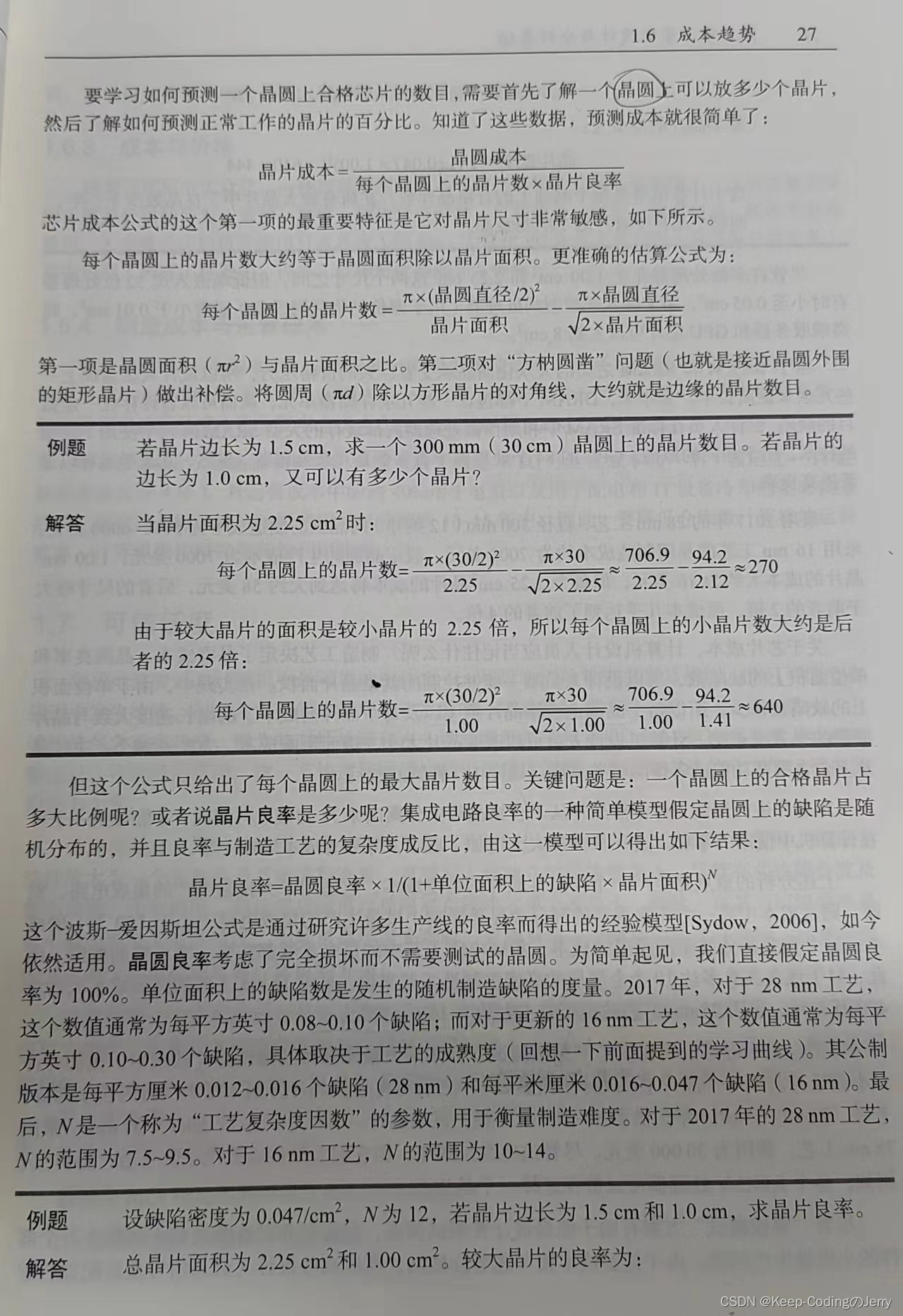

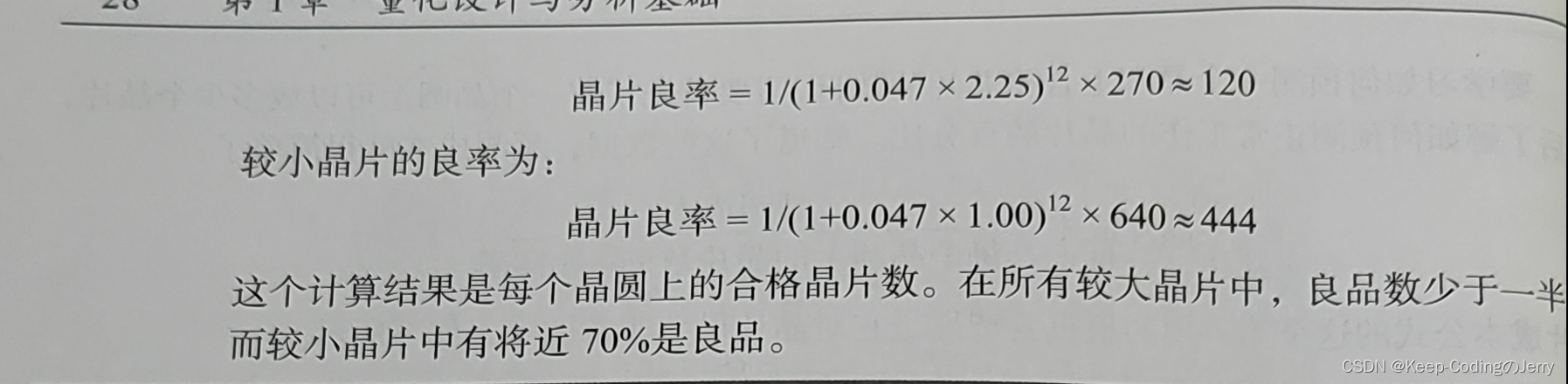

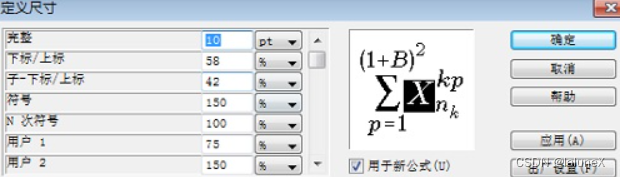

尽管集成电路的成本大幅下降,但基本的硅制造工艺没有变化:仍然要对晶圆(wafer)进行测试,并切割成晶片(die)进行封装(见图1-7、图1-8和图1-9)。因此,一个已封装集成电路的成本为:

集成电路的成本=(晶片成本+晶片测试成本+封装与最终测试成本)/最终测试良率

下面有关计算的内容就直接上图了,书上讲得挺清晰的。

尽管许多微处理器介于1.00cm2和2.25cm2这两个尺寸之间,但低端嵌人式32位处理器有时小至0.05cm2、用于嵌入式控制的处理器(用于廉价的物联网设备)通常小于0.01cm2 ,而高端服务器和GPU芯片可以大到8cm2。

由于DRAM和SRAM之类的大众化商品承受着巨大的价格压力,所以设计人员会加上一些冗余来提高良率。多年来、DRAM中都包含一些冗余存储器单元,从而可以容许存在一定数目的缺陷。设计人员在标准SRAM中和用作微处理器内部缓存的大型SRAM阵列中使用了类似的技术。出于相同的原因、GPU的84个处理器中有4个是冗余处理器。显然,冗余单元可以显著提高良率。

采用2017年的28nm工艺,直径300mm(12英寸)的晶圆的制造成本为5000~6000美元:

采用16nm工艺的晶圆制造成本约为7000美元。假定晶圆的生产成本为7000美元,1.00cm2晶片的成本大约为16美元,但每个2.25cm2晶片的成本将达到大约58美元,后者的尺寸略大于前者的2倍,而成本几乎达到了前者的4倍。

关于芯片成本,制造工艺决定了晶圆成本、晶圆良率和单位面积上的缺陷数,所以设计人员唯一能够控制的就是晶片面积。在实践中,由于单位面积上的缺陷数很少,所以每个晶圆上合格晶片数(以及每个晶片的成本)的增长速度大致与晶片面积的平方成正比。计算机设计人员可以改变晶片大小,进而影响成本,方法有两个:决定晶片上包含哪些功能或者排除哪些功能,确定/管脚的数目。

对晶片进行测试(将合格晶片从不合格晶片中分离出来)、封装、再测试,才能得到一个可在计算机中使用的零件。这些步骤都大大增加了成本,导致总成本增加一半。

上述分析的重点是生产一个功能性晶片的可变成本,它适用于大批量生产的集成电路。然而,固定成本中有一个非常重要的部分会显著影响小批量生产的集成电路(小于100万)的成本,这个重要部分就是掩膜(掩膜(MASK):全称单片机掩膜,是指程序数据已经做成光刻版,在单片机生产的过程中把程序做进去)组的成本。集成电路工艺中的每个步骤都需要一个单独的掩膜。因此,对于现在具有多达10个金属层的高密度制造工艺来说,采用16nm工艺的掩膜成本大约为400万美元,采用28nm工艺的掩膜成本大约为150万美元。

好消息是半导体公司提供了“穿梭测试”方案来大幅降低微型测试芯片的成本。他们将许多小型设计放到单个晶片上,以分摊掩膜成本,之后再将这些晶片分割为每个项目的较小部分于是,TSMC于2017年提供了80~100个未经测试的晶片,其尺寸为1.57mm×1.57mm,采用28nm工艺,费用为30000美元。尽管这些晶片很小,但它们为架构师提供了数百万个晶体管例如,多个RISC-V处理器可以放在这样一个晶片上。

尽管“穿梭测试”方案有助于原型设计和测试调试,但它们并没有解决数十到数十万个部件的小批量生产问题。由于掩膜成本很可能继续增加,所以有些设计人员采用可重新配置的逻辑,以增强一个零件的灵活性,进而降低掩膜带来的成本。

![[附源码]计算机毕业设计springboot“科教兴国”支教门户网站](https://img-blog.csdnimg.cn/e888571e5e8b49868c4d5821d2853d9b.png)