目录

1. 纳米级设计

2. 什么是STA

3. 为什么要进行STA

4. 设计流程

5. 不同阶段的STA

6. STA的局限性

1. 纳米级设计

在半导体器件中,金属互连线通常被用来连接电路中的各个部分,进而实现整个芯片。随着制造工艺的进一步缩小,这些互连线对芯片性能的影响开始显现。对于深亚微米(≤0.25um)或者纳米级(≤0.1um)的工艺,互连线之间的耦合电容会引起噪声和串扰,而这两者都会限制芯片的运行速度。在老旧工艺中,噪声和耦合效应都是可以忽略不计的,而现在它们在纳米级工艺中扮演重要的角色。所以物理实现(Physical Design,或者叫后端设计)和设计验证(Design Verification)都应该考虑串扰和噪声的影响。

2. 什么是STA

STA(Static Timing Analysis,静态时序分析)是多种验证数字电路时序方法中的一种。另一种验证时序的方法是时序仿真(Timing Simulation),它不仅可以验证时序,还可以验证功能。“时序分析”这个词通常被用来指代这两种方法——STA,或者时序仿真中的一种。所以简单地说,时序分析就是指分析电路的时序问题。

STA中的“静态”是指整个电路的分析是静态进行的,不依赖于输入端口的激励(Stimulus)。这和基于仿真的时序分析形成了鲜明对比。时序仿真时,在输入端口施加激励,电路的行为被观察和验证,然后随时间进行施加新的激励,新的电路行为被观察和验证,诸如此类。

STA的目的就是去验证1个电路是否可以在给定的1组时钟、给定的电路外部环境下,正常工作在额定速度上。也就是说,这个电路可以安全地工作在指定的时钟频率上而没有任何时序违例(Timing Violations)。我们平常主要关注的就是建立时间检查(Setup Timing Check)。建立时间检查保证了数据可以在给定的时钟周期内到达触发器(Flip-Flop)。而保持时间检查则是保证了数据至少稳定了一段时间,没有预料之外的数据到达触发器。上述这些就保证了触发器可以采到正确的数据并且为新的状态保持好这些数据。

相对于时序仿真来说,STA的特点有:

①速度快;

②基于形式化,数学技术而非测试向量,可以彻底验证;

③验证同步时钟之间的时序,不验功能。

总的来说,STA的意义在于整个设计只需要分析一次就可以对所有的场景和路径进行必要的时序分析。因此,STA是一种完备的验证设计时序的方法。

3. 为什么要进行STA

STA可以对设计中所有时序进行完备的验证。而时序仿真只能验证被激励执行到的部分时序,且对于大型设计来说,速度很慢。

设计的功能和性能都会受到噪声的限制。噪声产生的原因有:信号线之间的串扰、主要输入端口或电源引入的噪声。噪声的影响会限制设计的频率,也可能会造成功能错误。所以,设计的物理实现必须验证设计具有鲁棒性(健壮性),这意味着设计可以运行在额定频率并容忍一定的噪声。

基于逻辑仿真的验证无法处理串扰、噪声和片上变化的影响。

4. 设计流程

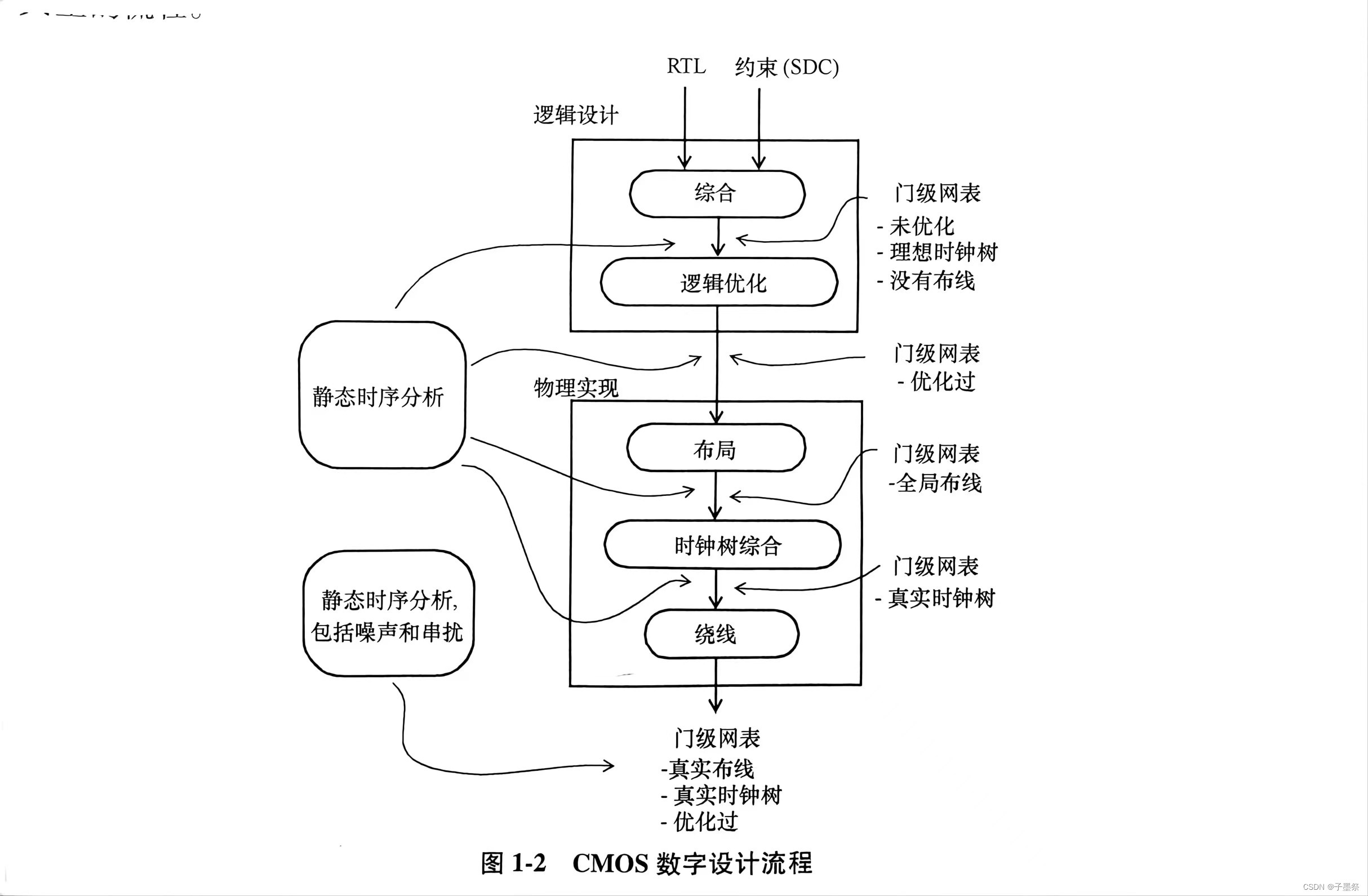

在CMOS数字设计流程中,STA可以在物理实现的各个阶段中进行来确定最差的时序路径。

当RTL级设计综合到门级网表,就可以用STA来验证设计的时序。

STA在逻辑优化之前运行,这是为了提前确定最差或关键的时序路径。STA也可以在优化之后再次运行,这是为了检查是否还有遗留的时序违例路径需要再次优化,确定关键的时序路径。

在物理实现的开始,时钟树被认为是理想的,即时钟树上的延迟为零。一旦物理实现开始,时钟树被综合好,STA将再次检查时序。事实上,在物理实现的过程中,可以在每个阶段执行来确定最差的时序路径。

在物理实现过程中,所有的逻辑单元被金属互连线连接起来。金属绕线的寄生RC(电阻和电容)会影响经过这些绕线的信号路径延迟。在典型的纳米级设计中,互连线的寄生参数是造成延迟和功耗损失的主要原因。所以,对设计的任何都应该评估互连线对性能(频率、功耗等)的影响。综上所述,信号线之间的耦合效应带来噪声,验证时必须考虑噪声对性能的影响。

在逻辑设计阶段,因为没有关于布局的物理信息,可以假设互连线是理想状态的,此阶段更关注是哪些逻辑造成了最差的时序路径。还有一种技术在此阶段被用来估计互连线长度,那就是线负载模型(Wireload Model)。线负载模型会基于单元的扇出(Fan-out)估算出RC值。 (DC就是基于线负载模型的,而DCG则是在后端反馈def后运行,多了物理的东西,更加准确)

在完成绕线之前,后端工具会预估绕线的距离来得到该绕线的RC寄生参数。因为没有最终确定,这一阶段被称为全局布线(Global Route),和它对应的阶段是最终布线(Final Route)。在全局布线阶段,用简化的绕线来估计绕线长度,而估计的绕线则用来电阻和电容值。这些电阻和电容值又被用来计算线延迟(Wire Delay)。在这一阶段,耦合效应是无法分析的。当精细绕线完成后,就可以提取实际的RC值来分析耦斜应的影响了。但是,物理实现工具在计算RC值时,可能仍然会使用近似值来缩短运行时间。

提取工具是用来从绕线完成的设计中提取详细的寄生参数(RC值)。提取工具通有以下选项:在迭代优化时,用较少的运行时间得到相对较低精度的RC值;在最终验证时,用更长的运行时间得到非常精准的RC值。

总结一下,在门级网表运行STA,需要考虑以下条件:

1)互连线是如何建模的:理想互连线,线负载模型,具有近似RC值的全局布线,者具有精准RC值的真实布线。

2)时钟是如何建模的:理想时钟(零延迟)或者传播时钟(真实延迟)。

3)是否考虑信号之间的耦合效应,也就是说是否分析串扰噪声。

图1-2似乎暗示STA是在实现过程中每个步骤以外完成的,也就是说STA是在综逻辑优化以及物理实现的每个步骤之后进行的。但实际上,这些步骤在实现功能时都进行集成的(递进的)STA。比如,逻辑优化步骤中的时序分析引擎就负责找到关键时序路径并对其优化。类似地,布局工具集成的时序分析引擎就负责在逐渐布局的过程中保持时序质量。

5. 不同阶段的STA

在逻辑级(门级,没有布局布线),STA要用到以下模型:

1)理想互连线或者基于线负载模型的互连线。

2)带有预估时钟抖动(Clock Jitter)和时钟延迟(Clock Latency)的理想时钟。

在物理实现阶段,除了以上模型,STA还会用到:

1)互连线:可以是使用预估RC值的全局布线,可以是提取近似RC值的真实布线,也可以是使用签核(Sign off)精度的真实布线。

2) 时钟树:真实时钟树。

3)包括或不包括串扰的影响。

6. STA的局限性

虽然时序和噪声分析在任何情况下都可以很好地分析设计中的时序问题,但在最先进的工艺中仍然无法用STA来完全替代时序仿真。这是因为STA仍然无法捕捉和验证时序验证的某些方面。

STA的局限性:

1)复位序列(Reset Sequence):要检查是否所有的触发器在收到异步或同步复位信号后都复位到所需的逻辑值,STA是做不到的。芯片可能无法退出复位状态。这是因为一些特定的声明,比如某些信号的初始值,没有被综合,且只能在仿真时验证。

2)X状态处理:STA只能处理逻辑0和逻辑1(或者高电平/低电平)的逻辑域,或者电平上升和下降。设计中1个未知的状态X会造成不确定的值在设计中传播,STA无法进行这种检查。即使STA的噪声分析可以分析并传播设计中的毛刺,但这一类型的毛刺分析和传播与未知状态X的处理也是非常不同的,后者是纳米级设计的基于时序仿真的时序验证的一部分。

3)PLL(Phase-Locked Loops,锁相环)设置:PLL的配置可能没有被正确读取和设置。

4)跨异步时钟域(Asynchronous Clock Domain Crossings):STA不能检查是否使用了正确的时钟同步器,需要其他工具来保证在跨异步时钟域的地方都有正确的时钟同步器。

5)IO接口时序:仅依靠STA的约束来指定IO接口的需求是不太可能的。举例来说,工程师可能用SDRAM仿真模型,为DDR接口选择精细的电路级仿真。这种仿真可以保证读取和写入存储器都有足够的余量,也保证在必要时可以用DLL (Delay Locked Loop,延迟锁相环) (如果有)来对齐信号。

6)模拟和数字块(Block)之间的接口:因为STA不能处理模拟块,需要相应的验证方法来确保两种块之间的连接是正确的。

7)伪路径:STA确保逻辑路径的时序满足所有的要求,并且标记出那些不满足要求的逻辑路径。在很多情况下,哪怕逻辑值永远不可能传播到这条路径,STA还是标记了这条路径为违例路径。这种情况的发生,通常是由于系统应用使用不到这条路径,或者互相冲突的情况发生在这条违例路径上。这些时序路径被称为伪路径,因为它们永远不会被用到。如果使用了正确的包括伪路径和多周期的时序约束,STA的结果会好很多。在大多数情况下,设计者可以运用他们对设计的内在理解来指定约束,这样在STA的过程中删除伪路径。

8)FIFO指针不同步:当2个应该是同步的有限状态机(Finite State Machines)不同步时,STA不能发现该问题。在功能仿真时,2个有限状态机是可能一直同步并且在锁步(Lock-Step)时一起改变。但是,考虑到存在延迟,1个有限状态机可能会和另1个不同步,通常是由于1个有限状态机的复位(Reset)信号比另1个更早。STA检测不到这种情况。

9)时钟同步逻辑:STA不能发现时钟生成逻辑和时钟定义不符。STA会假定时钟生成器会提供时钟定义里指定的波形。时钟生成逻辑可能会被错误地优化,比如,1条没有被正确约束的路径被插入1个巨大的延迟。再比如,添加的逻辑可能会改变时钟的占空比 (Duty Cycle)。STA不能检测到任何一种可能的情况。

10)跨时钟周期的功能性行为:STA不能建模或仿真那些跨时钟周期的功能性行为变化。

尽管存在以上局限性,STA依然广泛用于验证设计的时序,而仿真(带有时序或单位延迟)则作为备用手段检查极端情况,或作为更简单的验证设计的普通功能模式。

下一篇学习STA的具体概念。