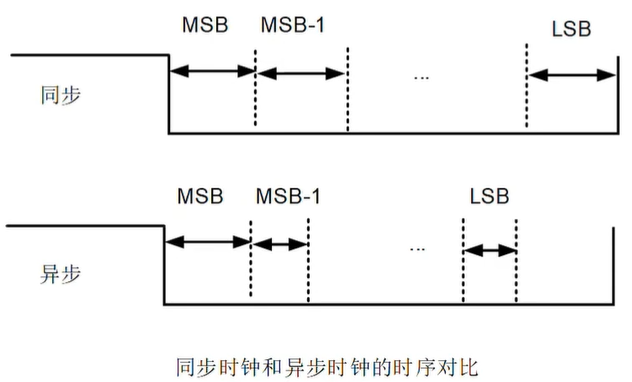

异步sar逻辑的引入:

原因1:提高转换速度

■ 同步时钟从第一个比较周期到最后一个比较周期长度都是相等的。对于Latch比较器,信号幅度越小,比较时间越长(参考latch时域响应那一节)。为了保证比较器的分辨精度<1LSB,每个比较周期需足够长。

■ 异步时钟是根据每一次比较所花费的时间自动划分比较周期,可以避免时间的浪费。

原因2:避免输入高速时钟

■ 对于同步SAR逻辑,1个100MSPS10 Bit SARADC一个转换周期需要至少11个时钟周期,意味着需要一个1.1GHz的高速时钟。

■异步SAR逻辑通过自动判断比较器的状态,从而在自动产生高频时钟,避免外部输入高速时钟

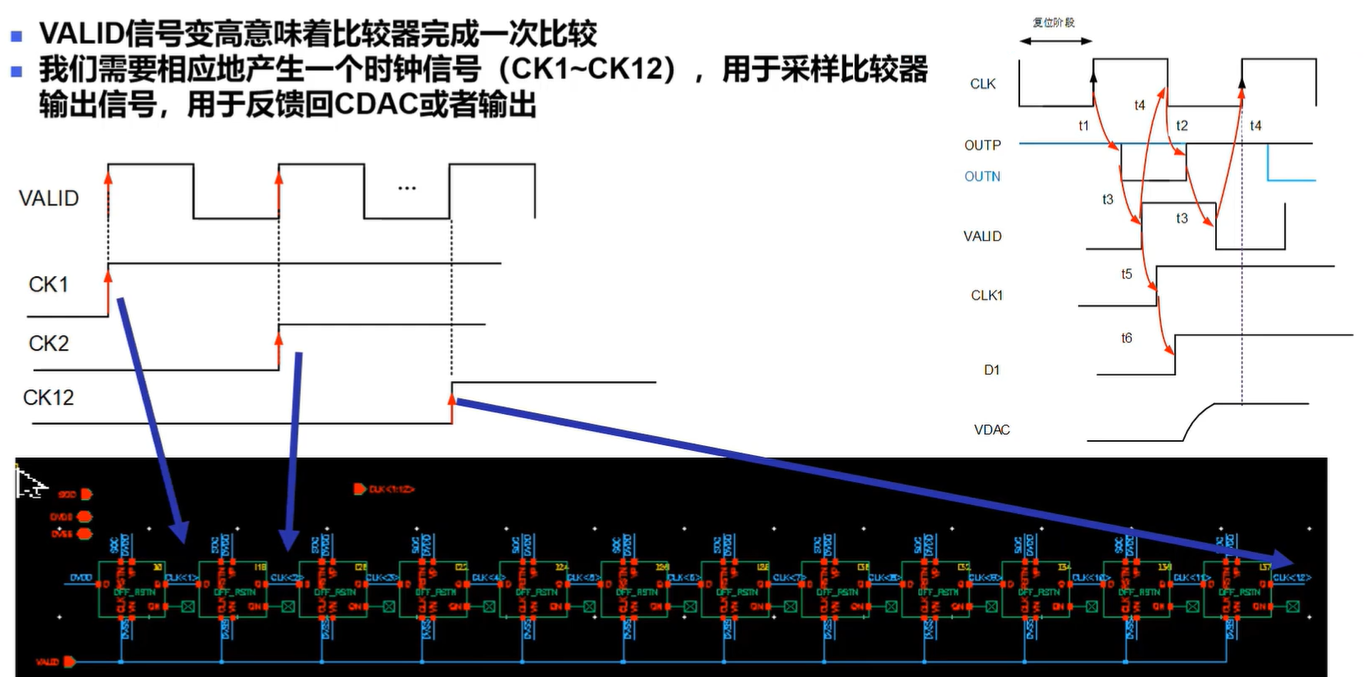

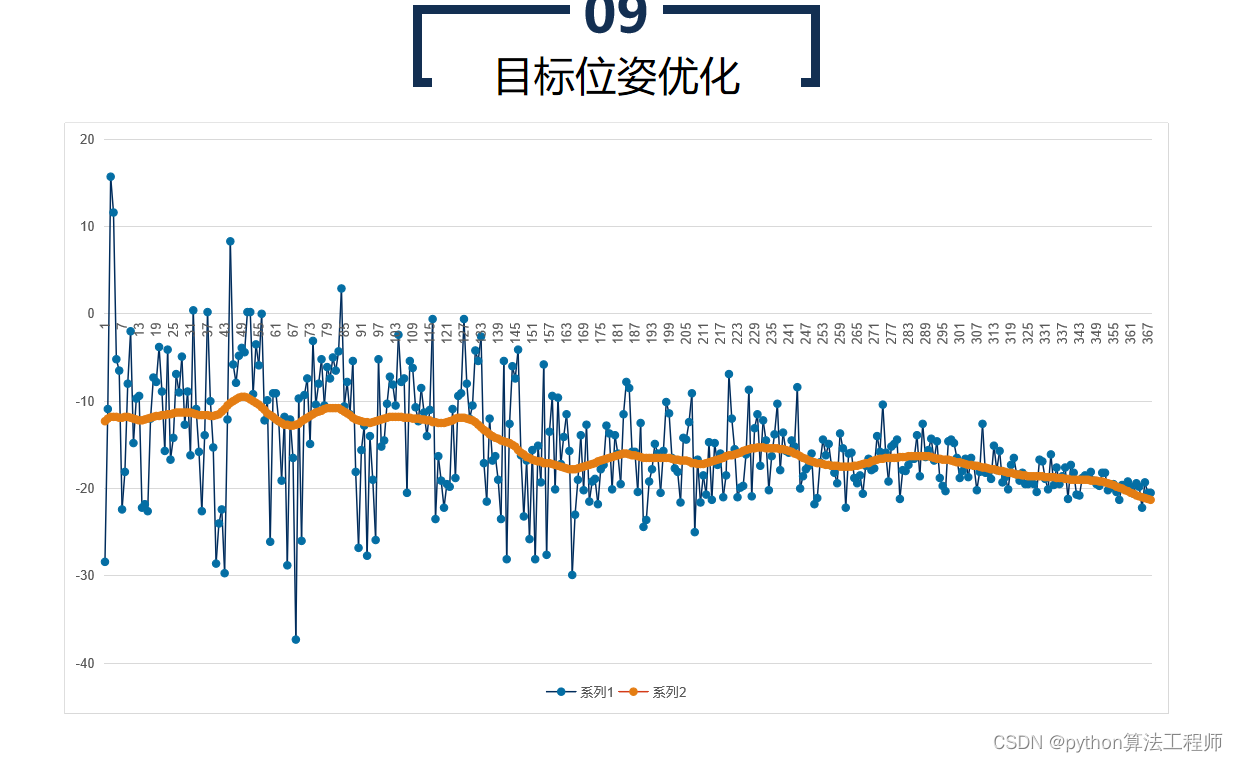

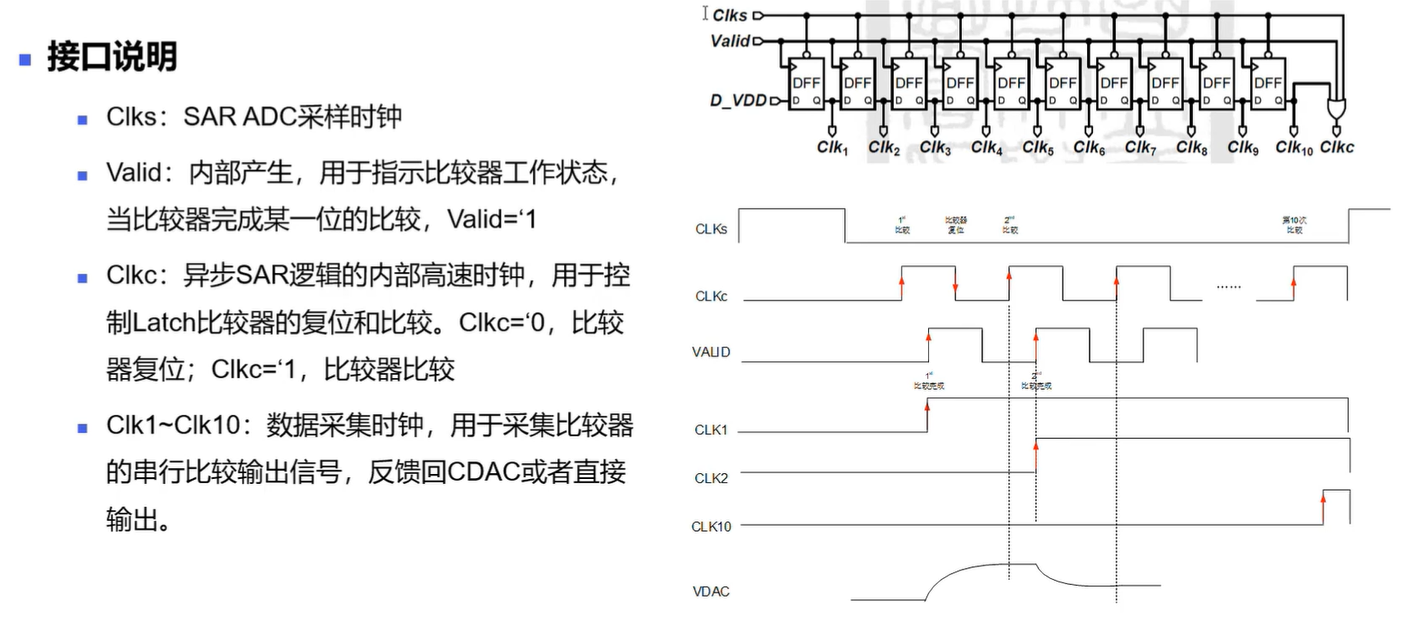

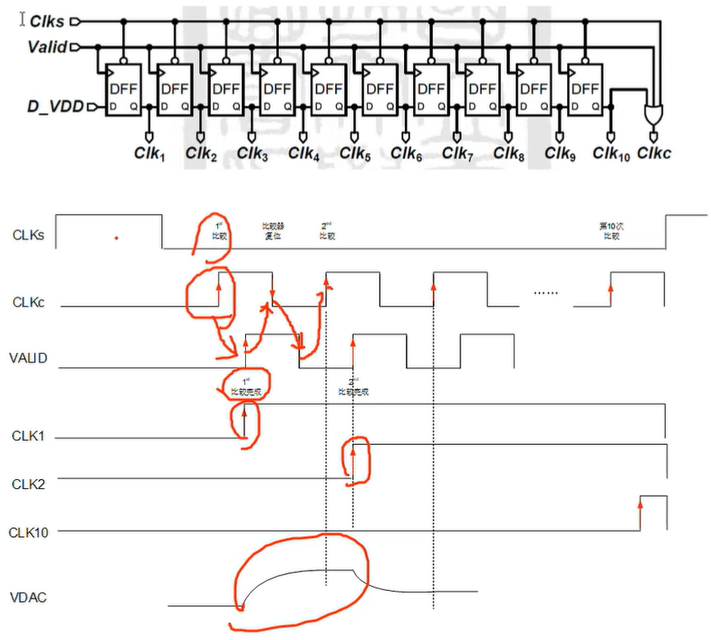

异步sar逻辑的时序图

sar逻辑时序

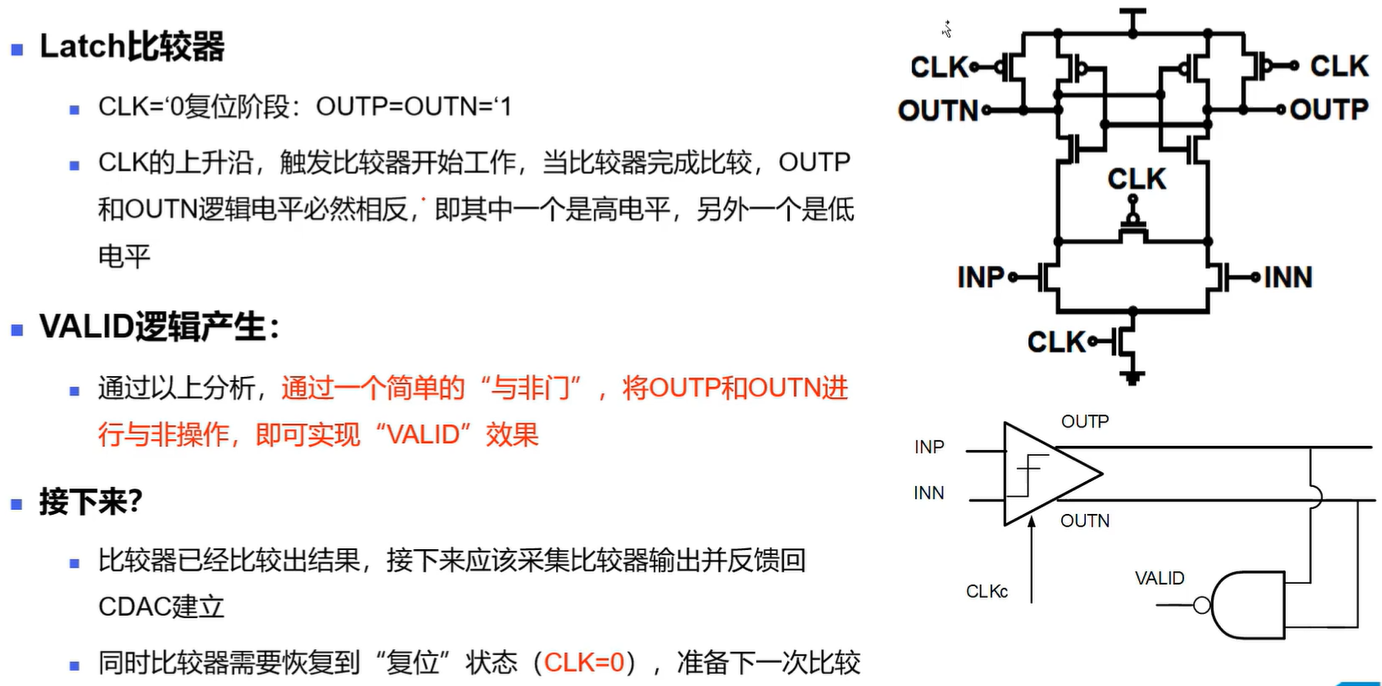

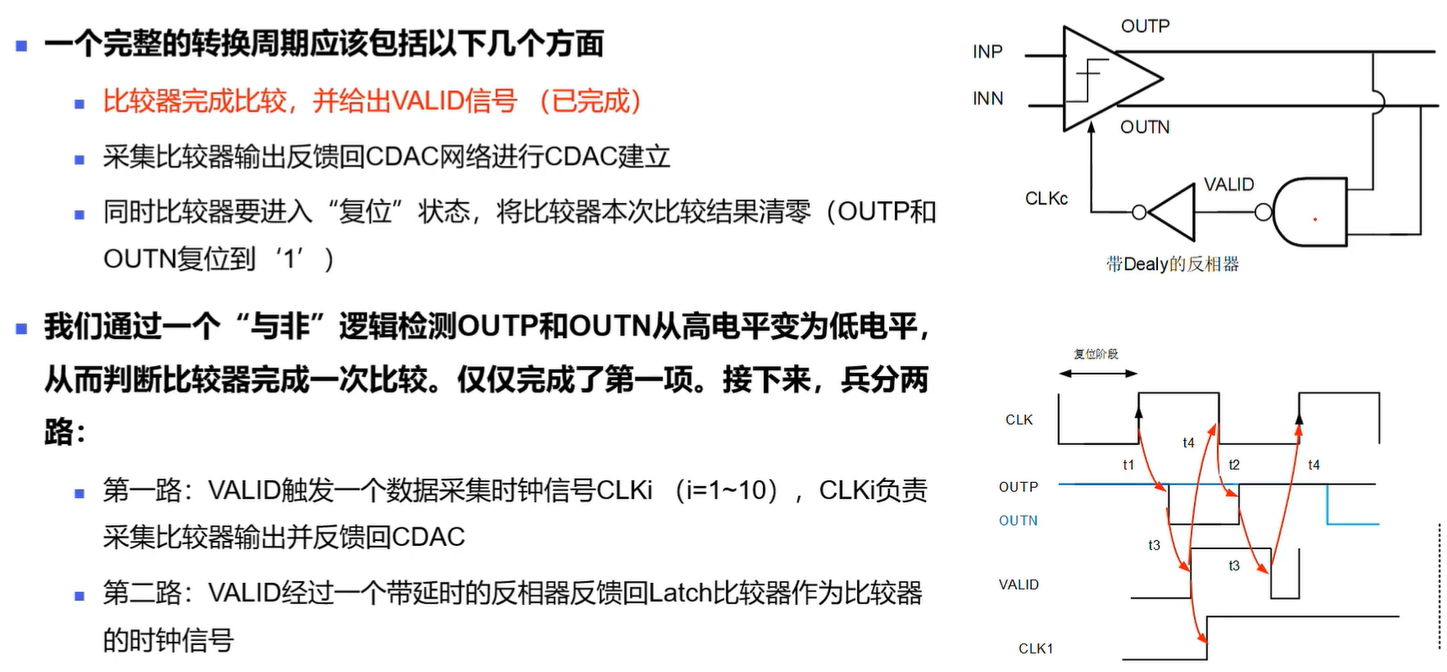

异步sar逻辑:比较器Valid产生

好多种方法,与非门,异或门,同或门啊噔噔蹬蹬

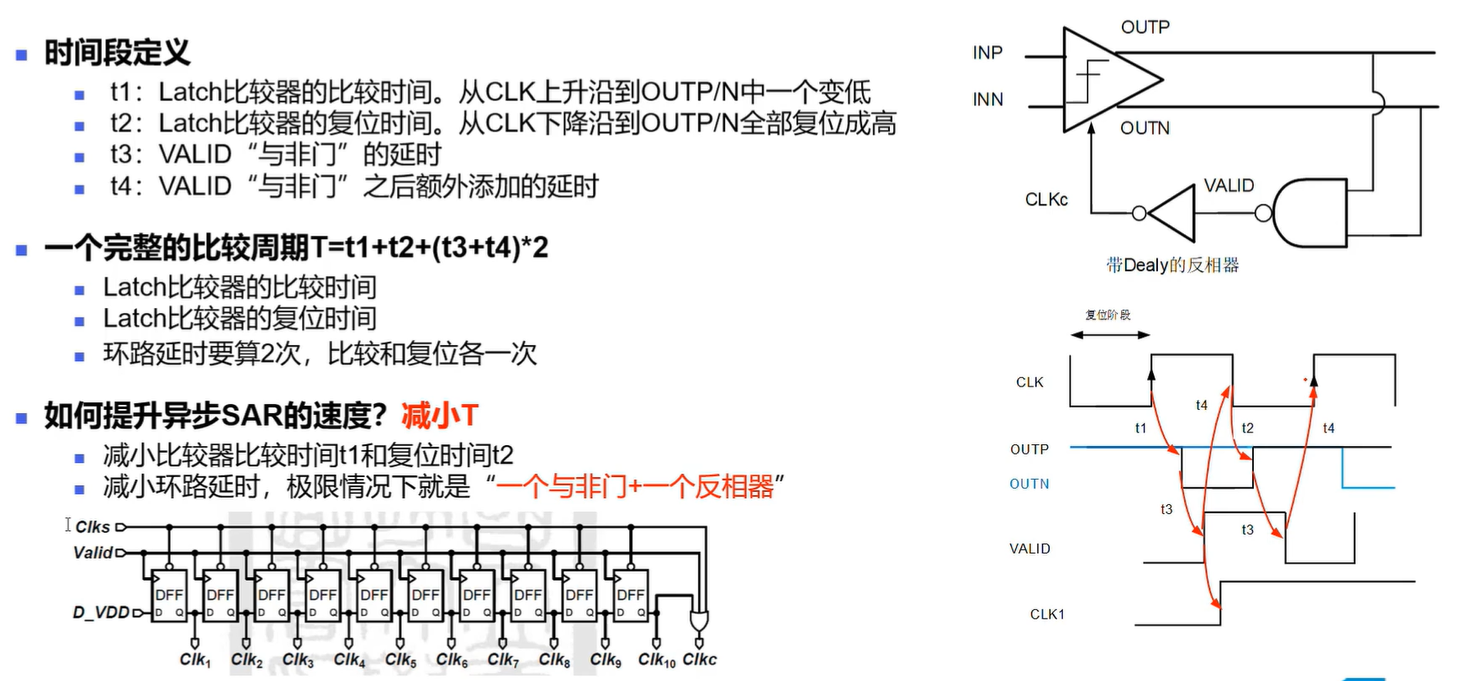

t1:比较器比较时间 -- t3:与非门延迟 -- t4:反相器延迟 -- t2:比较器复位时间

一次比较周期:t1 + t2 + 2*(t3 + t4)

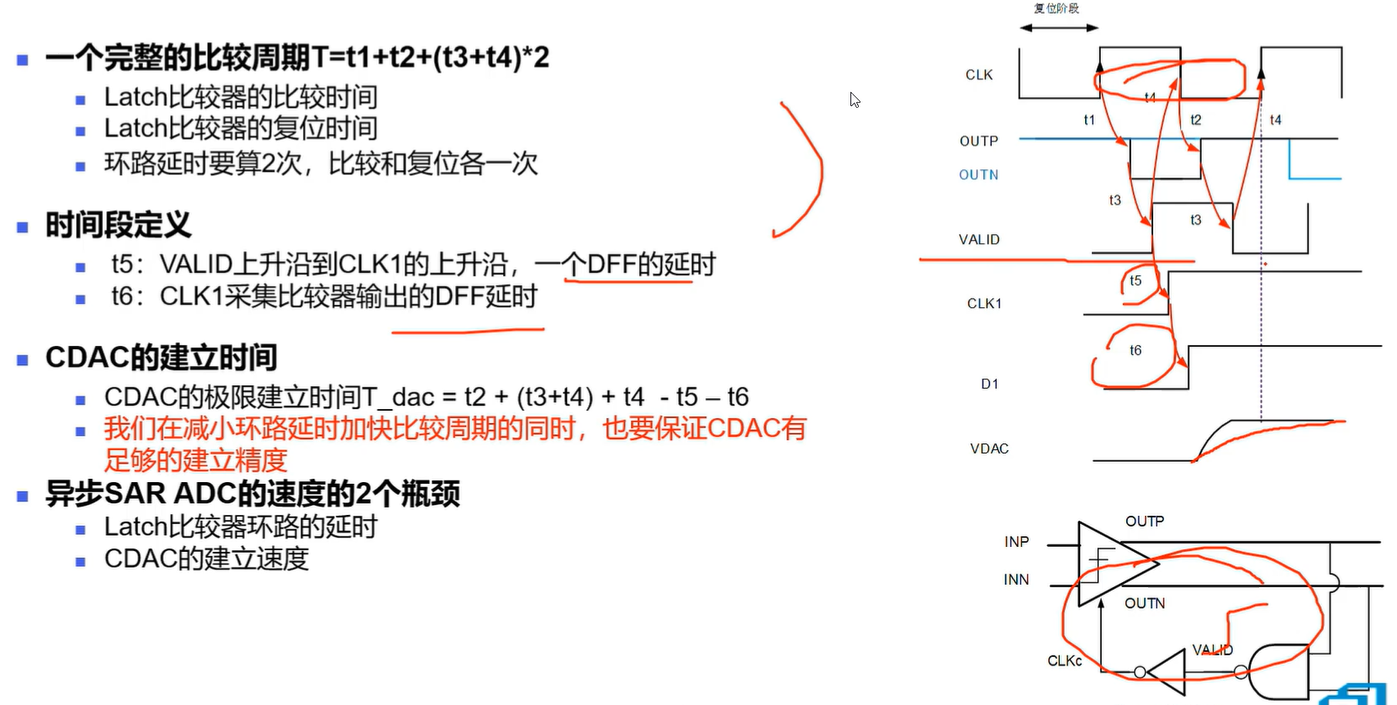

异步sar逻辑:一个完整的转换周期——重要

异步sar逻辑:CDAC的建立

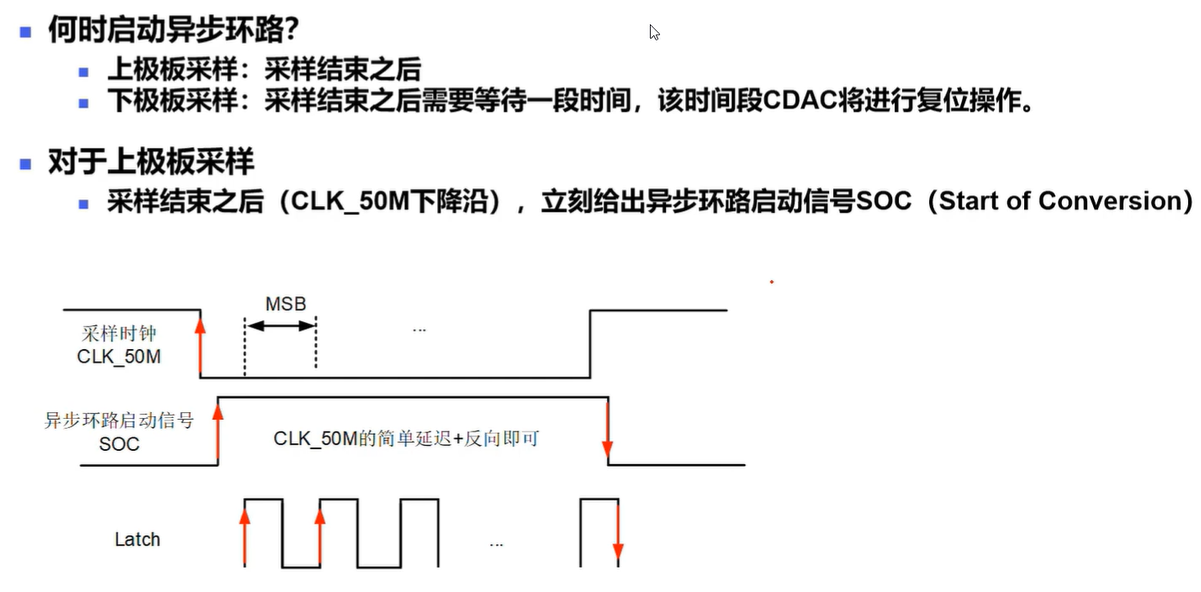

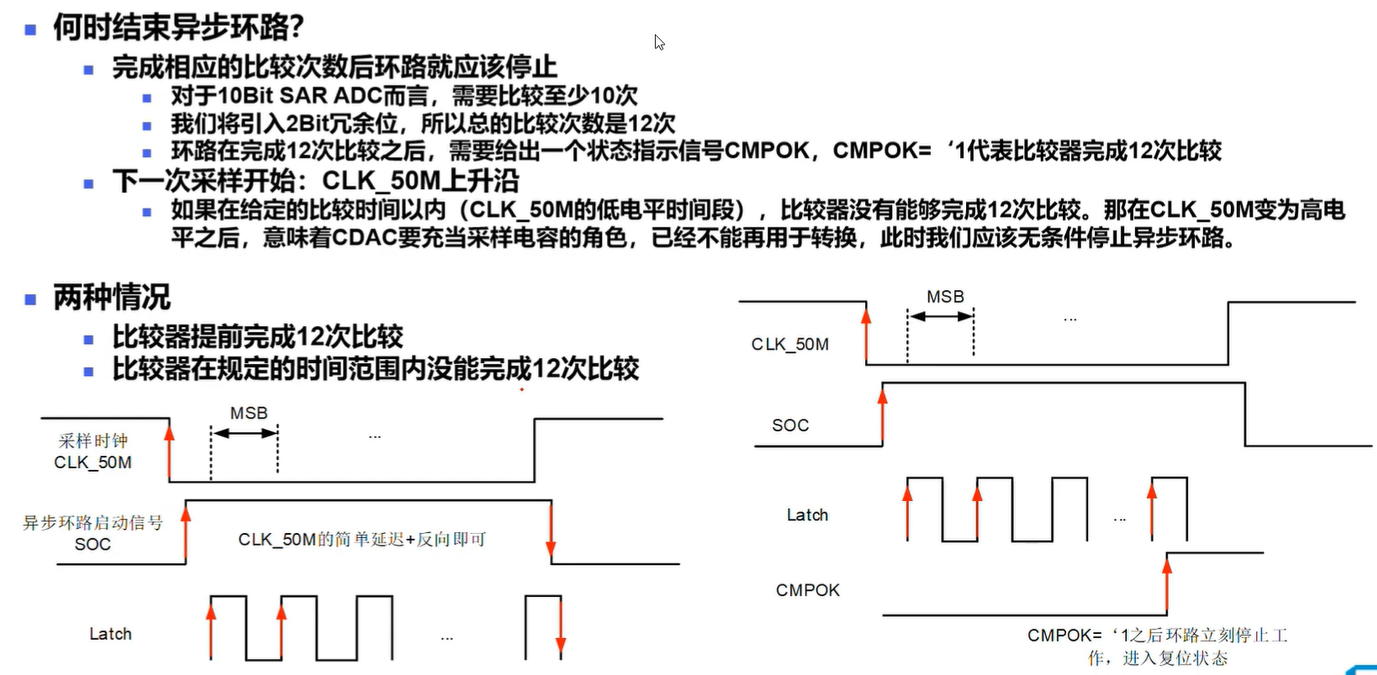

异步sar逻辑:环路的启动和结束

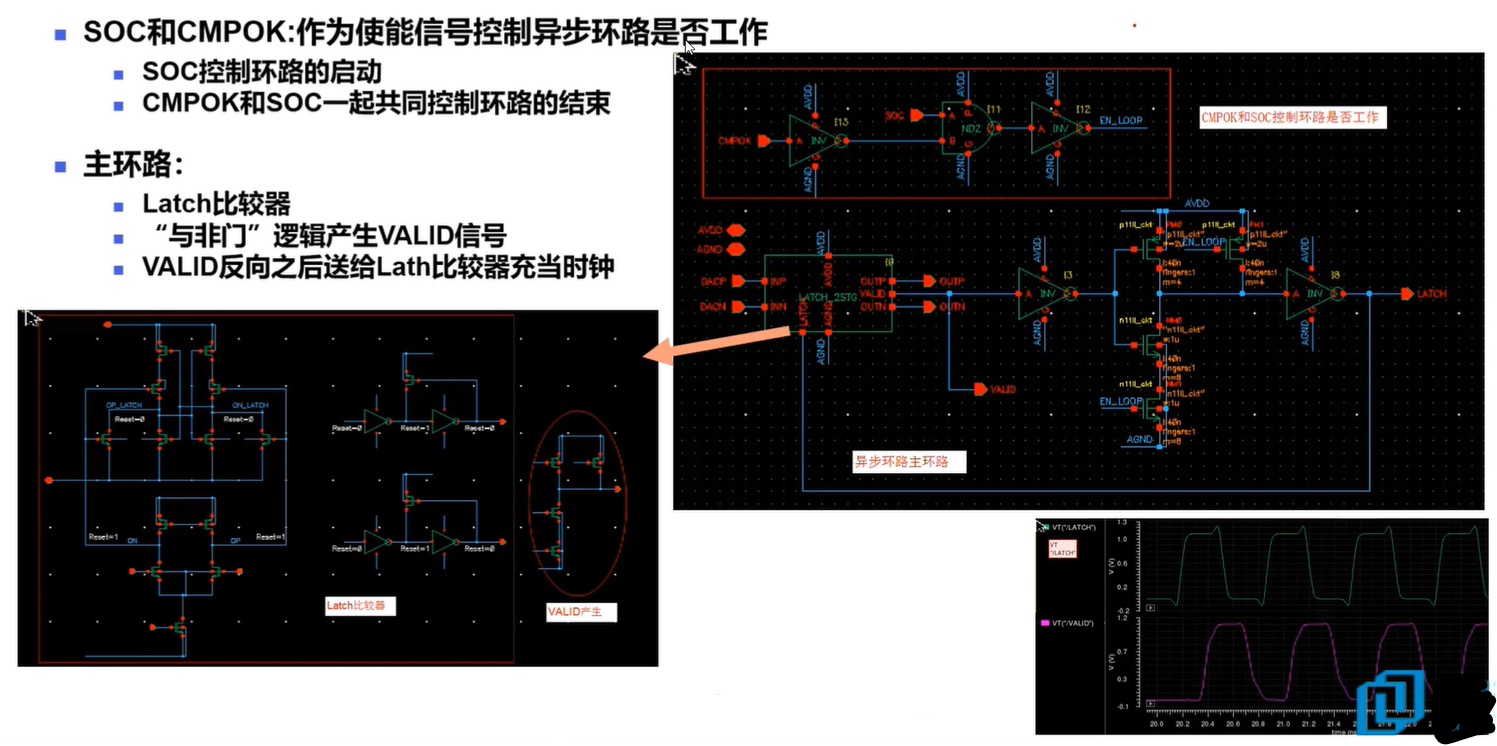

异步sar逻辑:电路实现

异步sar逻辑:CLK1~CLK12的产生