一、SPORT简介:ADI21489具有八个独立的同步串行端口(SPORT),可为各种外围设备提供I/O接口。他们是称为SPORT0至SPORT7,每个SPORT都有自己的一组控制寄存器和数据缓冲器,具有一定范围的时钟和帧同步选项。

二、特性:支持多种协议:

1、标准串口,2、左对齐,3、标准I2S,4、打包,5、TDM

三、管脚描述

1、SPORT7–0_DA_I:数据接收通道A。双向数据引脚。如果TRAN=0,输入以接收串行数据。

2、SPORT7–0_DA_O:数据传输通道A.双向数据引脚。如果TRAN=1,输出以传输串行数据。传输数据引脚始终被驱动(并继续如果串行端口启用)且TRAN=1,除非是多通道/压缩模式和非活动信道时隙发生。

3、SPORT7–0_DB_I:数据接收通道B,双向数据引脚。如果TRAN=0,输入以接收串行数据。

4、SPORT7–0_DB_O:数据传输通道B,双向数据引脚。如果TRAN=1,输出以传输串行数据。传输数据引脚始终被驱动(并继续如果串行端口启用)且TRAN=1,除非是多通道/压缩模式和非活动信道时隙发生。

5、SPORT7–0_CLK_I/O:发送/接收串行时钟。该信号可以是内部或外部生成。

6、SPORT7–0_FS_I/O:发送/接收帧同步。帧同步脉冲启动串行数据的移位。

7、SPORT7–0_TDV_O:多通道传输数据有效。此输出仅在SPORT传输多信道中激活/打包协议模式。

8SPORT7–0_DA_PBEN_O,SPORT7–0_DB_PBEN_O,SPORT7–0_CL\K_PBEN_O,SPORT7–0_FS_PBEN_O、SPORT7–0_TDV_PBEN_O

引脚缓冲区启用引脚,要将SPORTPBEN输出信号应路由至引脚缓冲器输入信号。

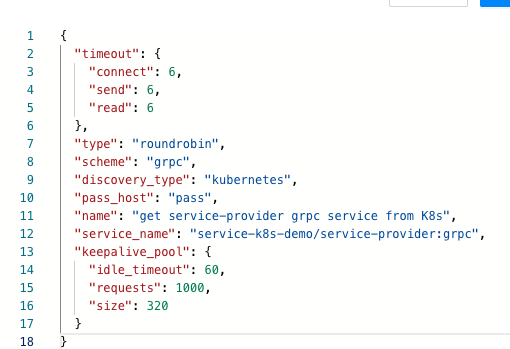

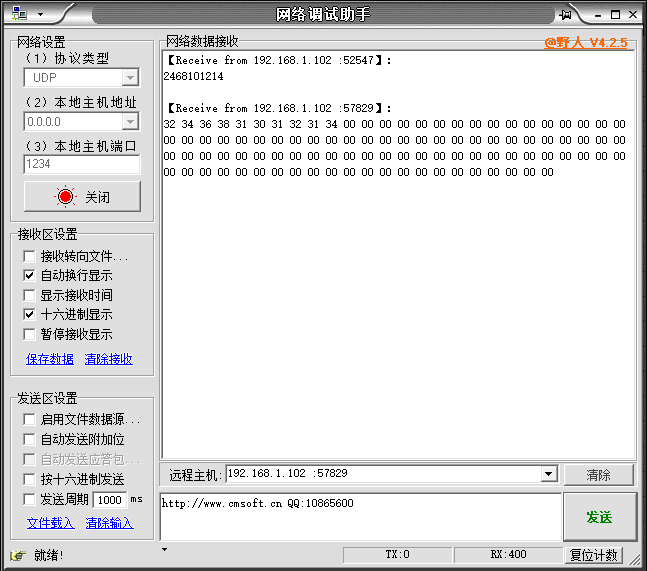

四、信号路由单元SRU编程

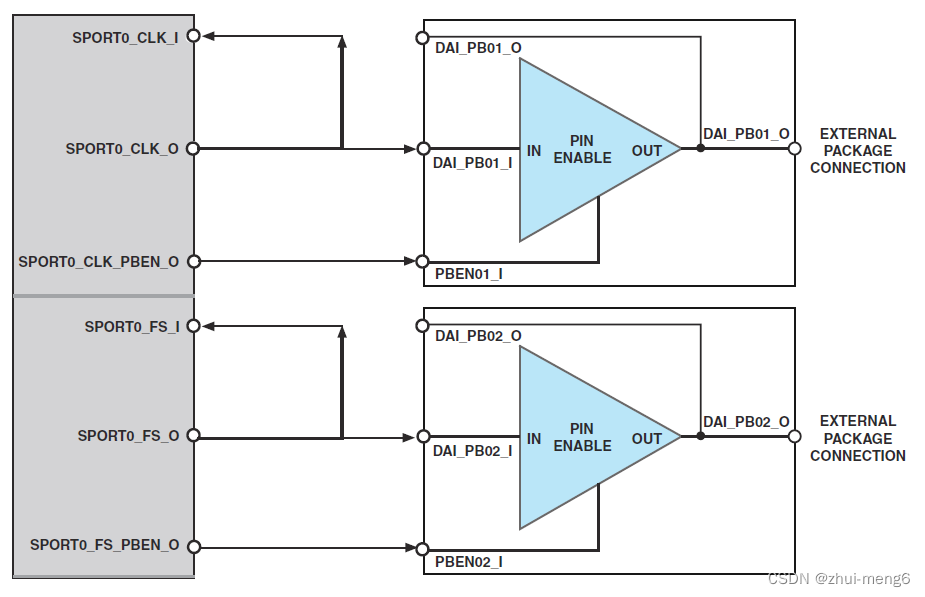

任何串行端口的信号都可以通过信号路由单元(SRU)映射到数字应用接口(DAI_Px)引脚, SPORT 6和7从其他路由源接收时钟,但无法将自己的时钟通过SRU路由到其他SPORT或其他外围设备内部。如果需要Sport6和7在外部,通过DAI引脚布线

1、SPORT作为主接收器运行,则必须提供其主输出时钟返回到其输入时钟。

SPORT为主接收器时的SRU配置图

2、SRU SPORT信号完整性,时钟(SPORTx_CLK)和帧同步对噪声有一定的敏感性,当SPORT配置为主机时,同步(SPORTx_FS)信号接受者通过正确编程信号路由单元(SRU)时钟这些信号中的反射灵敏度可以是

避免。

五、寄存器概述

1、Master Clock Divider主时钟分频器(DIVx):包含给定频率的除数值,用于内部生成的时钟和帧同步

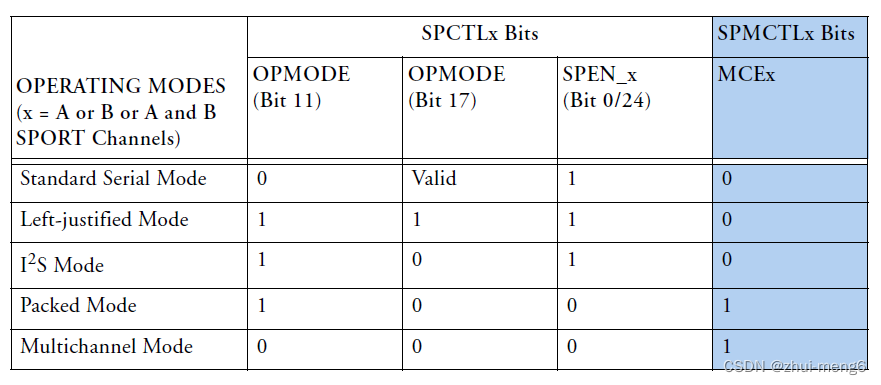

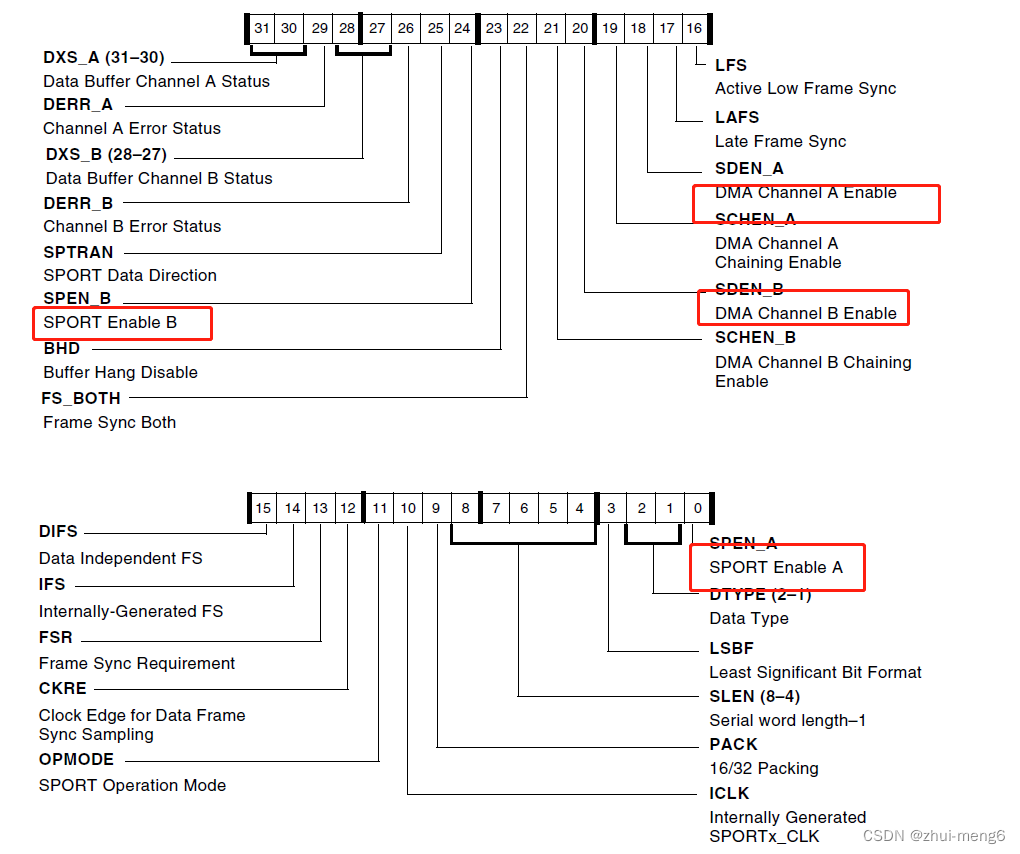

2、Serial Port Control/Status串行端口控制/状态(SPCTLx):控制串行端口模式和SPCTLx(发送和接收)控制寄存器的一部分,其他Bit位设置DMA相关的串行端口特性.

注意使能SPORT和在配置DMA时

注意使能SPORT和在配置DMA时

3、Multichannel Control/Status多通道控制/状态

(SPMCTLx):是一个全局控制以及用于多通道操作的每个SPORT(SPORT7–0)的状态寄存器,这些寄存器定义通道的数量并提供当前通道状态,多通道操作使能,并设置多通道帧延迟。

4、Serial Port Control N串行端口控制N(SPCTLNx):控制增强型串行端口模式并且还允许传统SPORT模块之间的兼容性模式切换。

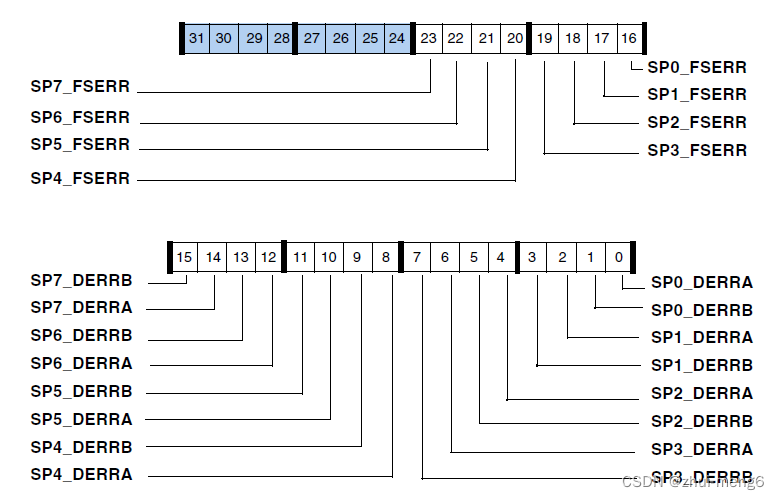

5、Serial Port Error串行端口错误(SPERRxx):两个错误寄存器(SPERRCTLx/SPERRSTAT)用于观察和控制传输期间的错误处理,检测错误可能是帧同步冲突或缓冲区溢出/下溢条件。

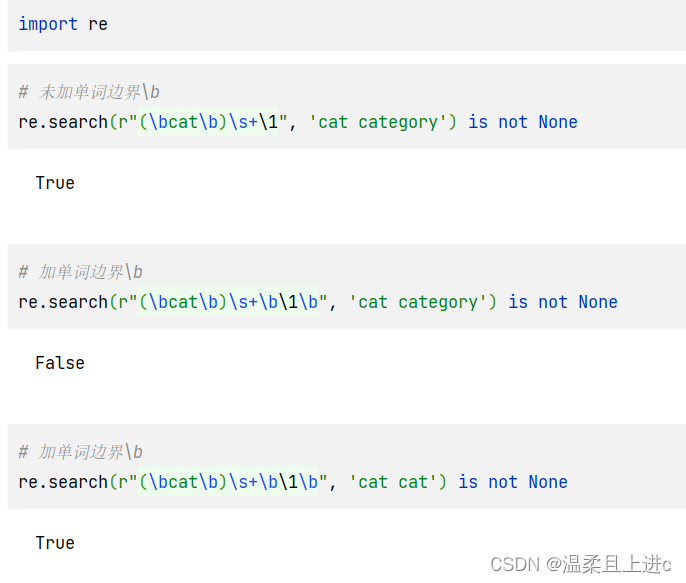

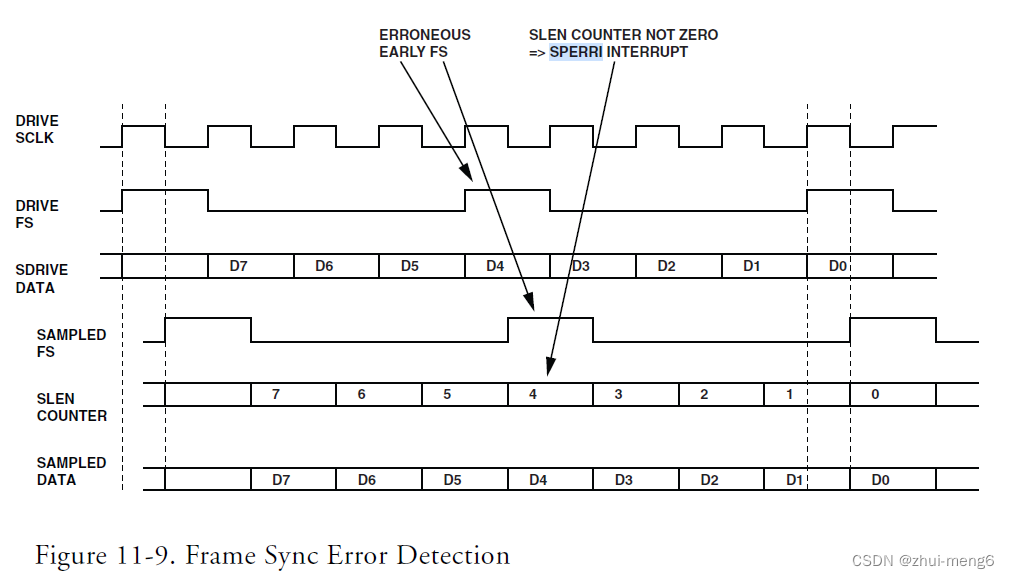

如果SLEN>Frame,则检测到意外的外部FS错误仅在数据传输期间出错FS脉冲,如图11-9所示,帧同步错误(设置错误位)为在数据传输期间发生早期帧同步时触发,或者如果帧同步的周期较小,则接收或延迟帧同步然后是串行字长度(SLEN)。然而,当前的发送/接收操作继续而不中断。

注意,在以下情况下不会检测到帧同步错误

注意,在以下情况下不会检测到帧同步错误

1、当没有数据发送/接收时(SLEN计数器为0)并且由于输入信号中的噪声而出现帧同步脉冲。它将被视为有效的帧同步。

2、如果已经存在缓冲区下溢错误,SPORT错误逻辑不被操作。

3、当帧同步脉冲<SCLK周期。

4、如果SPORT在TDM从属模式下运行,则帧同步必须在一个SCLK周期激活的新帧的开始不活跃的,如果使用例如50%的占空比,则FS错误位(SPERRSTAT)自动设置。

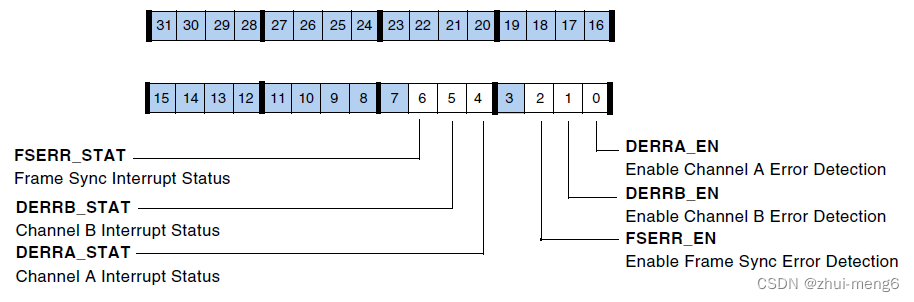

SPERRCTLx:

SPERRSTAT:

SPERRSTAT:

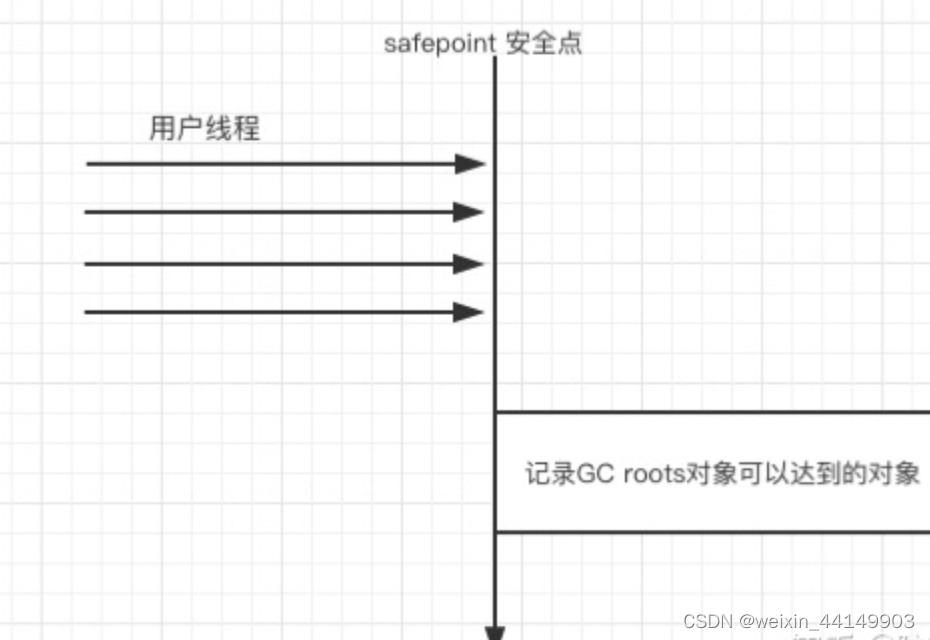

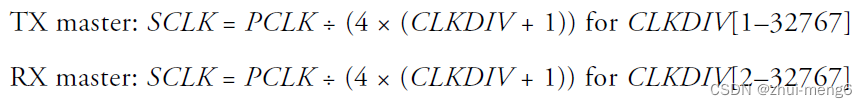

六、时钟

SPORT模块的基本计时时钟为外围时钟,时钟/4(PCLK/4),每个串行端口都有一个时钟信号(SPORTx_CLK),用于在两个相关联的数据信号上发送和接收数据。这个时钟和帧同步信号由ICLK/IFS配置SPCTLx/DIVx控制寄存器的CLKDIV/FSDIV位。一个时钟信号对A和B数据信号进行计时(配置为输入或输出)以相同的速率接收或发送数据。关闭时钟可节省电力。CLKDIV位字段指定处理器的内部时钟(PCLK)被分频以生成发送和接收时钟。如果数据信号被配置为接收机。同样,帧同步SPORTx_FS是数据信号被配置为发射机。除数是一个15位的值,(除数寄存器中的位0是

保留),允许宽范围的串行时钟速率。使用以下内容计算串行时钟频率的公式: CLKDIV = (PCLK ÷ 4 × SCLK) – 1

CLKDIV = (PCLK ÷ 4 × SCLK) – 1

FSDIV = (SCLK ÷ FSCLK) – 1

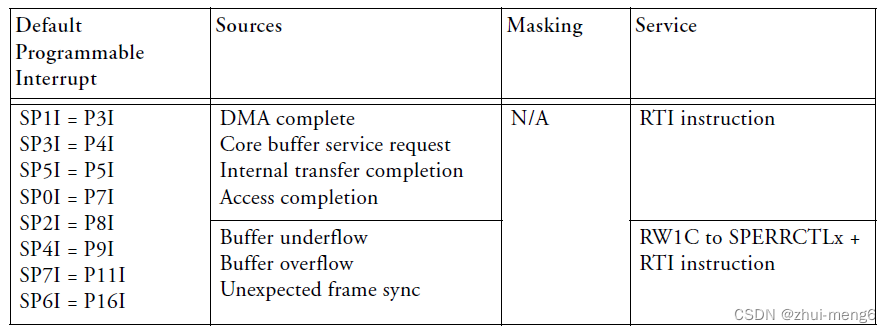

七、中断

SPORT模块生成三个本地中断信号,每个信号一个数据信道(A和B)信号和用于错误检测的第三信号。数据通道中断均逻辑“或”运算到一个SPORT中

中断信号,并且错误检测中断与所有SPORT成为一个信号,SPERRI。串行端口生成中断如以下章节所述。

如:检测异常,如缓冲区下溢、缓冲区溢出、意外的帧同步时中断,DMA完成、核心缓冲区服务请求、内部转移完成、访问完成时A或B通道信号中断。

如:检测异常,如缓冲区下溢、缓冲区溢出、意外的帧同步时中断,DMA完成、核心缓冲区服务请求、内部转移完成、访问完成时A或B通道信号中断。