上节总结cell的结构和基本操作

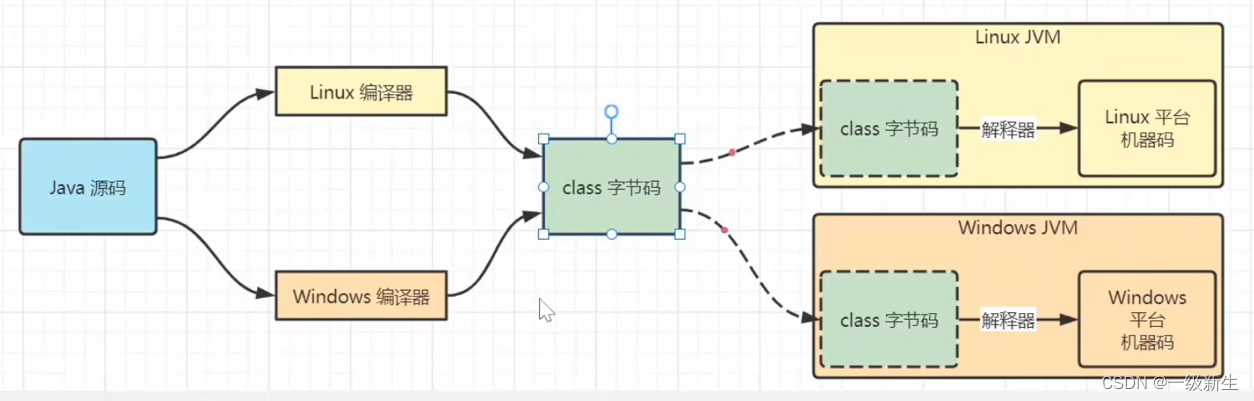

本节基于cell组合起来的DRAM组织结构

- DDR Device 的组织结构

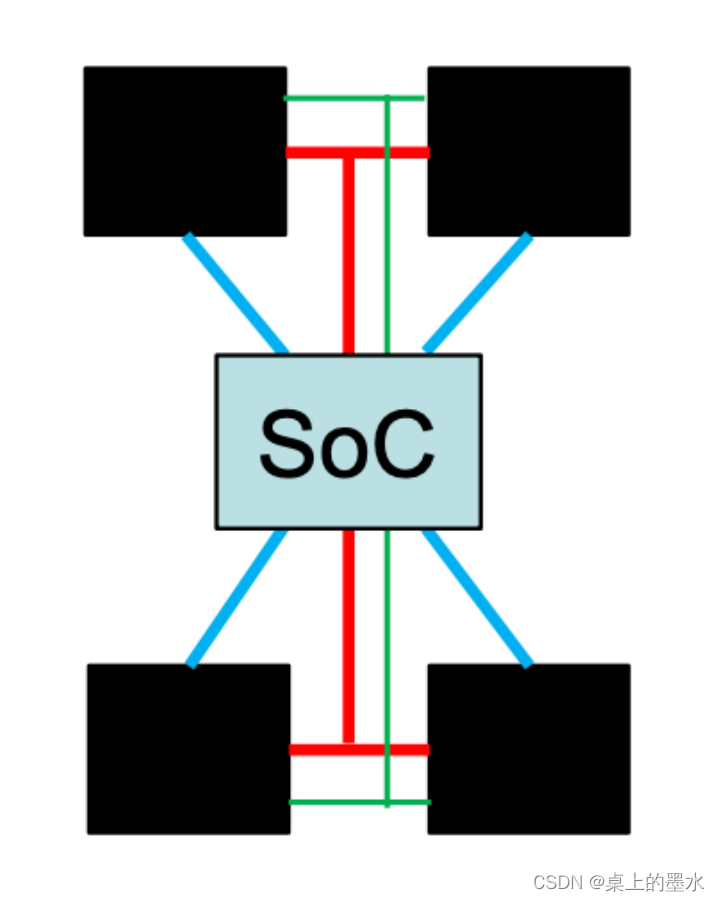

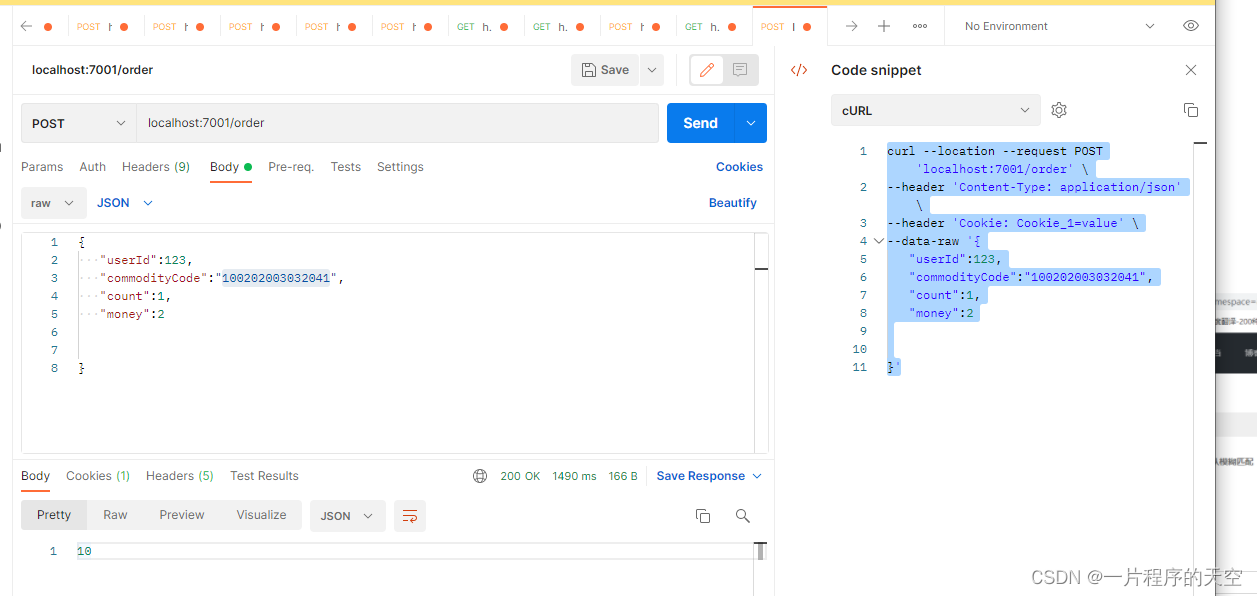

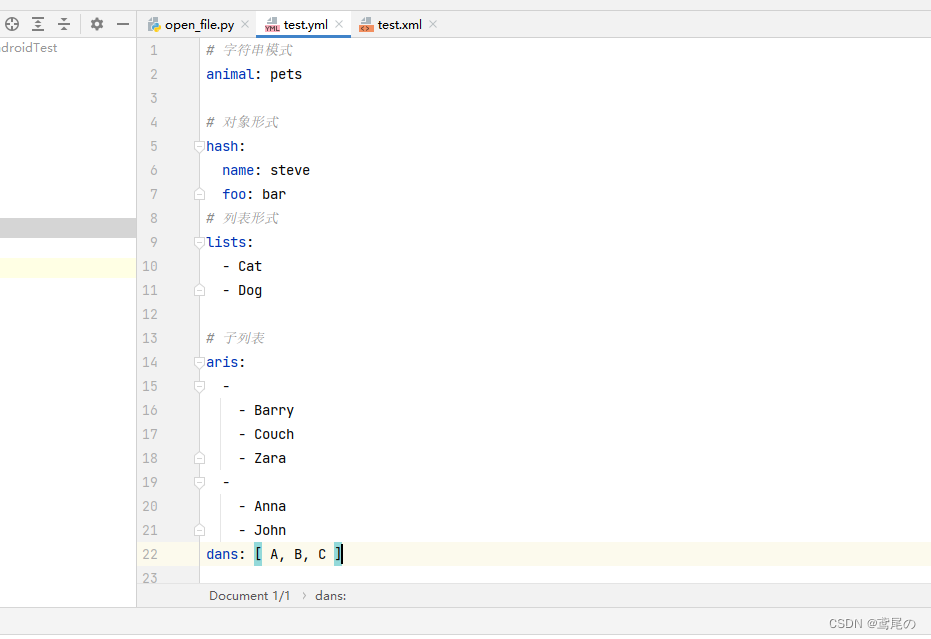

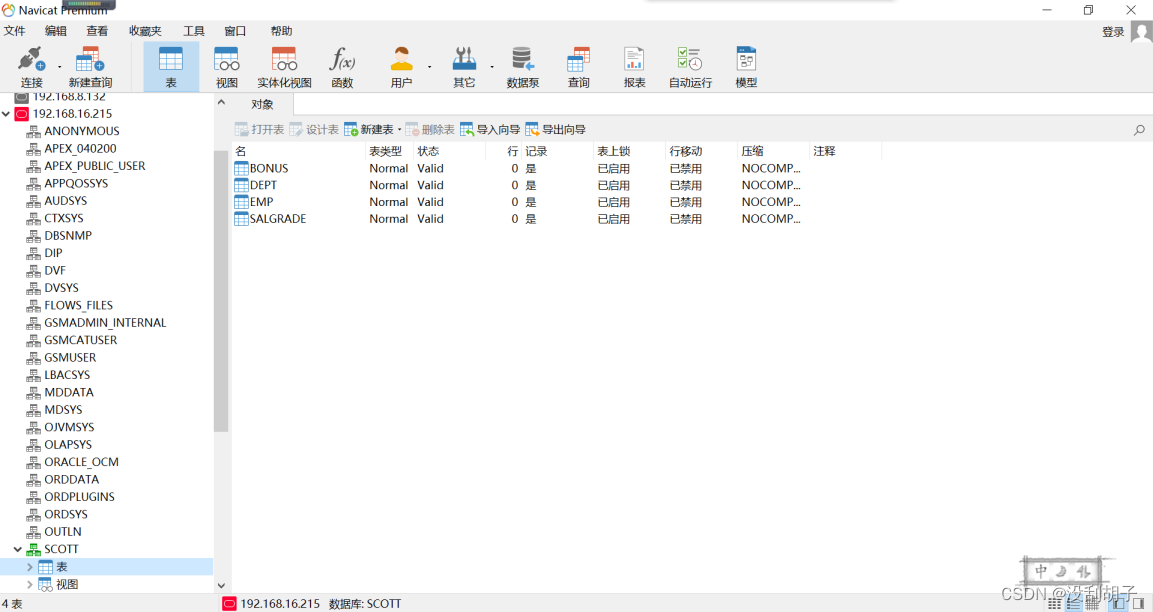

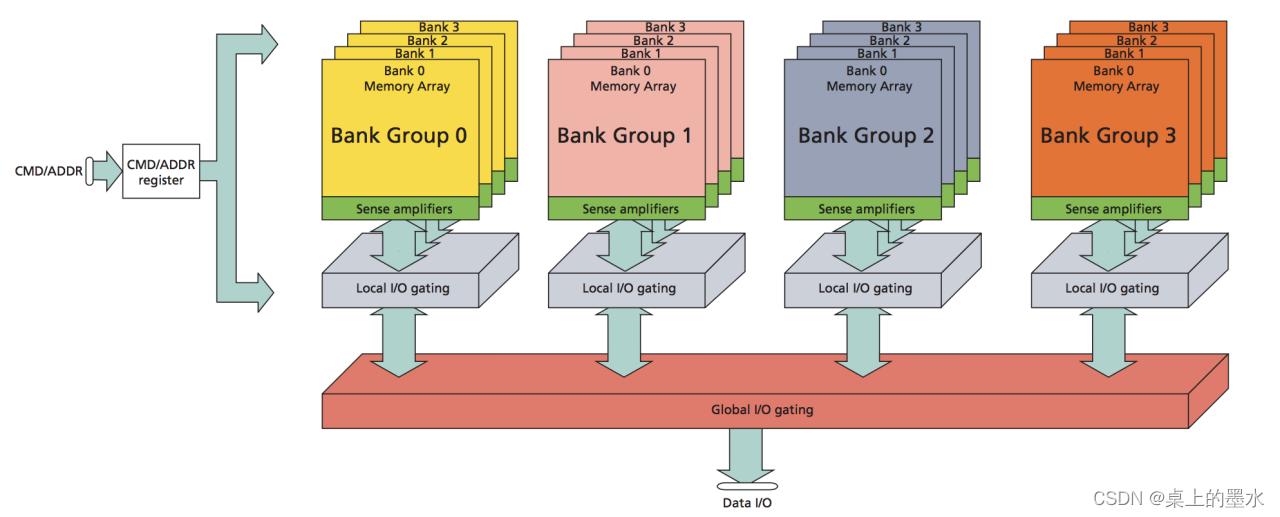

Cells 以特定的方式组成 Column/Row/Bank/Chip/Rank/DIMM/Channel等多层级组织结构如下图:

图1 - DRAM的组织结构

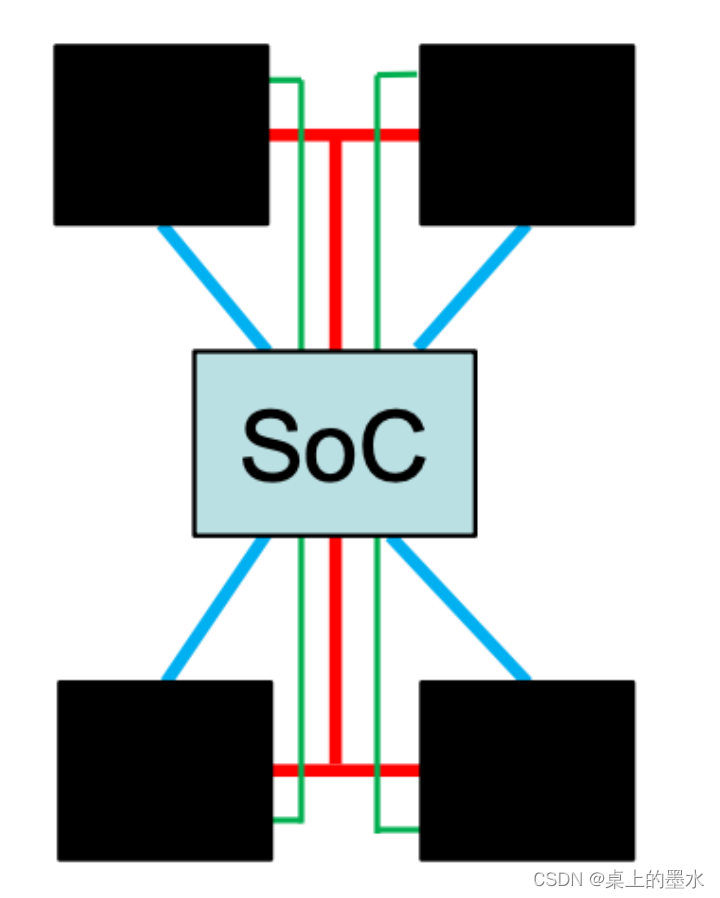

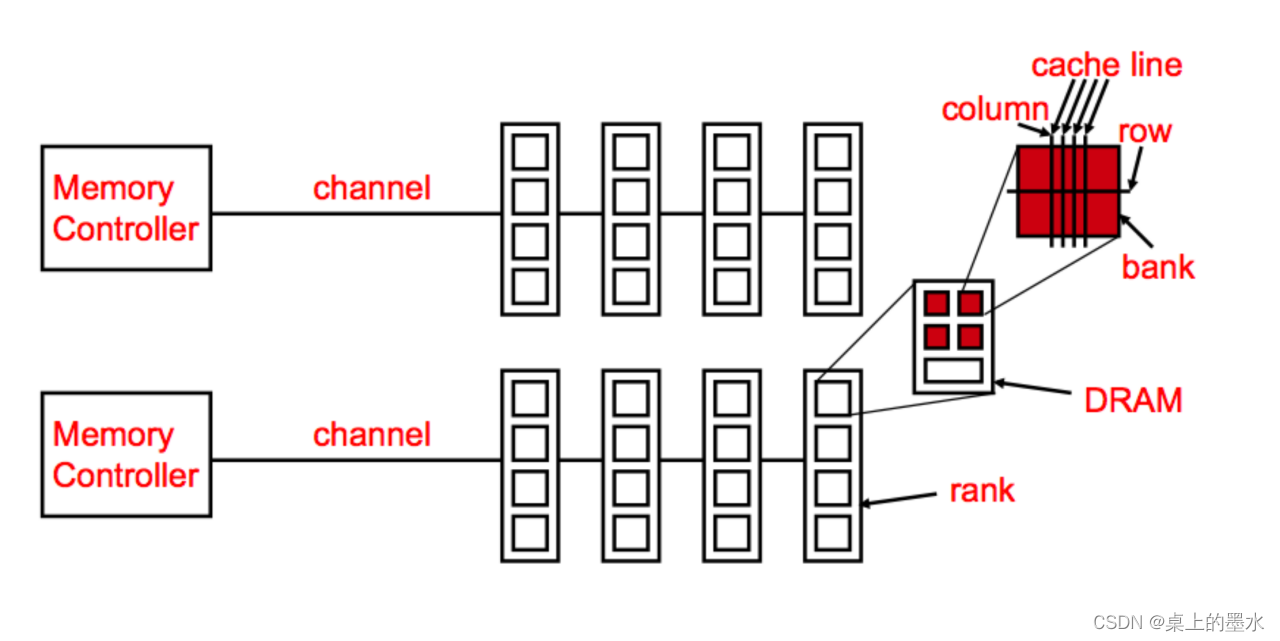

图2 - DRAM容量的组织结构图

Channel: 同1个DDR控制器

DIMM: Dual in-line memory module(2 sides)

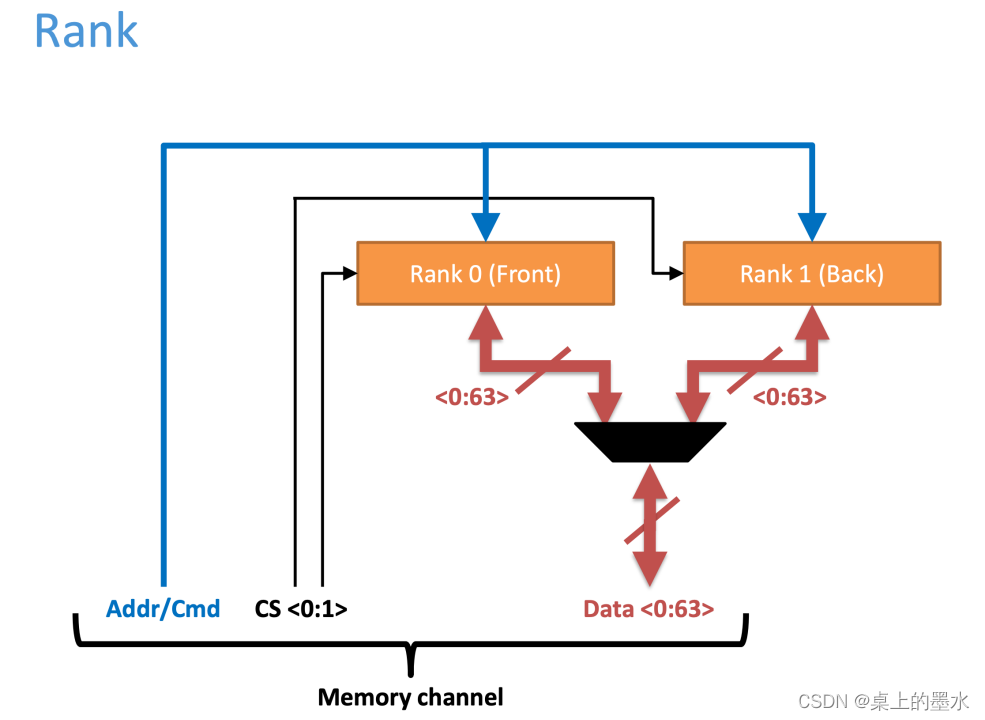

Rank:同1个地址(diff CS)

CHIP:diff data

1.1 Columns(最小可寻址单元)

Column 是 Memory Array 中可寻址的最小单元。

Column Size:1个Column上所含 Cells 数量,与 Data Width 相同。

Memory Array的Data Width 是指对该 Array 进行一次读写操作所访问的 Bit 位数。这个位数与 CSL 和 WE 控制线的组织方式有关。

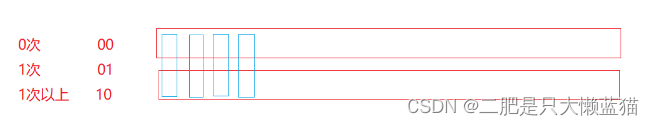

增加 Bitline 后,Sense Amplifier、Read Latch 和 Write Driver 的数量也相应的增加了,这意味着成本、功耗、芯片体积都会随着增加。由于这个原因,在实际的设计中,会优先考虑增加 Bitline 上挂接的 Cells 的数量,避免增加 Bitline 的数量,这也意味着,一般情况下 Wordline 的数量会比 Bitline 多很多。

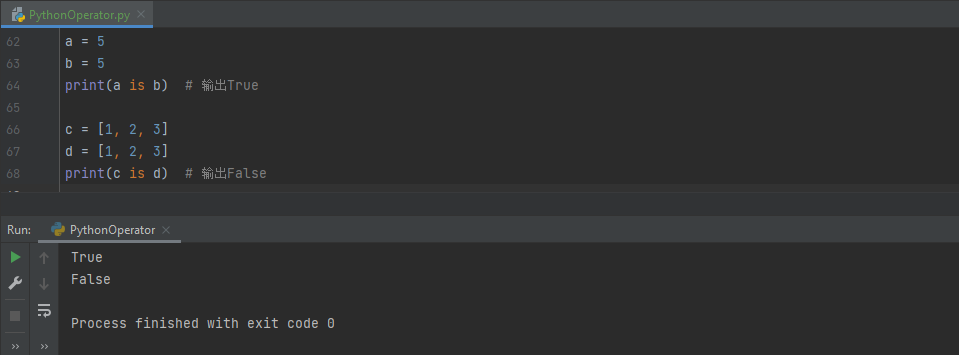

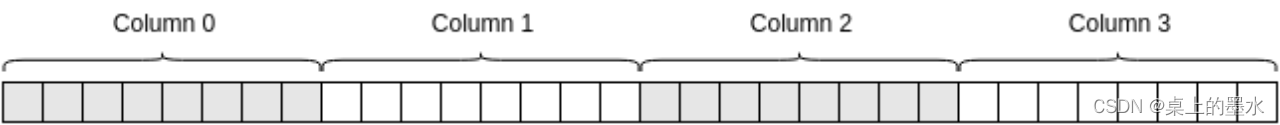

1.2 Rows(含多个columns)

Row 与 Wordline 是一一对应的,1个 Row 本质上就是所有接在同1根 Wordline 上的 Cells,如下图所示。

Row Size:即为1个 Row 上面的 Cells 的数量。

1个 Row 中有 n 个 Column,其中 n = Row Size / Data Width。

例如,下图是 Row Size = 32,Data Width(column size) =8 的示例。

图2 - row size & coulumn size

DRAM 在进行数据读写时,选中某1 个Row,实质上就是控制该 Row 所对应的 Wordline,打开 Cells,并将 Cells 上的数据缓存到 Sense Amplifiers 上。

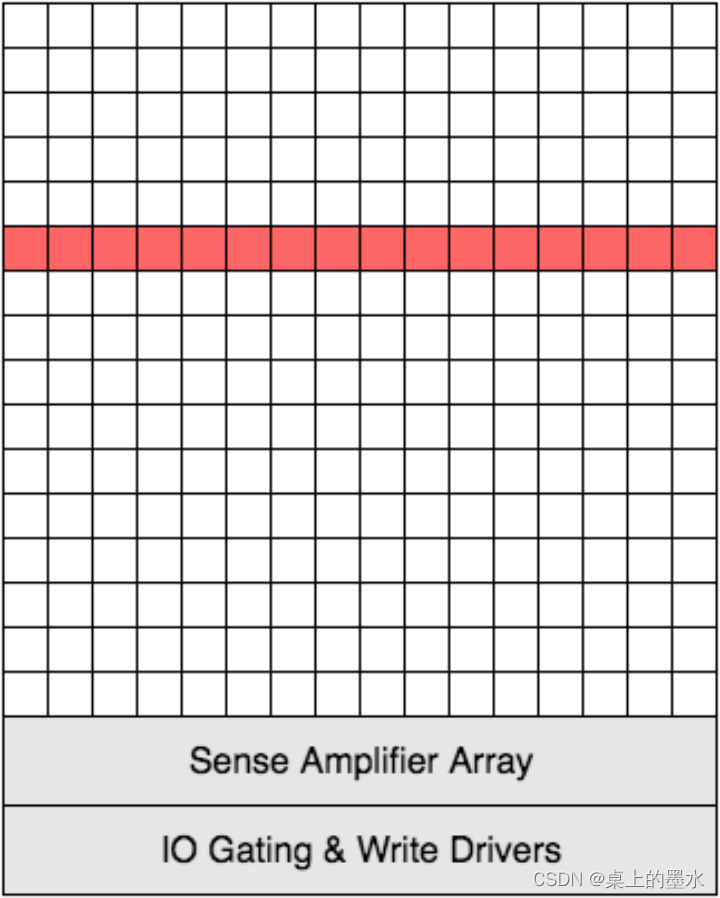

1.3.BANK(memory array:含多个Rows)

图3 - Array

1.4 CHIP:由多个bank组成的chip(含多个banks)

图4 - CHIP组织结构

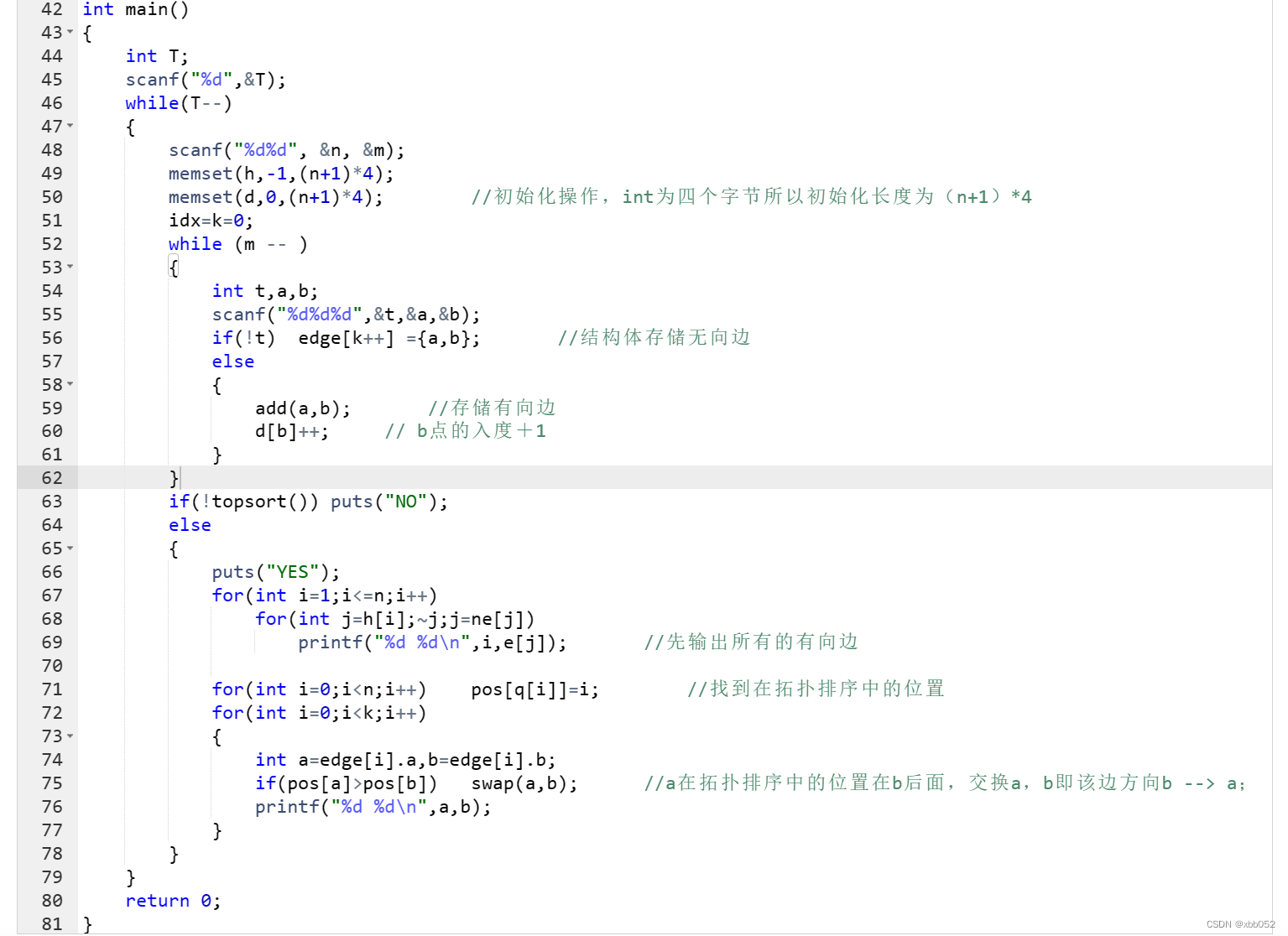

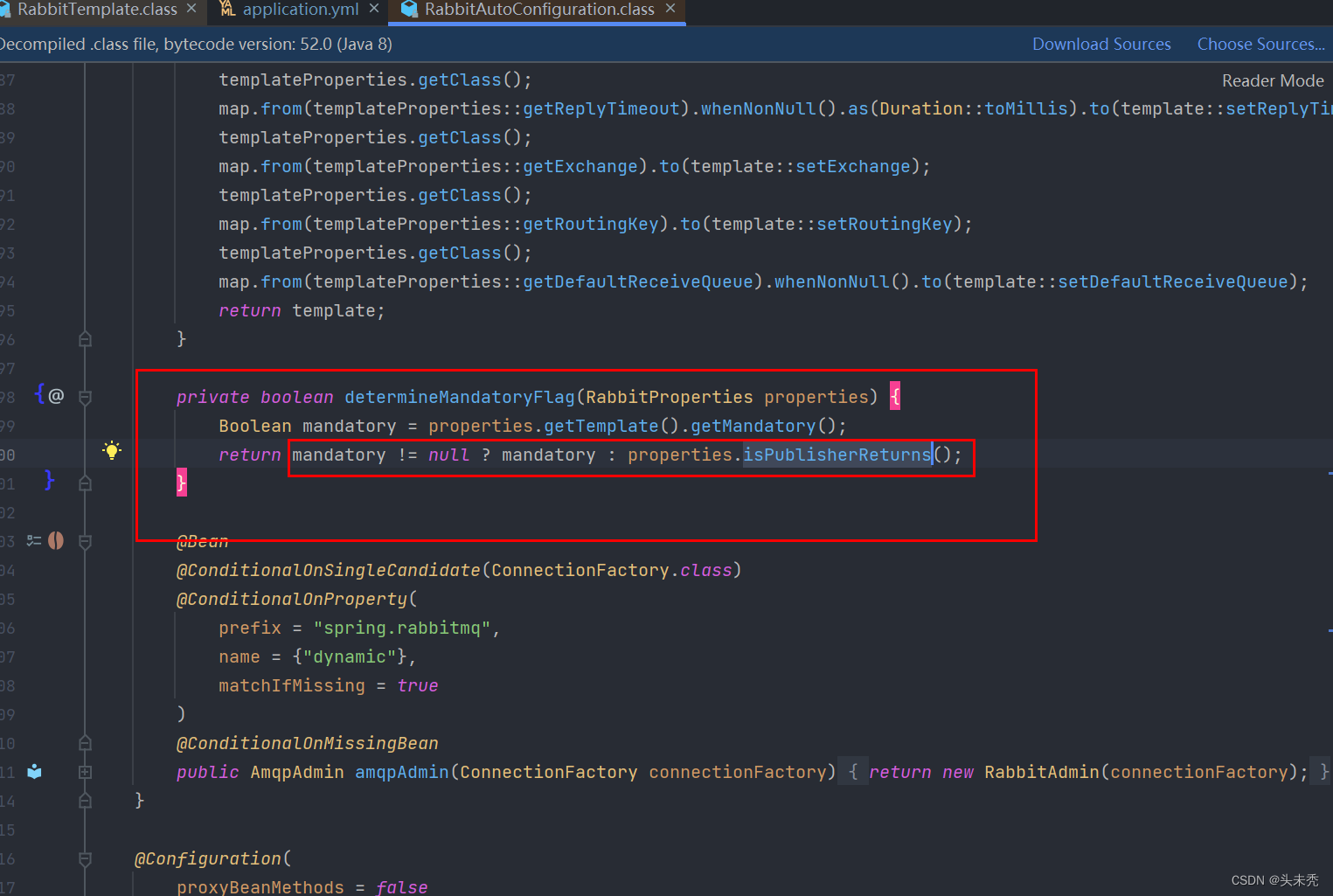

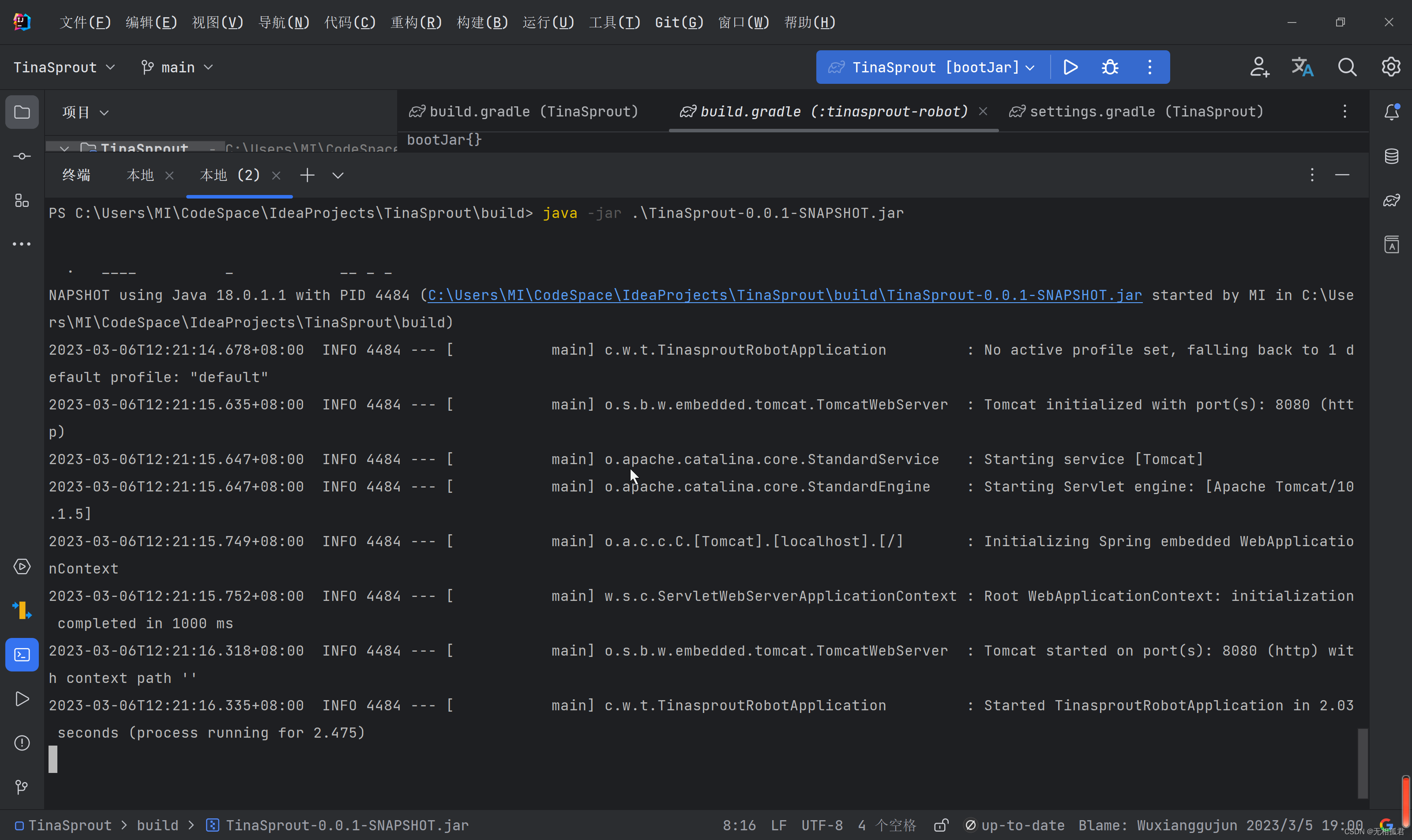

- DDR device的连接关系

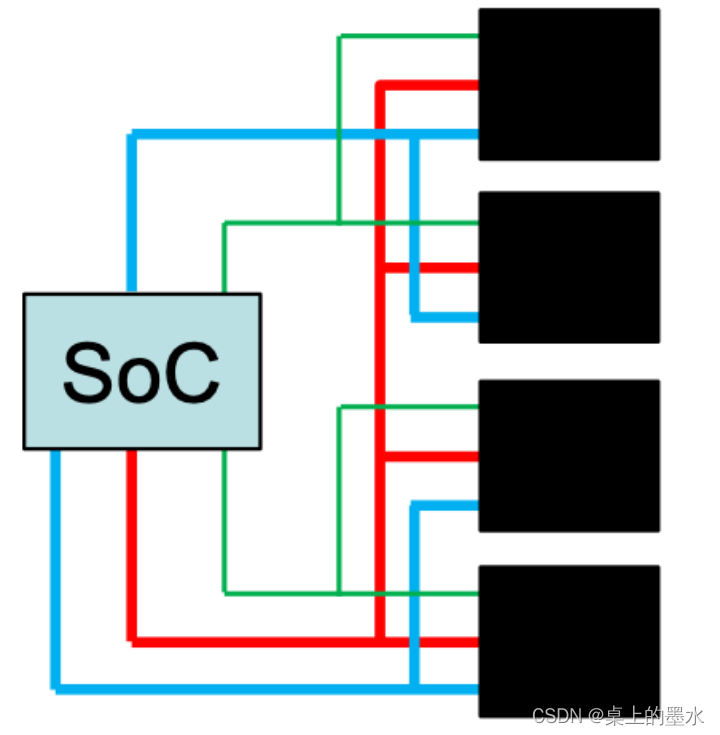

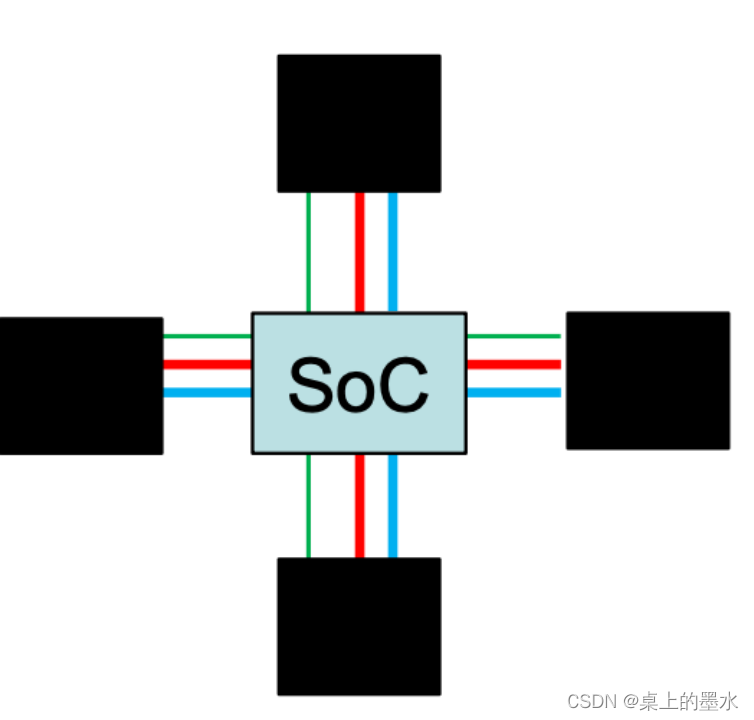

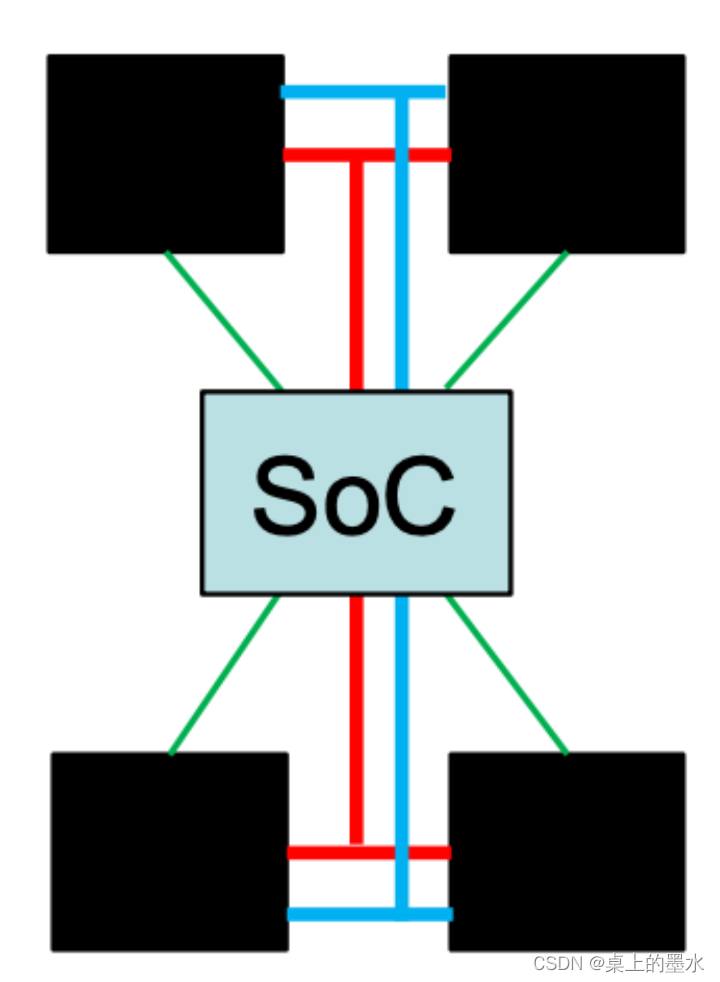

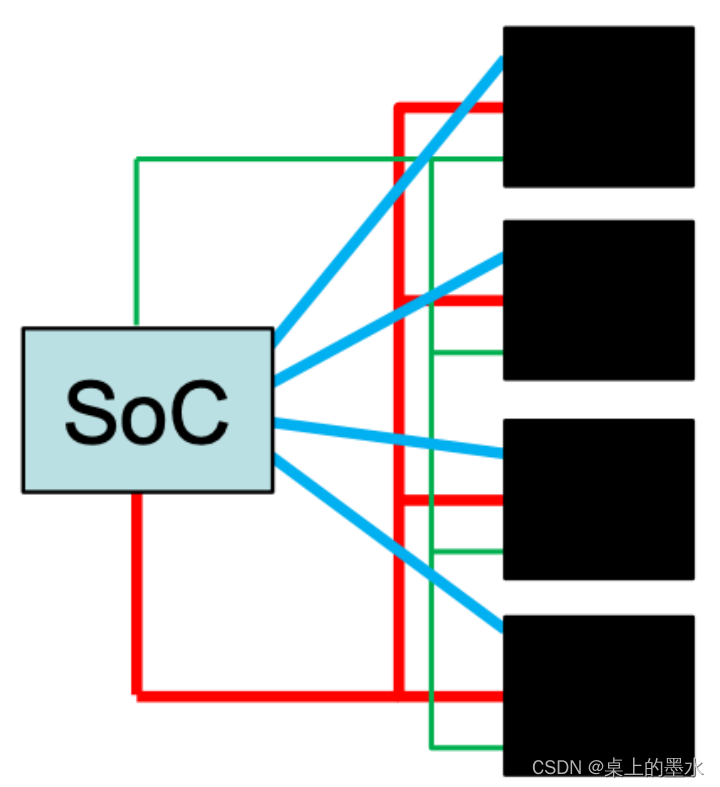

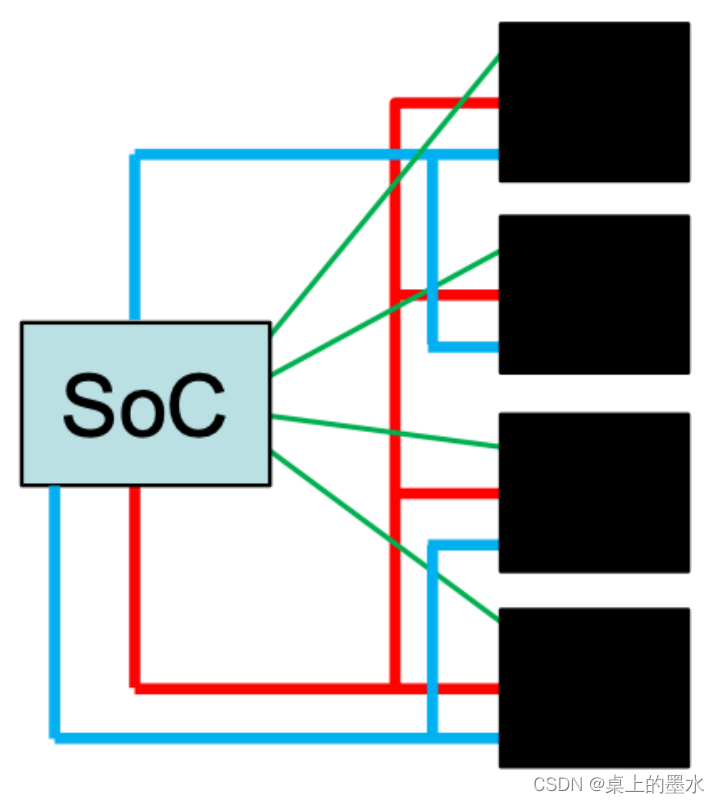

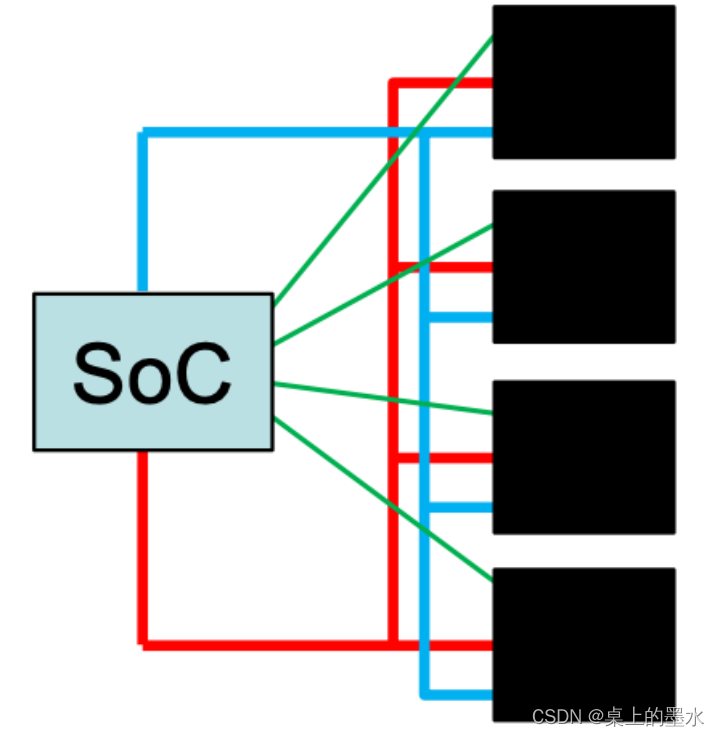

如下图,不同的CA/CS/DQ连接关系,可以练成不同的memory结构,对应的读写效率也不同。

组成1个Rank结构的例子

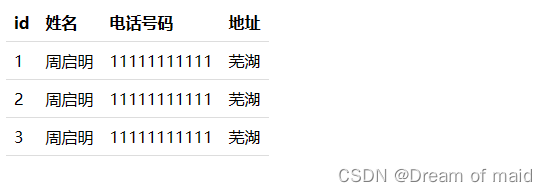

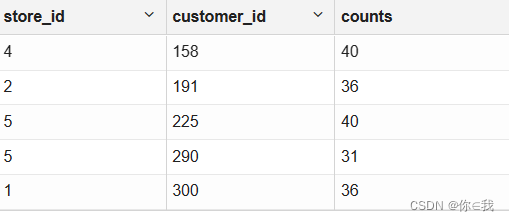

2.1 2个DRAM容量的连接关系

1个LPDDR4的2个channels( 与controller channels不同),相当于2个lpddr2颗粒。

图2.1 2个颗粒的连接方式

如果1个LPDDR4颗粒(2 channels)有4种连接关系(CA(命令/地址)):

| NO | 连接方式 | 共享 | 不同 | 备注 | |

| 1 | Parallel (lockstep) | CA,CS | DQ | 所有颗粒同时被访问: 1.PoP实现困难;2.低bank利用率;3.64Bytes fetch | |

| 2 | Series (多Rank) | CA,DQ | CS | 不同CS区分访问不同颗粒: 1.PoP实现困难;2.其他方案带宽的一半;3.省DQ pins | |

| 3 | Multi-channel | CA,DQ,CS | 都是独立的连线 | ||

| 4 | Share-CA | CA | DQ,CS | 两个DRAM设备接收相同的命令&地址,但只有一个设备被访问主动芯片选择一次,所以每个DRAM设备 |

这里的并行/串行指数据DQ并行/串行。

2.2 4个DRAM容量的连接关系

如果是2个LPDDR4的4 channels.

|

|

|  |

| 4 Channel(suggested) CA pins: 24 DQ pins: 64 CS pins: 4 Banks: 32 Fetch: 32 | 2 Channel & Parallel(suggested) CA pins: 12 DQ pins: 64 CS pins: 2 Banks: 16 Fetch: 64 | 4 Channel & Shared-CA CA pins: 12 DQ pins: 64 CS pins: 4 Banks: 32 Fetch: 32/64 | 2 Channel & Serial CA pins: 12 DQ pins: 32 CS pins: 4 Banks: 32 Fetch: 32 |

|

|  |  |

| Parallel CA pins: 6 DQ pins: 64 CS pins: 1 Banks: 8 Fetch: 128 | Complicated CA pins: 6 DQ pins: 32 CS pins: 2 Banks: 16 Fetch: 32/64 | Complicated CA pins: 6 DQ pins: 32 CS pins: 2 Banks: 16 Fetch: 32/64 | Serial CA pins: 6 DQ pins: 16 CS pins: 4 Banks: 32 Fetch: 32 |

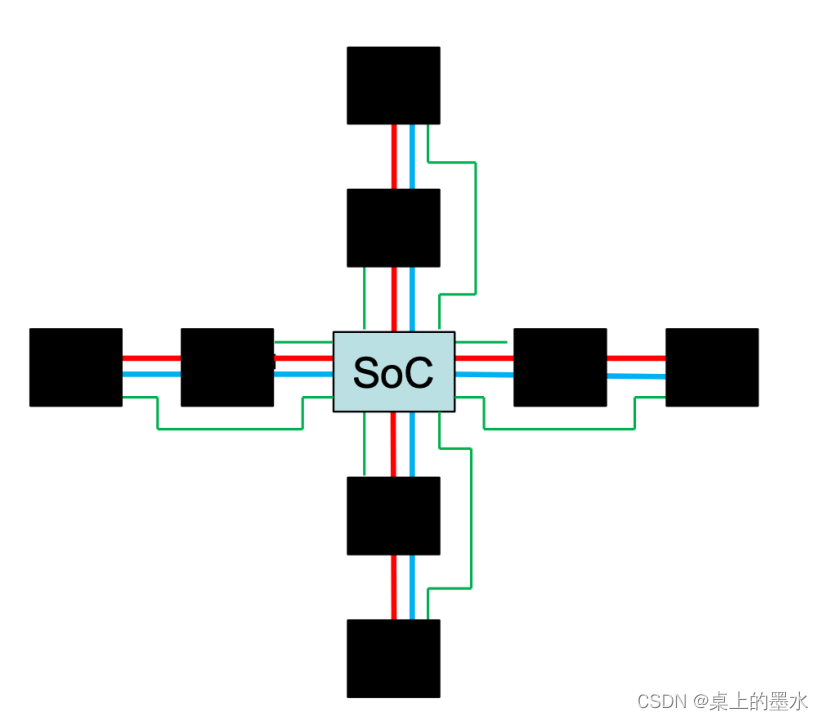

2.3 8个DRAM容量的连接关系

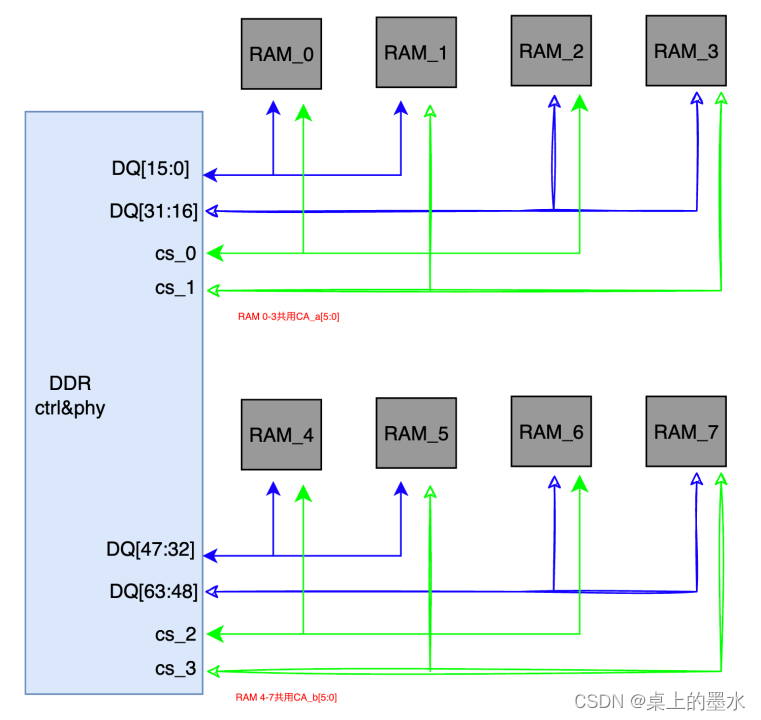

如果是4个LPDDR4的8 channels ,更多的选择,推荐使用以下2种方式:

方式1: LPDDR4串行实现增加了DRAM容量,此解决方案兼容2 die封装。

方式2: 2个channels, 每个channel(4个RAM) 共享1组CA.其中1个channel 访问4个RAM,另1个channel访问另4个RAM。

参考:

- https://www.jedec.org/sites/default/files/Marc_Greenberg_Mobile_August_2016.pdf