一、简易频率计设计中为什么一定要获取下降沿?

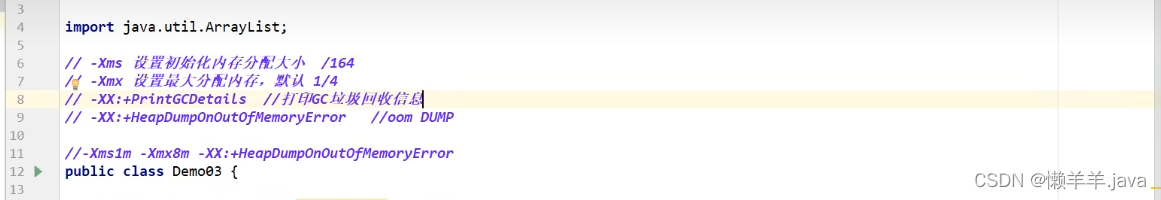

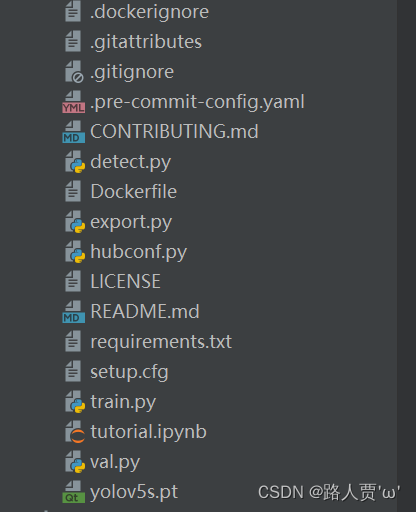

gate_a:实际闸门信号

gate_a_stand:将实际闸门信号打一拍之后的信号

gate_a_fall_s:下降沿标志信号

cnt_clk_stand: Y值,即在实际闸门信号下,标准时钟信号的周期个数

cnt_clk_stand_reg:保存Y值的寄存器

核心问题在:什么时候可以去获取这个Y值?

解决方法:在标准时钟信号下,gate_a为低电平时可以取Y值。

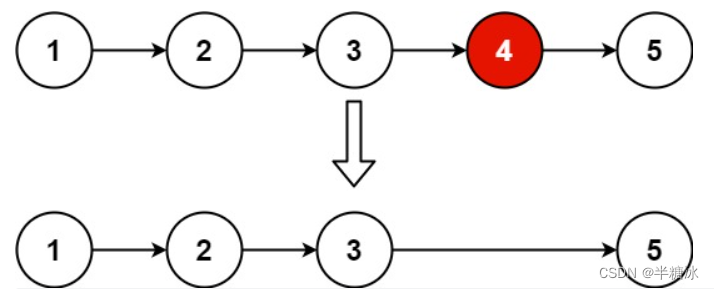

cnt_clk_stand在gate_a为第一个低电平时已经清零(清零的原因是想要为下一次计数做好准备),下一个时钟周期来时再去取Y值就是0了。

所以我们需要一个脉冲式的flag信号,把date_a下降沿取出来,当看到flag信号为高,就开始取数据,由于是脉冲式的,到下一个时钟周期已经自动为低,不会再取Y值了。

所以我们需要这个下降沿标志信号gate_a_fall_s

怎么取这个下降沿?

先把gate_a打一拍得到gate_a_stand,注意是在标准时钟信号下打一拍,使得gate_a与标准时钟信号同步(打一拍不是简单的往后移一个时钟周期),然后用组合逻辑

assign gate_a_fall_stand = ((gate_a_test_reg == 1'b1)&&(gate_a == 1'b0))?1'b1:1'b0;产生一个上升沿与gate_a齐平的一个脉冲信号gate_a_fall_s