目录

- 1、前言

- 2、设计思路和框架

- SDI接收

- SDI缓存写方式处理

- SDI缓存读方式处理

- SDI缓存的目的

- SDI发送

- 3、工程1详解

- 4、工程2详解

- 5、上板调试验证并演示

- 6、福利:工程代码的获取

1、前言

FPGA实现SDI视频编解码目前有两种方案:

一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCRCB,GS2972发送器直接将并行的YCRCB编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;

另一种方案是使用FPGA实现编解码,利用FPGA的GTP/GTX资源实现解串,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA水平要求较高。

本文详细描述了FPGA纯verilog编解码SDI视频的实现设计方案,工程代码编译通过后上板调试验证,文章末尾有演示视频,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

本设计提供两套vivado工程;

工程1:

SDI 1080P@30Hz帧视频输入解码后,经DDR3缓存,SDI发送1080P@30Hz帧输出;

工程2:

FPGA内部生成测试彩条视频,SDI发送出去,SDI接收后无缓存HDMI输出;

关于SDI的理论知识部分,可自行搜索一下,很多大佬讲得很详细,也可以参考我之前写的文章点击查看:SDI理论

2、设计思路和框架

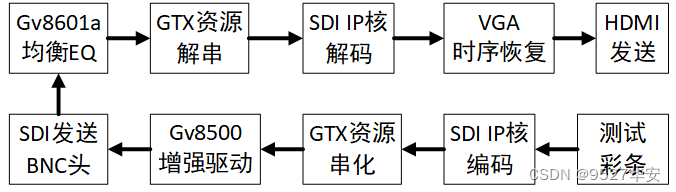

设计思路和框架如下:

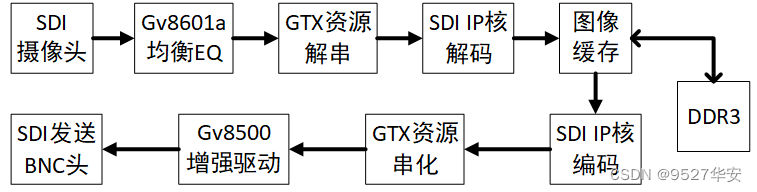

SDI经DDR3环出工程设计思路如下:

SDI接收

SDI解码部分之前写过一篇文章详细描述了,这里不再赘述,请参考我之前写的文章点击查看:SDI解码

这里重点将SDI图像缓存和发送部分:

SDI缓存写方式处理

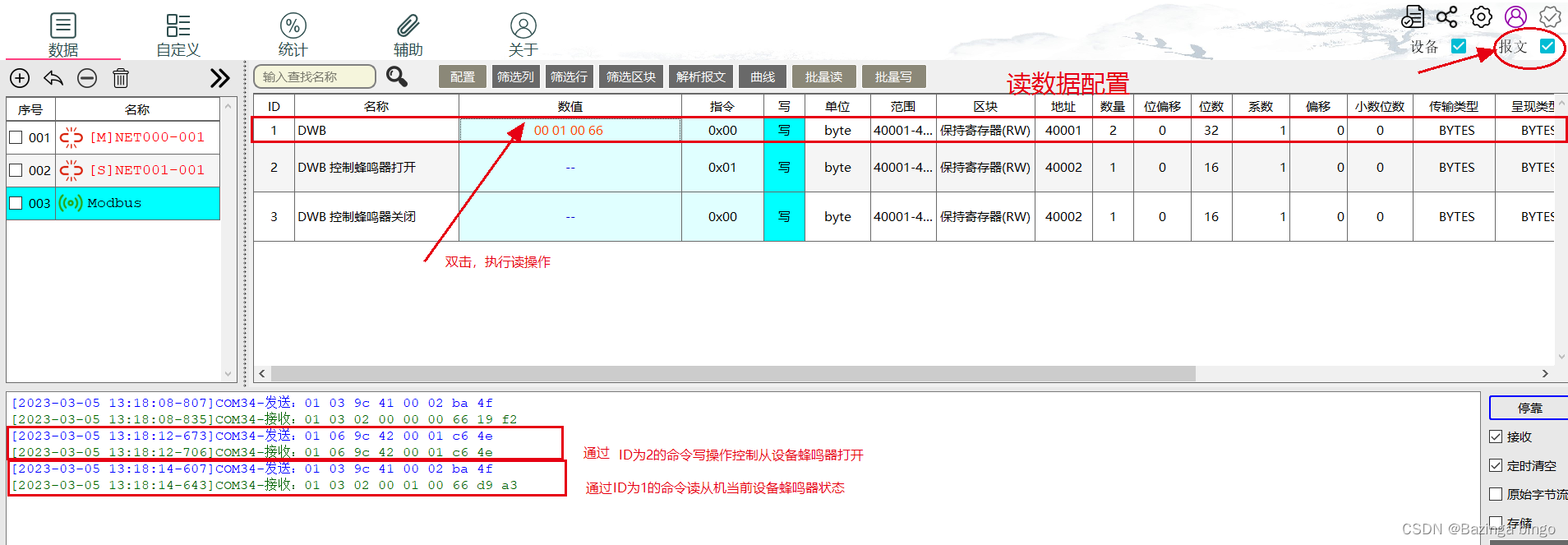

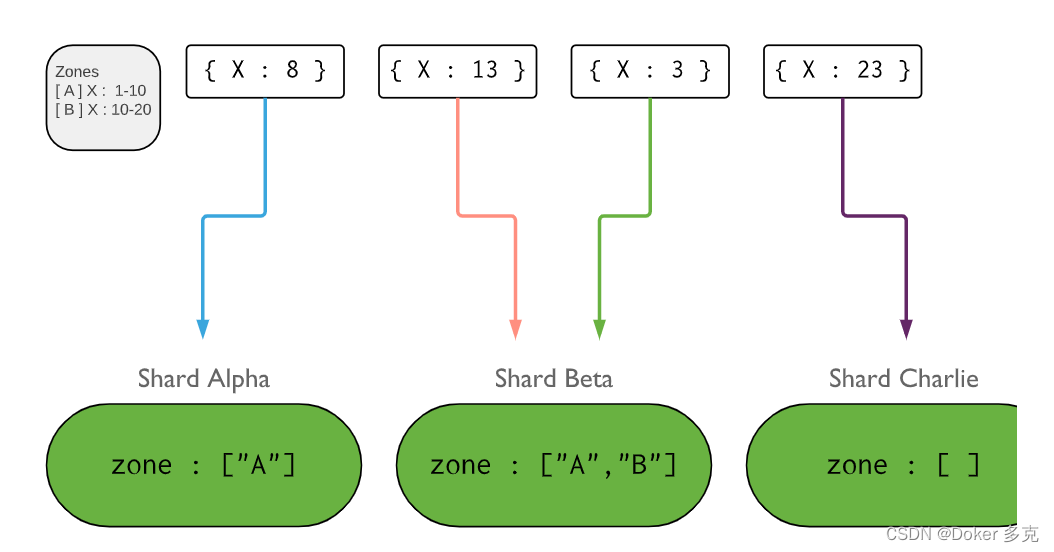

SDI 接收解串后,把 20 位数据,异步 FIFO 方式,8 个数据一起打包成并行数据,送入 DDR3。通过 rx_usrclk 时钟送入 20 位到 FIFO,然后再用 DDR 的 ui_clk 时钟,把 8 个数据并行送入DDR3。每帧数据满了后,我们就把帧号加 1,即 ddr3_addr_bank_wr 变量加 1,这样使得我们在 DDR3 内存颗粒放置了3帧数据。

SDI缓存读方式处理

通过ui_clk,一个时钟读出 8 个 SDI 数据,送入 FIFO,通过异步方式,也就是通过 tx_usrclk时钟,读出 1 个 sdi 数据,也就是 20bit 的 sdi 数据。每读满一帧,我们就通过ddr3_addr_bank_rd <= ddr3_addr_bank_wr ‐2’b1;方式,让读帧号跟随着写帧号。

SDI缓存的目的

rx_usrclk 时钟是来自信号源,但是 SDI 发送必须要使用本地晶振,也就是硬件上连接到GTX 的参考时钟晶振。由于时钟的不同源,所以我们不能把接收的信号源直接送到 SDI 发送引擎上去,必须要经过 DDR 方式做帧处理才能做 SDI 环出。

SDI发送

SDI发送是SDI接收的逆过程,即使用SDI IP编码将视频数据编码为SDI格式,再使用GTX将并行SDI数据串化为高速串行数据通过GTX发送出去,经过GV8500增强驱动后给到SDI发送的BNC座子。

SDI发送接收彩条视频工程设计思路如下:

FPGA内部生成3G-SDI彩条视频,不缓存,直接经前文介绍的SDI发送通路发送出去,再经前文介绍的SDI接收通路后送HDMI输出显示。

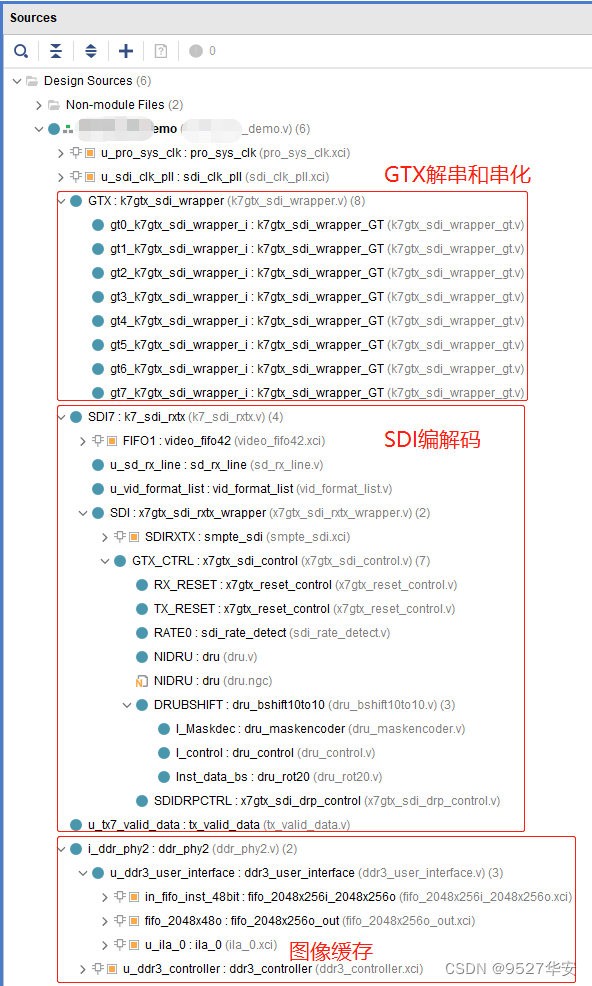

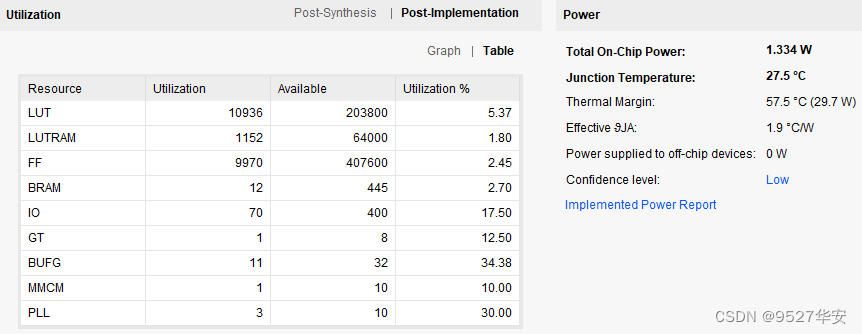

3、工程1详解

开发板:Xilinx Kintex7开发板;

开发环境:Vivado2019.1;

输入:SDI摄像头,分辨率1080p@30帧;

输出:SDI,分辨率1080p@30帧;

工程代码架构如下:

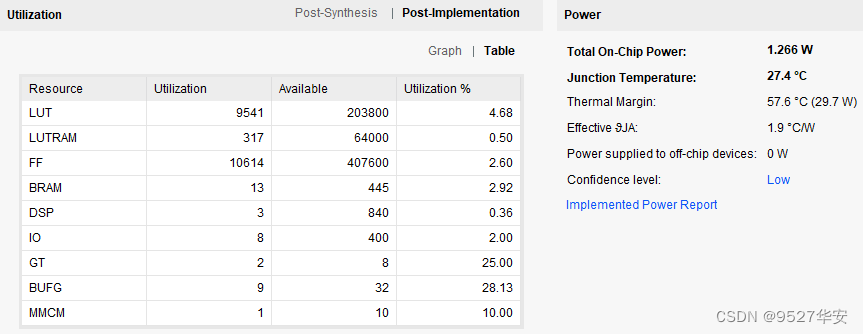

资源消耗和功耗预估如下:

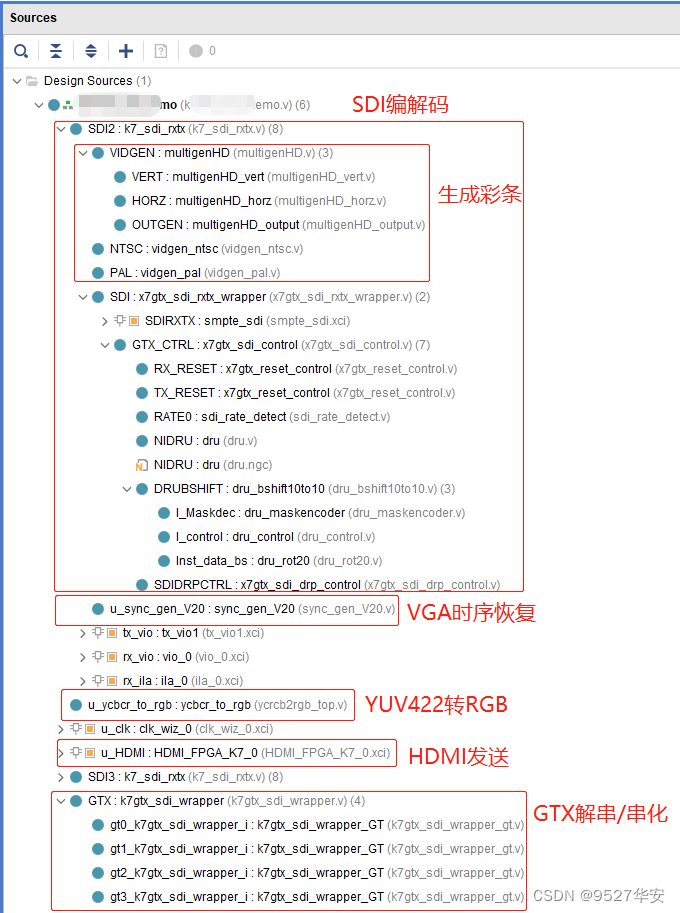

4、工程2详解

开发板:Xilinx Kintex7开发板;

开发环境:Vivado2019.1;

输入:FPGA内部生成彩条,分辨率1080p@30帧;

输出:HDMI,分辨率1080p@30帧;

工程代码架构如下:

资源消耗和功耗预估如下:

5、上板调试验证并演示

演示视频如下:

FPGA实现SDI视频解码SDI发送,提供2套工程源码和技术

6、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

![[一篇读懂]C语言十一讲:单链表的删除和单链表真题实战](https://img-blog.csdnimg.cn/9316603659cc4974993d65ce035aa358.png#pic_center)