前言

在嵌入式底层系统中,常见的通讯方式,串口,IIC,SPI,IIS等,一般IIC,SPI,IIS更多的采取IO模拟,其余CAN,UART均是硬件设计直接支持,而IIC主要用于多数传感器数据的读写,IIS更多用于语音驱动,SPI则用于传输要求较快的场景,如图像传输等,本文则着重阐述作者认知中的IIC,以及相关的实例和实际过程中的细微处理等,有机会和时间再慢慢写其他。

硬件设计注意

一般来说IIC主要有两根主要的线,SDA和SCL(去除电源相关的VCC和GND),硬件设计过程中SDA和SCL注意做上拉处理,电阻的选值在一定基础上也会影响到整体的通讯速率。

IIC的基础规则

1.基本约定

(1)总线上主和从、发和收的关系不是恒定的,而取决于此时数据传送方向。如果主机要发送数据给从器件,则主机首先寻址从器件,然后主动发送数据至从器件,最后由主机终止数据传送;如果主机要接收从器件的数据,首先由主器件寻址从器件.然后主机接收从器件发送的数据,最后由主机终止接收过程。在这种情况下.主机负责产生定时时钟和终止数据传送。

(2)通常来说IIC设备一般会存在一个设备编号,用于区分相关的设备,占7个bit,最后一个bit作为此次操作的读写处理位,最后一个bit为0表示写,为1表示读取(此处顺序是从高数据到低数据算的),例如51H—>0101 0001,当我们要写入数据的时候需要传输1010 0010 也就是A2H数据。

(3)发送到SDA 线上的每个字节必须为8 位,每次传输可以发送的字节数量不受限制。每个字节后必须跟一个响应位。首先传输的是数据的最高位(MSB),如果从机要完成一些其他功能后(例如一个内部中断服务程序)才能接收或发送下一个完整的数据字节,可以使时钟线SCL 保持低电平,迫使主机进入等待状态,当从机准备好接收下一个数据字节并释放时钟线SCL 后数据传输继续。

(4)规定,只允许SCL为高的时候,SDA的数据有效传输,也就是说我们在SCL为低的时候修改SDA的电平去表示你要传输的bit电平,修改稳定后我们将SCL拉高,另一个设备读取到SCL高的时候会去采样SDA的电平,注意这里的措辞是稳定,根据选型的芯片和通讯要求等,一般会做一定的延时,具体可以看相关的设备的手册。

(5)IIC是一个半双工,这是由其数据性决定的,SDA作为数据的主要传输线路,不可能同时传输两端数据。

2.IIC的基本传输流程

IIC根据SCL和SDA的线路情况将通讯的状态分为以下几种,空闲状态(IDLE状态),起始信号(START信号),确认信号(ACK/NACK),停止信号(STOP信号),相对实际通讯过程中,我们会多加几个通讯流程,数据传输阶段,等待确认信号。

3.相关传输流程的SCL和SDA的处理

以下会做一个简单的通讯过程的说明,以程序设计流程为示例,注意以下过程修改引脚的时候注意电平转换一般需要延时时间

空闲态:一开始没有数据传输的过程中会处于空闲态,SDA=SCL=1,两者均保持高电平,从一种角度上来说为什么建议加上拉,从抗干扰层次说也是,如果做键盘扫描没有加上拉的话,可能会体会更深,从软件上来说浮空就是1,但是实际上要从EDA设计角度来说,一般会认为是X,未知态。

起始信号:SCL=1,SDA-=1>SDA=0,当SCL为高的时候SDA由高为低,下降沿,从设计的角度来说,数据的传输必然是起始开始的,之所以设定在SCL高的时候,让SDA为0表示起始信号,个人理解是这样是设计让数据变化更快,只需要更改一根线的电平,可以参考格雷码的存在意义,起始信号一般是空闲态转后的状态。

数据传输:第一个传输的是地址+读写标志位组成的8bit数据,当起始信号的存在被检测后,将SCL=0,然后修改对应的SDA,认为SDA引脚稳定表达你想要的逻辑电平后,SCL=1,另一个设备检测到SCL为1后会开启采样,给予另一个设备足够的采样时间采用SDA,这样就完成1bit的传输。

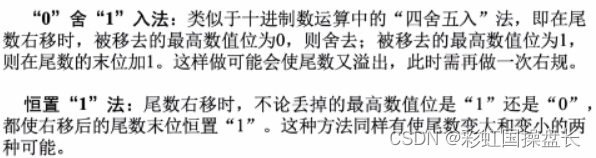

ACK/NACK:当完成如上的8个bit数据传输后,设备会等待接收到数据的响应信号,当接收到数据的设备已经发完或者异常情况(常见的异常,请见下面补充),或者没有传输完成则会表示ACK让你进行下一步操作,告诉你已经做完一个数据步骤,ACK:SCL高电平时,SDA为低电平,NACK:SCL高电平时,SDA为高电平,按照个人理解的话,常见的程序存在两种,一种是不管直接进行下一个步骤就进行ACK判断,一种是会将释放SDA的控制,SCL=0,SDA=1,SCL=1,让另一个设备去拉低SDA来排除最后一个字节发送为0的时候的区分,作为等待ACK或者NACK的程序设计,NACK和空闲的状态表示一样。

停止信号:SCL=1,SDA=0–>SDA=1在SCL为高电平时,SDA上升沿。以停止信号作为整个程序的指令的结束。

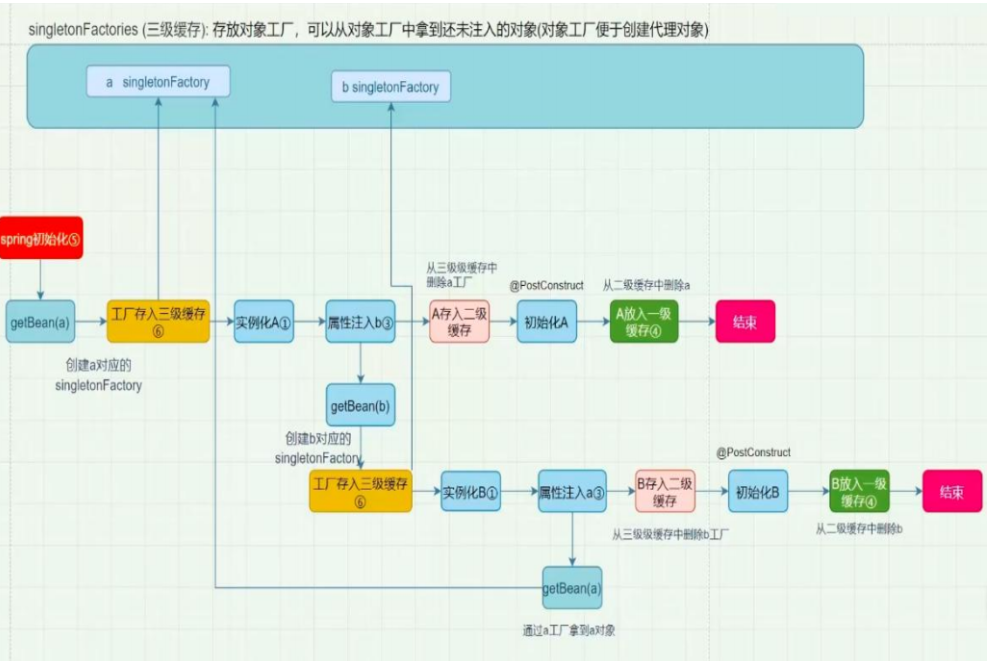

具体事例流程说明

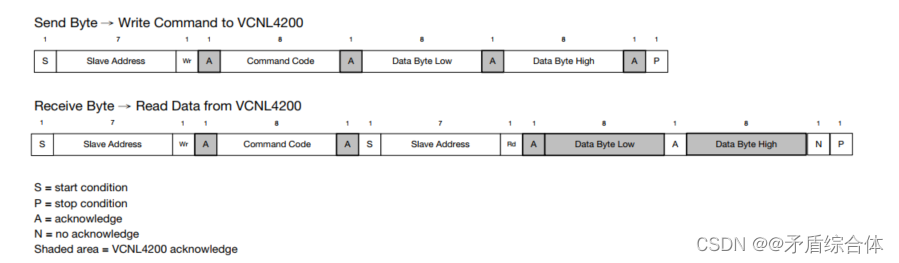

上图是VCNL4200传感器的协议流程图,采取的官方数据手册,白色是主设备做的,深色是VCNL做的。

1.先初始化IO口,对于我们来说SCL必然是我们一直控制的,做为主设备,设置输出,也可以将SDA=1做为输出,进入空闲态。

2.如图的第一个表示的是写数据,开始信号,由空闲进入开始,开始信号的要求是SCL的时候SDA一个下降沿,我们可以直接将SDA拉低即可。

3.传输数据地址,VCNL4200的地址是51H,通过上面的示例得到,我们写的时候变成了A2H,将SCL拉低,然后SDA拉高,后再将SCL拉高,如此处理8个bit。

4.进入等待阶段ACK阶段,按照上面的两种方式中的一种即可

5.后面同2-4,知道P阶段,先在SCL为低的情况下,拉低SDA,然后将SCL=1,SDA=1,产生一个上升沿作为结束。

6.对于读取来说,不一样的就是从设备读取的过程,在这个过程中仍然是主设备控制SCL,我们会释放SDA,将SCL拉低,给予从设备一段时间,然后其去修改SDA的电平,然后我们读取SDA的逻辑电平,用于表示读取到的bit数据,在读取到8bit数据后给予ACK或者NACK反应。

补充:

通讯过程中出现以下情况,总线上会出现NACK信号:

1)接收方忙于其他事情,不能接收数据

2)接收方不能理解收到的数据或者没有空间存储数据

3)主机读取数据完成,返回NACK告知从机读取完成。