日期:20230228

规范分类

根据 RISC-V 设计哲学,其规范文档也是高度模块化的:

ISA 规范(2 篇)

- 非特权规范

- 特权规范

非 ISA 规范(6篇)

- Trace规范

- ABI 规范

- 外部调试规范

- PLIC 规范

- SBI 规范

- UEFI 协议规范

以及其他未合并的扩展规范,目前不是重点

| ISA | none-ISA | |

| 正式审批 | Volume 1, Unprivileged Specification version 20191213 [PDF] Volume 2, Privileged Specification version 20211203 [PDF] | 表 2,6 个规范 |

| 审批未集成 | 见表 3,16 个扩展 | RISC-V Non-ISA Specifications · GitHub |

| 进行中 | Specification Status - Home - RISC-V International (riscv.org),20+ | |

| Specification name | Version | Publish Date | Description | RISC-V Community | Source Repository |

|---|---|---|---|---|---|

| Efficient Trace for RISC-V | 2.0 | June 2022 | Specifies the signals between the RISC-V core and the encoder, compressed branch trace algorithm, and the packet format used to encapsulate the compressed branch trace information to implement processor tracing. | SOC Infrastructure Horizontal Committee | riscv-non-isa/tech-trace-spec |

| RISC-V ABIs Specification | 1.0 | November 2022 | Provides the processor-specific application binary interface document for RISC-V | Application & Tools Horizontal Committee | riscv-non-isa/riscv-elf-psabi-doc |

| RISC-V External Debug Support | 0.13.2 | March 2019 | Outlines a standard architecture for external debug support on RISC-V platforms. | SOC Infrastructure Horizontal Committee | riscv/tech-debug-spec |

| RISC-V Platform-Level Interrupt Controller Specification | 1.0.0 | February 2023 | Delineates the operational parameters for a platform-level interrupt controller on RISC-V. | Privileged Software Horizontal Committee | riscv/riscv-plic-spec |

| RISC-V Supervisor Binary Interface Specification | 1.0.0 | May 2022 | Describes the RISC-V Supervisor Binary Interface, known from here on as SBI which enables supervisor-mode (S-mode or VS-mode) software to be portable across all RISC-V implementations by defining an abstraction for platform (or hypervisor) specific functionality. | Privileged Software Horizontal Committee | riscv-non-isa/riscv-sbi-doc |

| RISC-V UEFI Protocol Specification | 1.0.0 | May 2022 | Details all new UEFI protocols required only for RISC-V platforms. | Privileged Software Horizontal Committee | riscv-non-isa/riscv-uefi |

| RV32E and RV64E Base Integer Instruction Sets | January 2023 | RV32E/RV64E |

| “Ztso” Standard Extension for Total Store Ordering | January 2023 | Ztso |

| RISC-V Wait-on-Reservation-Set (Zawrs) extension | November 2022 | Zawrs |

| Zmmul Extension | June 2022 | Zmmul |

| PMP Enhancements for memory access and execution prevention on Machine mode (Smepmp) | November 2021 | Smepmp |

| RISC-V Base Cache Management Operation ISA Extensions | November 2021 | Zicbom, Zicbop, Zicboz |

| RISC-V Bit-Manipulation ISA-extensions | November 2021 | Zba, Zbb, Zbc, Zbs |

| RISC-V Count Overflow and Mode-Based Filtering Extension | November 2021 | Sscofpmf |

| RISC-V Cryptography Extensions Volume I: Scalar & Entropy Source Instructions | November 2021 | Zbkb, Zbkc, Zbkx, Zknd, Zkne, Zknh, Zksed, Zksh, Zkn, Zks, Zkt, Zk, Zkr |

| RISC-V State Enable Extension | November 2021 | Smstateen |

| RISC-V "stimecmp / vstimecmp" Extension | November 2021 | Sstc |

| RISC-V Vector Extension | November 2021 | Zve32x, Zve32f, Zve64x, Zve64f, Zve64d, Zve, Zvl32b, Zvl64b, Zvl128b, Zvl256b, Zvl512b, Zvl1024b, Zvl, Zv |

| The RISC-V Instruction Set Manual Volume II: Privileged Architecture | November 2021 | Sm1p12, Ss1p12, Sv57, Hypervisor, Svinval, Svnapot, Svpbmt |

| "Zfh" and "Zfhmin" Standard Extensions for Half-Precision Floating-Point | November 2021 | Zfh, Zfhmin |

| "Zfinx", "Zdinx", "Zhinx", "Zhinxmin": Standard Extensions for Floating-Point in Integer Registers | November 2021 | Zfinx, Zdinx, Zhinx, Zhinxmin |

| “Zihintpause” Pause Hint | February 2021 | Zihintpause |

非特权 ISA 规范

非特权 ISA 规范对硬件平台术语、软件执行环境和 Harts、ISA 概述、内存、指令编码、异常/陷入/中断、非定义行为和数值等进行了简要的介绍。

规范重点描述了 RISC-V ISA 子集:RV32I 32 位整数指令集、RV32E 32 位精简整数指令集、RV64I/RV128I 64/128 位整数指令集、M 整数整除法指令集、A 原子操作指令集、Zicsr 控制状态寄存器、F 单精度浮点指令集、D 双精度浮点指令集、Q 双字精度浮点指令集、RVWMO 内存一致性等。

特权 ISA 规范

特权 ISA 规范首先对特权软件栈术语、特权级别、调试模式进行了简要介绍。

其次,对特权模式下的控制状态寄存器进行了介绍。

特权 ISA 分为 M 级别和 S 级别的特权级别。

对于 M 级别,介绍了 M 级别的控制状态寄存器、内存映射寄存器、特权指令、复位、不可屏蔽中断、物理地址属性、物理地址保护。

对于 S 级别,介绍了 S 级别的控制状态寄存器、指令、32/39/48/57 位虚拟内存系统、svnapot 翻译相邻性、svpbmt 基于页内存类型、svinval 小粒度地址转换表内存无效等。

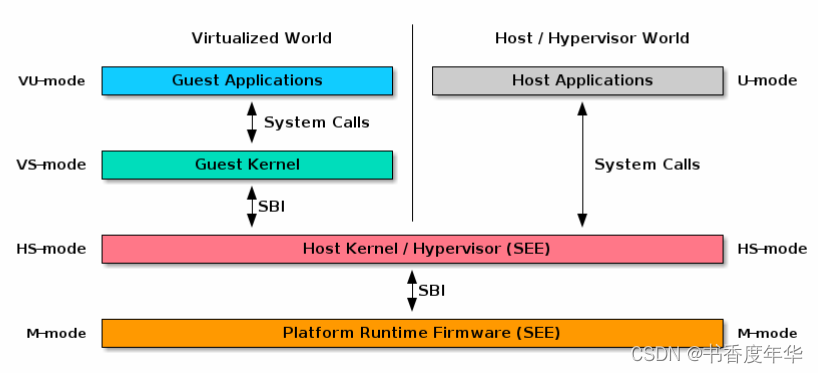

hypervisor 扩展介绍了特权模式、hypervisor和虚拟 S 模式控制状态寄存器、指令、机器级别的控制状态寄存器、两级地址转换、陷入等。

ABI 规范

介绍

本规范为 RISC-V 提供了处理器专用应用二进制接口文档,本规范由以下三部分组成:

- 调用规约

- ELF 规范

- DWARF 规范

该ABI的未来修订版将包括内存模型的规范映射集同步原语。

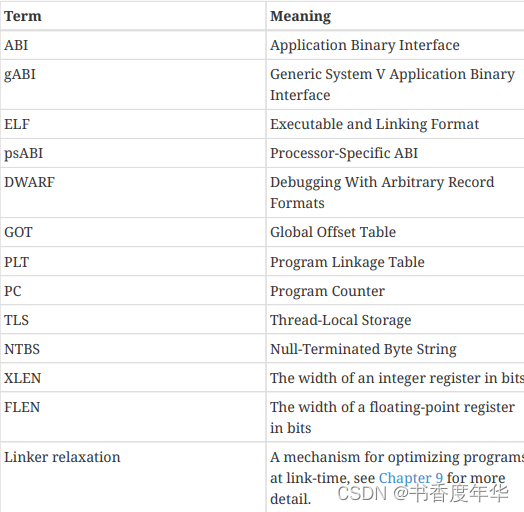

术语缩略语

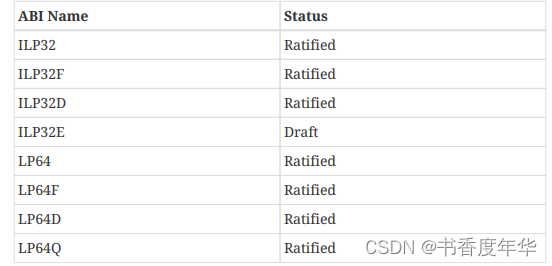

ABI 状态

调用规约

调用规约主要从寄存器约定、过程调用约定、系统调用约定、C/C++ 类型描述、Linux 特定的 ABI 等方面进行了介绍。

寄存器约定:整数、浮点数、向量寄存器的一些约定。

过程调用约定:整数调用约定、硬件浮点调用约定、ILP32E 调用约定、ABI 命名、默认 ABI 等。

系统调用约定:未在本文档中规定,参考 RISC-V execution environment interface (e.g OS kernel ABI, SBI)。

C/C++ 类型描述:类型大小和对齐方式、类型表示、va_list/va_start/va_arg。

Linux 特定 ABI:类型大小和对齐方式、类型表示。

PLIC 规范

PLIC 指的是平台级别的中断控制器,PLIC 规范主要从以下几个方面进行了介绍:

- 中断目标和 Hart 上下文、中断网关、中断通知、中断号、中断流程

- PLIC 操作参数

- 内存映射

- 中断优先级

- 中断等待状态位

- 中断使能

- 中断阈值

- 中断声明过程

- 中断完成

SBI 规范

这个规范描述了 RISC-V 超级二进制接口,即SBI,通过 SBI 接口, RISC-V 能够实现 S 模式、VS 模式代码能够在不同的平台之间的可移植性。SBI 遵循了 RISC-V 的设计哲学,由一个非常小的核心部分和一些可选的模块扩展组成。

SBI 整体来说是一个扩展,也就是说要不实现,要么就要完整实现。如果 sbi_probe_extention 指示出某个功能可用,那么所有版本要求的功能都需要实现,这个版本可以通过 sbi_get_spec_version 来获得。

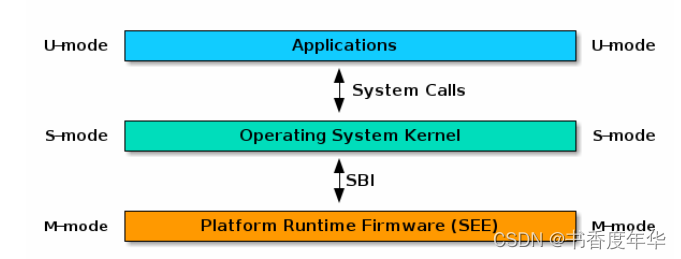

高特权软件向管理模式提供 SBI 接口支持,这个软件可以叫做 SBI 实现或者 SEE。SEE 可以是图1中的 M 模式下运行时固件,也可以是图2 中的 HS 模式运行的虚拟机管理程序。

SBI 规范不会指定任何硬件发现的方法,S 模式软件必须通过其他工业标准来获取,比如 Device Tree 或者 ACPI。

UEFI 协议规范

设备树(DT)或高级配置和电源接口(ACPI)配置表用于向操作系统传达有关硬件的信息:一些

只有在启动时才知道信息,并且在操作系统或者引导器启动之前很早就需要这些信息来解析固件表。

一个例子是 RISC-V 系统上的引导 hartid。在非 UEFI 系统上,这通常作为内核的参数(在 a0中),但是,UEFI 系统需要遵循 UEFI 应用程序调用,因此不能在 a0 中传递。有一个现有的解决方案使用 DTS 中的 /chosen 节点传递此信息。然而,此解决方案不适用于基于 ACPI 的系统,因此,UEFI 协议对于基于 DT 和 ACPI 的系统都是优选的。

RISC-V 系统的 UEFI 协议为引导加载程序或操作系统提供早期信息系统。EDK2 和 u-boot 等固件需要在 RISC-V UEFI 系统上实现该协议。

该协议通常由引导加载程序在调用 ExitBootServices()之前调用。然后他们通过将信息发送给操作系统。

本规范规定的 RISCV_EFI_BOOT_PROTOCOL 版本为 0x00010000。全部的未来的版本必须向后兼容。如果新版本的规范出现倒退兼容性,必须定义新 GUID。

Trace规范

介绍

在复杂系统中,理解程序行为并不容易。在这样的系统中,软件有时不能按预期运行。这可能是由许多因素导致。例如,与其他核心、软件、外围设备的交互、实时事件、较差的实现或以上这些组合。

因为调试器的侵入性特点,并非总是可以使用调试器来观察正在运行的系统。提供程序运行数据的可视化非常重要,这需要在不产生大量数据情况下实现。

一个实现方法是通过采用处理器分支跟踪技术。

通过从指定执行地址进行跟踪,并让其将程序运行的 delta 以消息的形式发出来实现,这些 delta 主要由跳转、调用、返回以及分支指令导致,当然中断和异常也能导致 delta 改变。

因此,系统需要具有一些必备的组件:

- 一种带有指令跟踪接口的内核,该接口输出所有相关信息,以允许成功创建处理器分支跟踪等。这是一个高带宽接口:在大多数实现中,它将为每个核心执行时钟周期提供大量数据(指令地址、指令类型、上下文信息等)

- 连接到指令跟踪接口并将信息压缩为较低带宽跟踪包的硬件编码器

- 连接到此指令跟踪接口并压缩将信息转换成较低带宽跟踪分组;

- 用于传输的传输通道或用于存储这些跟踪数据包的存储器;

- 一种解码器,通常是外部 PC上的软件,它接收跟踪数据包,并在知道原始哈特上运行的程序二进制文件的情况下,重建程序流。该解码步骤可以在 hart 执行时离线或实时完成

在 RISC-V 中,所有指令都是无条件执行的,或者至少可以根据程序二进制来确定它们的执行。可以假设增量之间的指令都是顺序执行的。因此,无需对整个指令流进行跟踪,只需要显示分支是否被执行以及间接执行的分支地址即可。当程序计数器的更改量无法从执行二进制文件时,需要为跟踪解码器提供目标地址(即地址下一个有效指令的)。例如,间接分支或跳转指令地址由寄存器的内容而不是嵌入的常量决定程序二进制文件。

中断通常与程序的执行异步发生,而不是故意作为特定指令或事件的结果。可以用相同的方式来考虑异常,即使它们通常可以链接回特定的指令地址。解码器通常不知道中断在指令序列中的何处发生,因此跟踪编码器必须报告正常程序流停止的地址,并给出异步目的地的指示,这可能与报告异常类型一样简单。当发生中断或异常,或处理器停止时,必须在跟踪中包含预先失效的最终指令。

本文档用于指定入口端口(RISC-V 核心和编码器之间的信号)、压缩分支跟踪算法以及用于封装压缩分支跟踪信息的数据包格式。

术语缩略语

ATB: Arm trace bus

- branch: an instruction which conditionally changes the execution flow

- CSR: control/status register

- decoder: a piece of software that takes the trace packets emitted by the encoder and reconstructs the execution flow of the code executed by the RISC-V hart

- delta: a change in the program counter that is other than the difference between two instructions placed consecutively in memory

- discontinuity: another name for ’delta’ (see above)

- ELF: executable and linkable format

- encoder: a piece of hardware that takes in instruction execution information from a RISC-V hart and transforms it into trace packets

- EPC: exception program counter

- exception: an unusual condition occurring at run time associated with an instruction in a RISC-V hart

- hart: a RISC-V hardware thread

- interrupt: an external asynchronous event that may cause a RISC-V hart to experience an unexpected transfer of control

- ISA: instruction set architecture

- jump: an instruction which unconditionally changes the execution flow

- direct jump: an instruction which unconditionally changes the execution flow by changing the PC by a constant value

- indirect jump: an instruction which unconditionally changes the execution flow by changing the PC to a computed value

- inferable jump: a jump where the target address is supplied via a constant embedded within the jump opcode • uninferable jump: a jump which is not inferable (see above)

- LSB: least significant bit

- MSB: most significant bit

- packet: the atomic unit of encoded trace information emitted by the encoder

- PC: program counter

- program counter: a register containing the address of the instruction being executed

- retire: the final stage of executing an instruction, when the machine state is updated (some times referred to as ’commit’ or ’graduate’)

- trap: the transfer of control to a trap handler caused by either an exception or an interrupt

- updiscon: contraction of ’uninferable PC discontinuity’

规范主要介绍了编码器控制、分支跟踪、Hart 编码器接口、过滤器、时间戳、指令编码器输出包、数据跟踪编码器输出包、参考压缩分支跟踪算法、参数和发现、编码器、代码和包示例、代码片段和传输、未来方向等。

外部调试规范

介绍

当设计从模拟发展到硬件实现时,用户对系统当前状态的控制和理解会急剧下降。帮助启动和调试低级别软件和硬件,在硬件中内置良好的调试支持至关重要。当一个健壮的操作系统在内核上运行,软件可以处理许多调试任务。然而,在许多情况下硬件支持至关重要。

本文档概述了 RISC-V 平台上外部调试支持的标准架构。该体系结构允许多种实现和权衡,这是对

广泛的 RISC-V 实现。同时,本规范定义了接口,允许调试工具和组件基于 RISC-V ISA。

系统设计者可以选择添加额外的硬件调试支持,但本规范定义通用功能的标准接口

系统概述

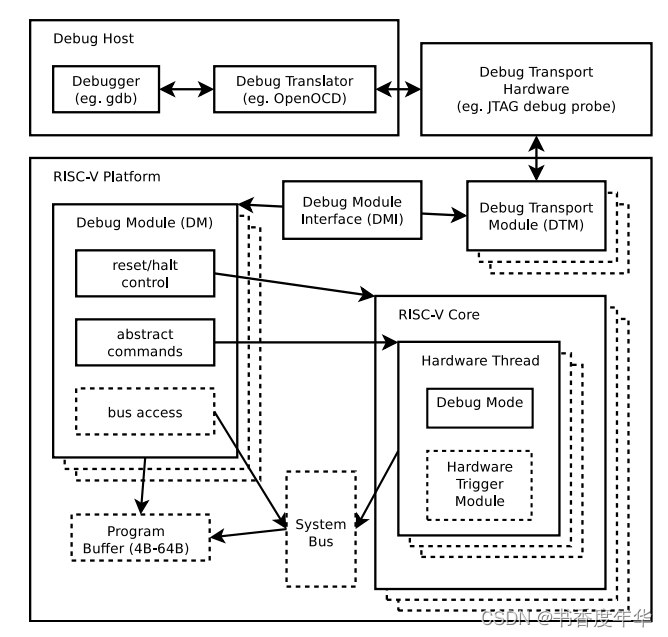

图 3 显示了外部调试的主要组件,虚线所示的块是可选的。

用户与正在运行调试器(例如 gdb)的调试主机(例如笔记本电脑)交互。调试器与调试转换器(例如 OpenOCD,其可以包括硬件驱动程序)通信,以与调试传输硬件(例如 Olimex USB-JTAG 适配器)通信。调试传输硬件将调试主机连接到平台的调试传输模块(DTM)。DTM 使用调试模块接口(DMI)提供对一个或多个调试模块(DM)的访问。

平台中的每一个 Hart 都由一个 DM 控制,Hart 可能是异构的,hart-DM 映射没有进一步的限制,但通常单个内核中的所有hart都由同一个 DM 控制。在大多数平台中,只有一个 DM 可以控制平台中的所有 Hart 。

DM 在平台中提供对 Hart 的运行控制,抽象命令提供对 GPR 的访问,可以通过抽象命令或将程序写入可选的程序缓冲区来访问其他寄存器。

程序缓冲区允许调试器在 Hart 上执行任意指令,该机制也可用于访问内存,可选的系统总线访问块允许在不使用 RISC-V Hart 执行访问的情况下进行存储器访问。

每个 RISC-V Hart 可以实现一个触发模块。当满足触发条件时,harts 将停止并通知调试模块。

此外,规范描述了调试模块、RISC-V 调试、调试传输模块、硬件实现、调试器实现等。

皮格马利翁效应心理学指出,赞美、赞同能够产生奇迹,越具体,效果越好~

“收藏夹吃灰”是学“器”练“术”非常聪明的方法,帮助我们避免日常低效的勤奋~

下一篇 「RISC-V Arch」SBI 规范解读(上)