CXL,全称Compute Express Link,该技术由Intel牵头开发用于高性能计算、数据中心,主要解决处理器、加速器和内存之间的cache一致性问题,可消除CPU、专用加速器的计算密集型工作负载的传输瓶颈,显著提升系统性能。

一、概述

参考文档

参考链接:CXL 2.0白皮书

CXL应用场景

如图为PCIe的应用场景:

如图为CXL的应用场景:

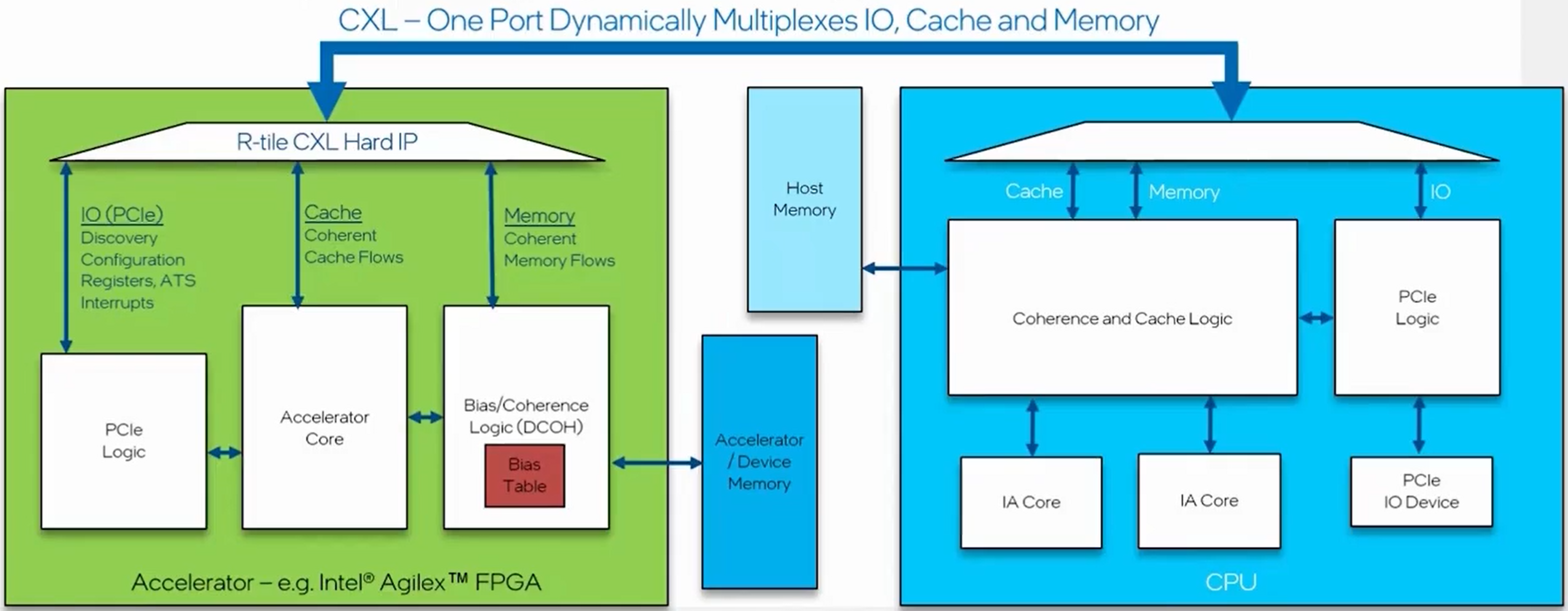

二、CXL协议架构

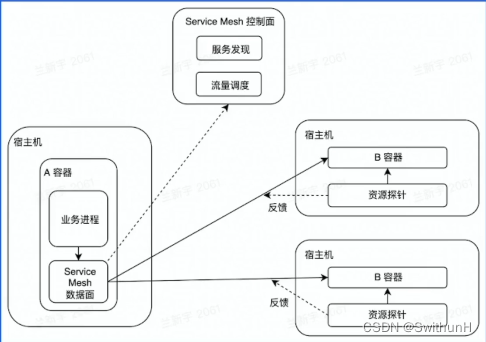

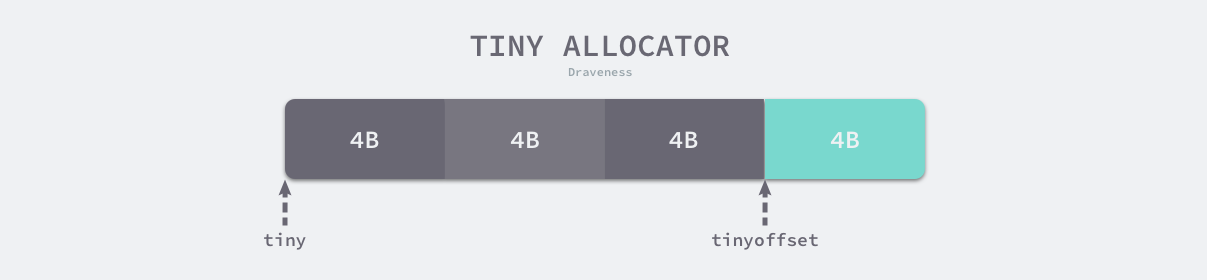

该协议基于PICe技术,完全兼容PCIe5.0,新协议的物理层直接采用于PCIe5.0,在事务层和数据链路层有所增加。增加了FlexBus用作CXL的互联。如下图所示,CXL.io使用PCIe的事务层和链路层,CXL.cache和CXL.mem使用自己的事务层和链路层,CXL_ARB/MUX模块将两组数据流交织,实现三组子协议的复用。

-

CXL定义了三个子协议,三个子协议在工作时可以动态切换:

cxl.io: PCIe5.0的增强版本,用于初始化、寄存器访问、中断处理、MMIO事务等,用于CPU访问外设的配置空间

cxl.cache:通过主机与设备的交互,引起cxl设备使用请求和响应的方式缓存主机侧的内存,用于外设访问CPU的内存

cxl.mem:主机处理器使用加载和存储命令的方式访问CXL连接设备的内存,同时CXL协议可以用作内存扩展,用于CPU访问外设的内存 -

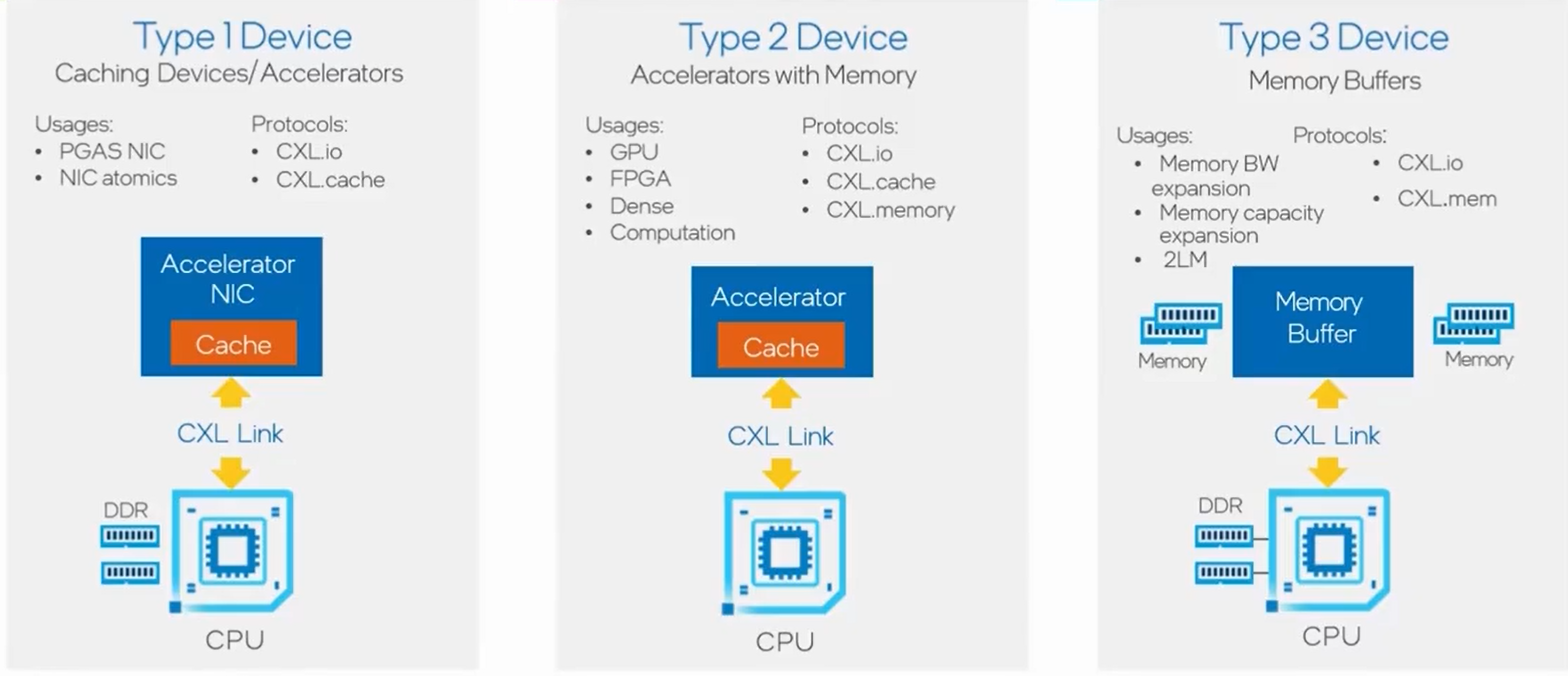

CXL 1.0/1.1设备

Type1设备:数据分析应用

Type2设备:重型加速器,即高带宽的内存应用场景,用于数据库加速分析功能

Type3设备:内存缓冲区,扩展主机的内存空间(内存资源池化?)

三、CXL运行机制

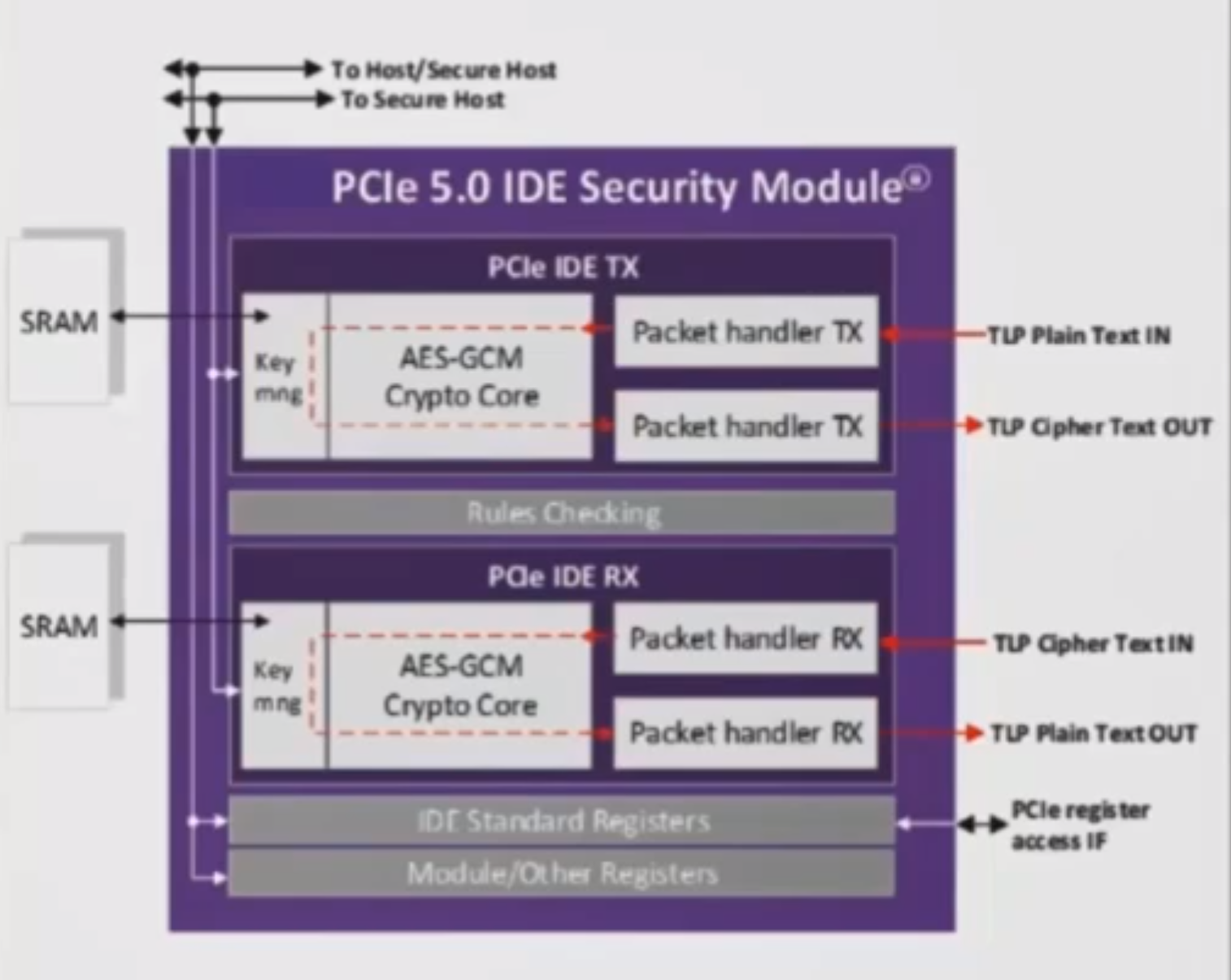

数据安全

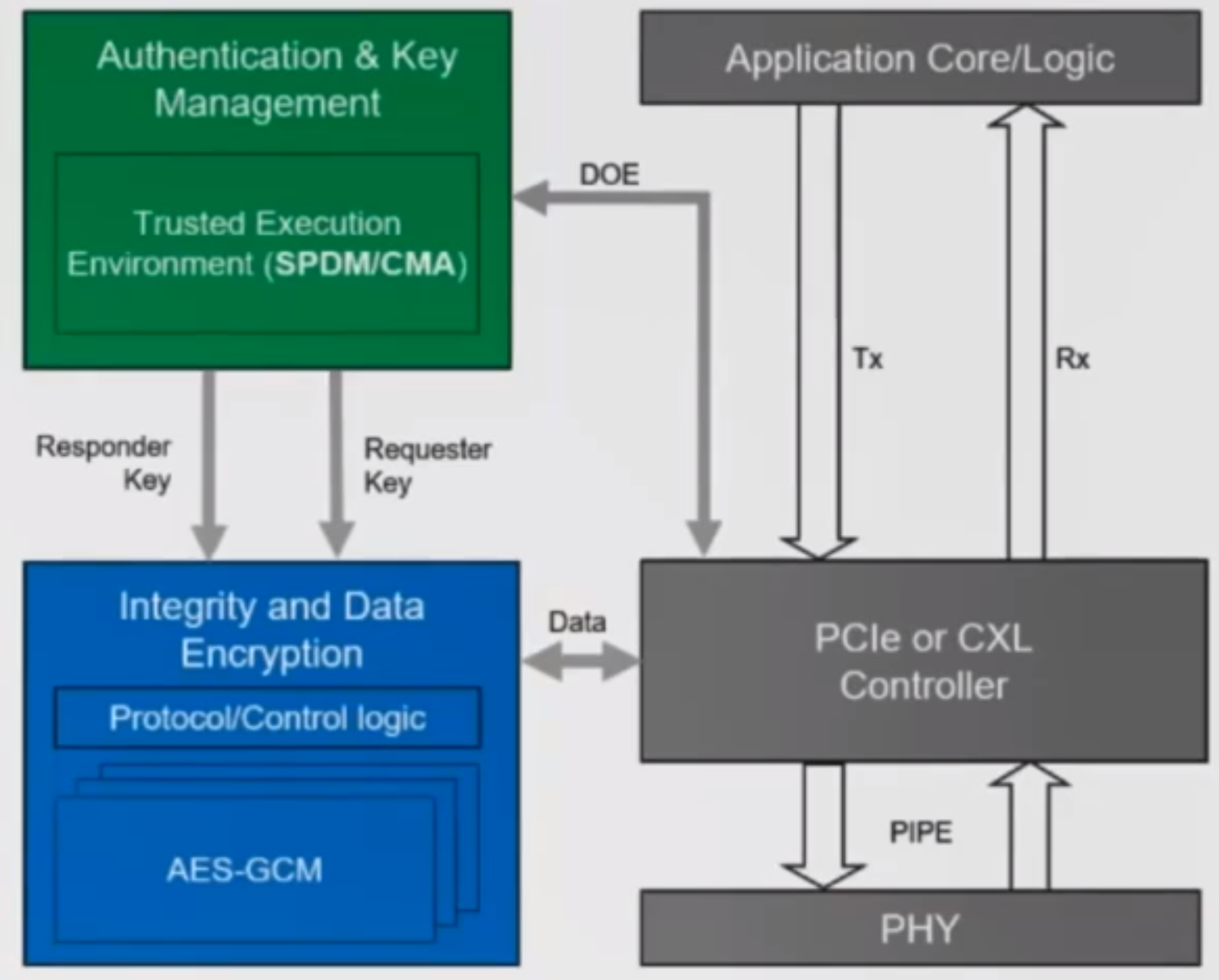

synopsys CXL数据安全解决方案