毕设是实现CXL的type3扩展内存设备,因为CXL技术非常新,2019年推出,本专栏也是记录CXL的相关知识与一些浅薄的理解

文章目录

- CXL出现的背景

- CXL是什么

- 其他互联总线介绍

- CXL胜出的原因

- CXL内容简介

- 包含三种协议 CXL.io/cache/memory

- 支持三种设备类型

- CXL1.1、2.0、3.0版本演进

- 其他可参考资料

CXL出现的背景

背景总结起来有两个方面,底层原因还是因为计算与内存的发展速度不同步:

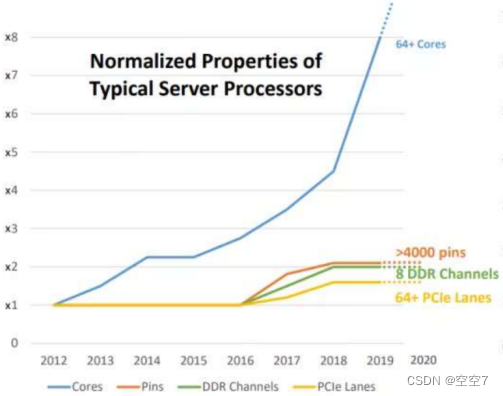

- 大数据时代,数据规模爆炸性增长,以计算为核心的传统计算机体系架构(冯诺依曼架构)出现了“内存墙”、“IO墙”问题,成为了应用性能的瓶颈。

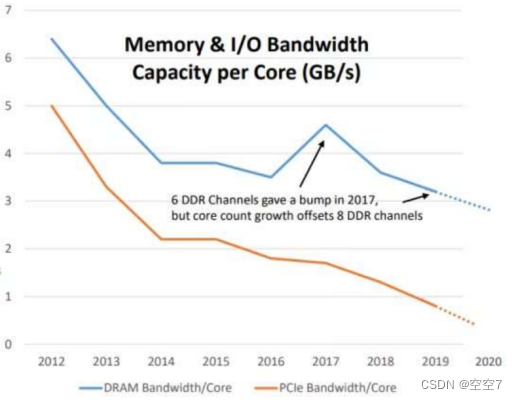

过去十年,存储和I/O带宽的增长远远落后于算力的增长。

一方面,随着CPU内核数的快速上升,每颗CPU内核对应的内存带宽反而不断下降,在应用访问的数据爆炸增长时,多级存储带来的响应延迟与不断下降的传输带宽都将成为拖累整体性能的瓶颈,即“内存墙”。

另一方面,CPU可以快速访问内存中的数据,但是当下动辄GB级的数据中心应用程序往往无法全部运行在内存中,需要放在外部存储里,使用网络I/O来访问数据,而I/O方式的访问会使得访问速度下降几个数量级,不可避免的成为应用性能的瓶颈,即“I/O墙”。

CXL支持的第三种内存扩展设备类型,使用CXL.io与CXL.mem子协议,通过CXL/PCIe插槽扩展内存容量和带宽,有效的打破了“内存墙”和“I/O墙”的瓶颈。

- 随着各类设备加速器性能的提高,同时业界对计算机处理大规模数据的要求提高,以往以CPU-Memory为中心的体系架构逐渐变成了以CPU、GPU、FPGA、SmartNIC等设备齐头并进的趋势,异构计算火热发展。而20年前提出的PCIe技术对于设备间的高速互联并不是很有效,业界非常期待一种面向异构计算的高带宽、低延迟的一致性互联总线的出现,CXL应运而生。

CXL是什么

CXL (Compute Express Link)1 总线互连标准是2019年由英特尔公司推出,以提高数据中心性能为目标,旨在改善传统PCIe系统中的通信路径,是针对数据中心、高性能计算,人工智能等范畴的创造性互连总线。它可以实现CPU与GPU、FPGA或其他加速器之间更高效率、更快速度的连接,从而满足高性能异构计算的要求,并且在提供更高带宽和更好内存一致性等方面做出了显著贡献2。CXL因其底层基于PCIe 5.0规范,具有物理层上的系统一致性,相比于其他互连协议有着更好的兼容性和易用性,目前CXL已经成为事实上的唯一开放标准。

其他互联总线介绍

近年来,随着高性能异构计算对带宽和延迟的要求越来越高,各大服务器厂商纷纷在高速互连总线技术领域发力,提出了各种各样的互联协议标准,既有开放标准,也有专用标准。

OpenCAPI3是IBM公司于2016年提出,是一种开放式接口架构,允许任何微处理器连接到一致的加速器和 I/O 设备。已经于2022年将所有规范和资产转让给CXL联盟。

CCIX4于2016年提出,是ARM公司主要支持的标准,是一种能够将两个或两个以上器件通过缓存一致性的方式来共享数据的片间互联。

Gen-Z5于2016年提出,是AMD公司主要支持的标准,是一种可扩展的通用系统互连标准,旨在简化数据访问、设计和方案架构。但是缺乏缓存一致性支持,已经于2020年将所有规范和资产转让给CXL联盟。

NVLink6于2014年由NVIDIA公司提出,是一种高速GPU互连技术,与传统的PCIe系统解决方案相比,能为多GPU系统提供更快速的替代方案。NVLink 技术通过连接两块 NVIDIA显卡,能够实现显存和性能扩展,从而满足最大视觉计算工作负载的需求,是一种专用标准。

CXL胜出的原因

CXL总线互连标准2019年由英特尔公司推出,到目前为止已经更新迭代了1.0/1.1、2.0、3.0三个版本,作为一项崭新的技术,它的发展非常迅速且具备清晰的技术发展路线。

相较其他互连协议,首先,CXL提供CPU和GPU、加速卡等外设间更高的数据带宽和更好的内存一致性访问。

其次,CXL包含CXL.io/cache/memory三种子协议,支持设备类型更多样,场景更丰富,是目前发展势头最好的一个互连标准。

最后,CXL是基于PCIe5.0协议设计,在原有的PCIe链路基础架构之上,可以同时支持PCIe设备与CXL设备运行,具有更高的兼容性。(其实也是因为这种互联总线一般需要CPU方面的支持,Intel作为CPU巨头,它不支持,其他协议也很难发展下去;同时也需要兼容过去的PCIe总线;那么CPU厂商支持,兼容PCIe,协议设计合理有效,CXL就这样走向胜利)

CXL内容简介

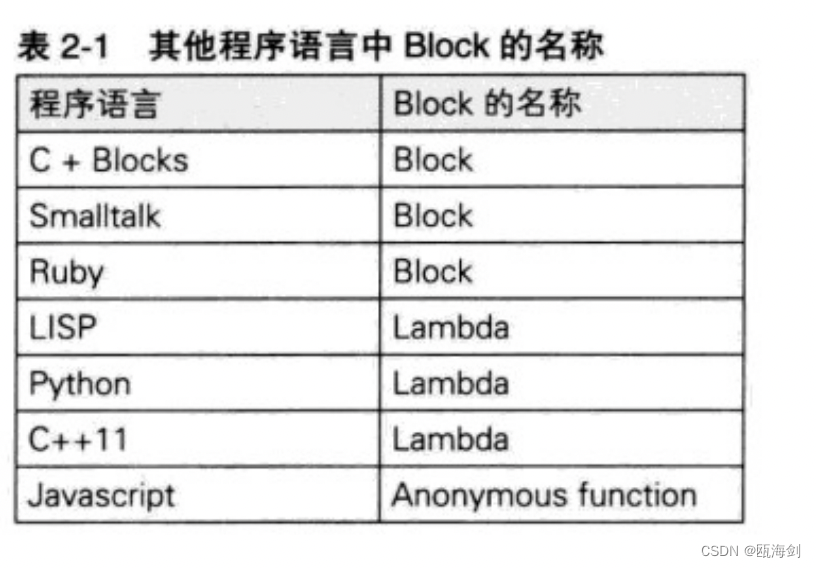

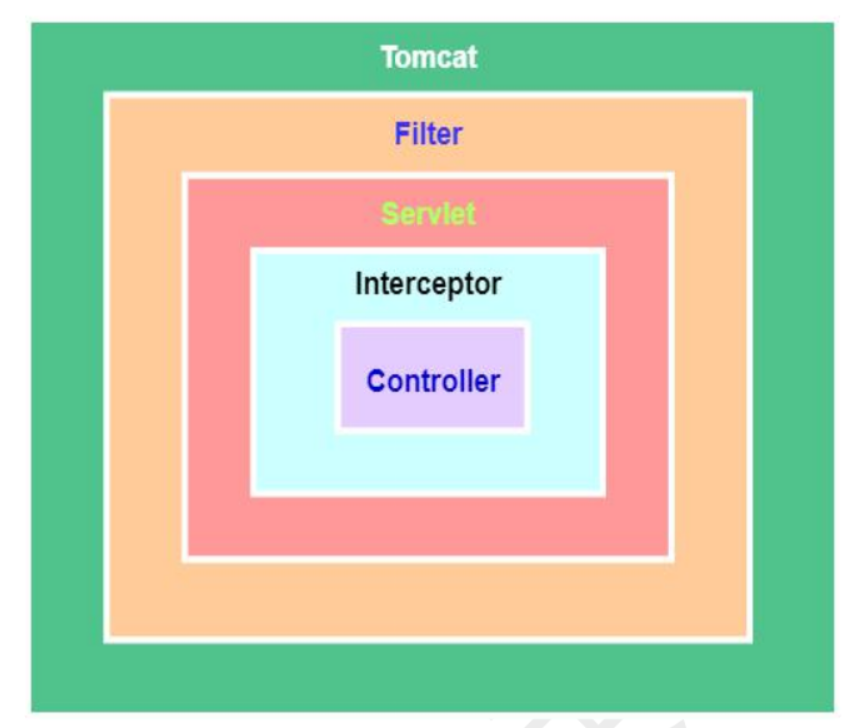

包含三种协议 CXL.io/cache/memory

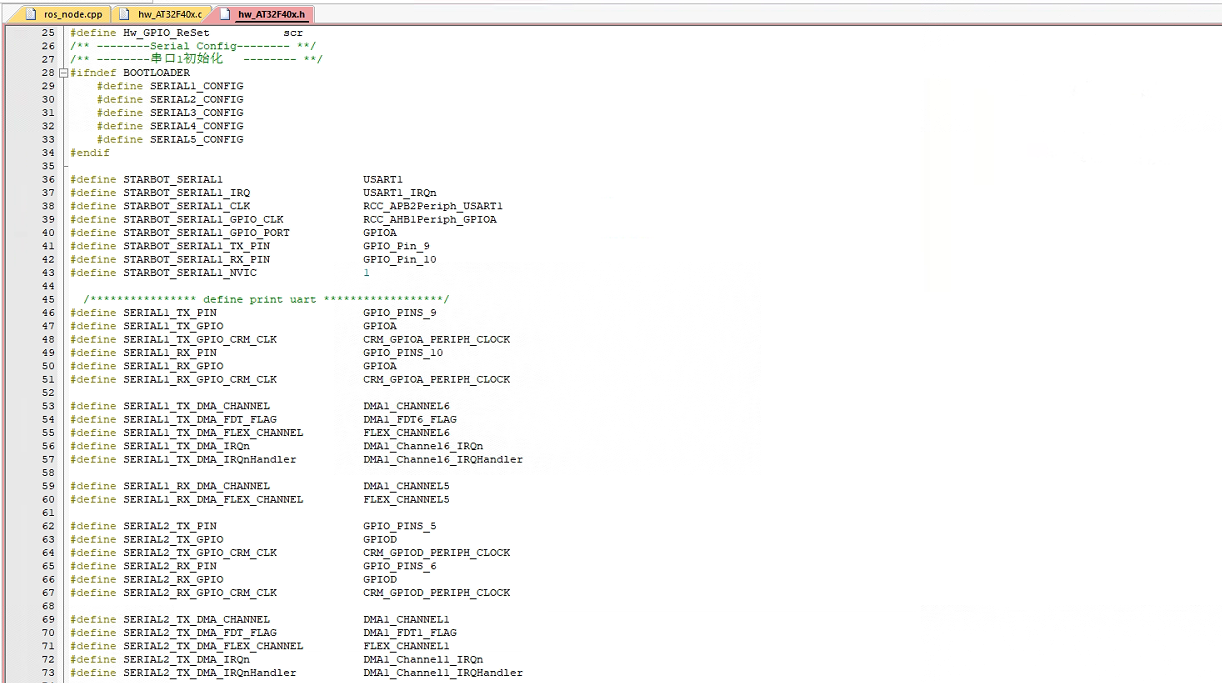

CXL.io:与PCIe协议相同

该协议本质上是PCIe 5.0协议的扩展,用于设备的发现、配置、寄存器访问和中断等,为IO设备提供了非一致数据的Load/Store接口(PCIe协议不支持一致性机制)

CXL.cache:支持设备对主机内存的访问

该协议定义了设备对主机内存(DIMM)的访问,允许设备使用请求/响应机制以极低的延时访问主机内存中的数据,类似于DMA(Direct Memory Access)

CXL.mem:支持主机对设备内存的访问

该协议允许主机处理器使用Load/Store指令访问设备内存,主机CPU充当主设备,而被访问设备充当从设备。CXL.memory协议同时支持易失性和非易失性存储

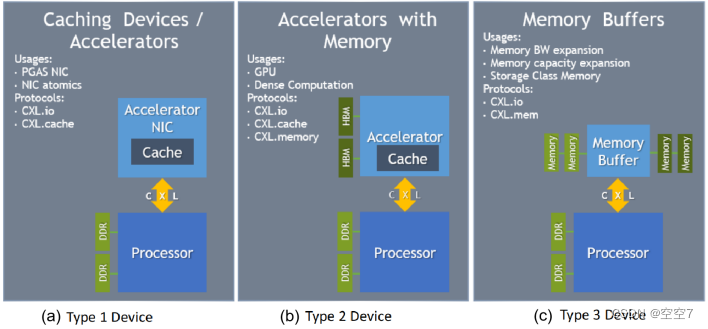

支持三种设备类型

CXL总线标准支持CXL.io/cache/memory三个子协议,三个子协议进行组合使用,得到CXL支持的三种设备类型。

Type1 Device:使用CXL.io与CXL.cache两个子协议,典型代表是NIC。

现在的NIC只能够通过 DMA(Direct Memory Access)的方式访问内存,且无法缓存数据。具备CXL.cache后,该网卡可以通过CXL.cache 访问主机内存,并缓存一些数据到NIC上,提高了运行效率。

Type2 Device:使用CXL.io/cache/memory三个子协议,典型代表是GPU、FPGA等加速器。

使用CXL.cache,GPU可以直接访问主机上的内存,使用CXL.memory,主机CPU可以直接访问GPU显存中的内存,而不需要显式的大块内存拷贝。

Type3 Device:使用CXL.io与CXL.memory两个子协议,典型代表是扩展内存设备。

通过 CXL.memory,Host可以直接使用load/store指令直接访问CXL内存扩展设备的内存,也可以进行缓存,从而实现内存容量的扩展,考虑到PCIe带宽的不断增加,这种方式还可以扩展内存带宽。

CXL1.1、2.0、3.0版本演进

CXL正在迎来大内存的曙光

大内存时代振奋人心的CXL技术(上)

大内存时代振奋人心的CXL技术(下)

其他可参考资料

CXL.cache 协议详解

CXL大内存论坛-2022中国数据与存储峰会

CXL学习笔记

SDC2020: CXL 1.1 Protocol Extensions: Review of the cache and memory protocols in CXL