电荷泵(CP)设计

- 前言

- 一、电荷泵(CP)原理

- (1)电流失配问题

- (2)开关管的时钟馈通问题

- (3)电荷注入问题

- 二、电荷泵(CP)电路

- 三、电荷泵性能测试

- 测试原理图

- 充电测试

- 放电测试

- 参考文献

- 各部分链接链接:

前言

本文主要内容是对电荷泵(CP)做出简单介绍,为课程设计部分章节内容,后需给出各部分的设计方案,以及测试结果。

一、电荷泵(CP)原理

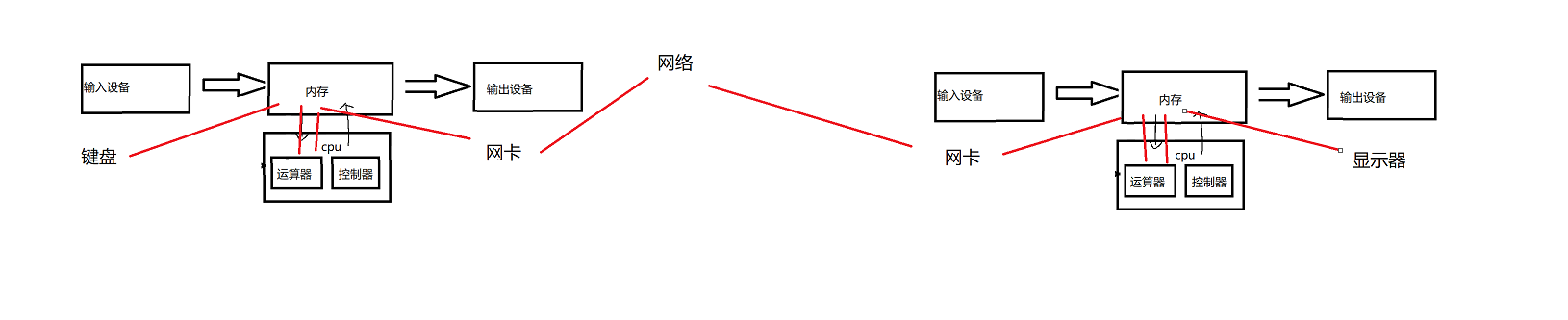

在PLL电路中,如果直接将无源环路滤波器与PFD相连,则会出现PFD的增益不是一个常数,会随着环路滤波器的平均输出变化而变化的问题。如果环路增益变小,将会降低阻尼系数,进而产生很大地过冲。为了解决上述问题可以让PFD驱动一个电荷泵产生一个输出电流而不是输出电压。电荷泵将PFD检测到的相位差信号转换为电流信号,进而控制对环路滤波器进行充放电。当CPPLL环路处于同步带的时环路频率固定,此时PFD无相位和频率的差别,CP输出电压VOUT处于恒定;当CPPLL环路处于捕捉带的时候,参考频率与分频后的频率产生了相位或频率差别,环路失锁,PFD依据鉴频鉴相结果控制CP的充放电依次改变VOUT,进而改变VCO的振荡频率。·

其工作过程如下:

(1)当 PFD 输出电压信号 up 为高, down 为低时,开关 S1 闭合, S2 断开,电荷泵上面通路导通,下面通路关断,电荷泵将以电流

I

1

I_1

I1对滤波器充电。

(2)当 PFD 输出信号 up 为低且信号 down 为高时,开关 S1 断开,S2 闭合,电荷泵下面通路导通,电荷泵将以电流

I

2

I_2

I2对滤波器放电。

(3)当 up 和 down 信号都为低时,两个开关均断开,因此电荷泵输出处于高阻态,没有对环路滤波器进行充放电,环路滤波器电压保持不变。

(4)当 up 和 down 信号都为高时,两个开关均导通,将形成从电源到地的通路。若电流源

I

1

I_1

I1与

I

2

I_2

I2相同的话,流过 S1 电流将从 S2 流出,流入环路滤波器的电流也将为 0,因此没有对环路滤波器进行充放电,环路滤波器电压保持不变。

PFD 的输出信号 up 和 down 信号保持高电平的时间差主要取决于两输入信号的相位差,因此,相位差就决定了电荷泵对环路滤波器的充放电时间。其工作过程波形图如下图4-3-2所示。

实际的电荷泵在工作时,受限于如下非理想效应:

(1)电流失配问题

由于 PFD 的非理想特性,在系统输入相位差为零的情况下,PFD 的两个输出端 UP 和 DN 也会产生一窄脉冲。即便是在 PLL 锁定的情况下,UP 和 DN 端也会在有限时间内同时打开电荷泵,进而使上下电流源同时打开。由于上下电流源的不匹配,会出现一个电流差,使得电荷泵产生的净电流不为零,会造成 PLL 环路失锁。

(2)开关管的时钟馈通问题

时钟馈通指的是当 MOS 开关栅极的时钟控制信号发生一个跳变时,由于 MOS 寄生电容的存在,该电压的跳变会耦合至 MOS 源漏处,从而引起源漏电压的变化,这种非理想效应在漏极开关型电荷泵中最为明显。如图4-3-3所示,由于开关管栅漏极覆盖电容的效应,当上拉脉冲和下拉脉冲通过 C G D 1 C_{GD1} CGD1 和 C G D 2 C_{GD2} CGD2 的耦合作用到达电路输出端 V c o n t V_{cont} Vcont时,由于 R 1 C 1 R_1C_1 R1C1很大,在刚开始时,只有 C 2 C_2 C2会减弱这种时钟馈通效应:

当电荷泵关断后,

C

1

C_1

C1和

C

2

C_2

C2共享电荷将减小至:

时钟馈通效应示意图

(3)电荷注入问题

沟道电荷注入是指当开关断开时,存于沟道中的电荷注入 MOS 的源漏,引起源漏电压变化的现象。在下图4-3-4所示简单 CP 电路中,当开关管 M1 和 M2 导通时,其反型层中存在一定数量的沟道电荷,可以表示为:

随着开关的导通,电荷被吸收,而开关关断时,电荷被消除。当开关管进行开关控制时,MOS 开关会通过源极和漏极将沟道电荷对输出端进行注入或吸收。如图4-3-4所示,通常由于 M1 和 M2 的尺寸和过驱动电压不同,不能正好抵消对方的电荷注入或吸收,因此在导通和关断时,控制电压会收到干扰, 而这个效应就被称为电荷注入效应。当开关进行关断时,电荷吸收作用类似。

针对这两种非理想效应,可以通过添加 Dummy 开关或采用互补开关进行改善。同时,为了降低开关的寄生电容可以采用最小尺寸的晶体管,但是减小尺寸会导致开关电阻增加,从而降低开关的速度,因此在设计电路时需要进行折衷考虑。

二、电荷泵(CP)电路

基于以上原理,此次所设计的 CP 电路原理图如图4-3-5所示。电路中 M0 和 M3 为开关管,分别由控制信号 Down 和 UP 控制其导通和关断。M4 和 M5 为开关管匹配的“虚拟”开关,其作用是为了减小开关管沟道电荷注入效应对输出的影响。以 M0 和 M5 为例,当Down 为高电平时,M0 导通,M5 关闭,在 M5 关闭的同时会将自身沟道电荷注入给 M0 ,帮助其沟道建立;当 Down 为低电平时,M0 关断,M5 导通,此时 M5 吸收 M0 的沟道电荷,帮助其沟道关断。M1 和 M2 也为开关管,其尺寸为 3:1,确保了在信号互补开关时,能够相互吸收对方的注入沟道电荷,减小沟道电荷出入效应,尺寸满足

W

5

:

W

0

=

2

,

W

4

:

W

3

=

2

,

W

1

:

W

2

=

3

:

1

W_{5} :W_0=2,W_4:W_3=2,W_1:W_2=3:1

W5:W0=2,W4:W3=2,W1:W2=3:1。另外,此结构由于中间控制管的作用,可以有效的抑制时钟馈通效应。为了驱动这些电路,采用较大驱动能力的反相器产生互补信号,该电路结构可以提供最大的电压裕量。

三、电荷泵性能测试

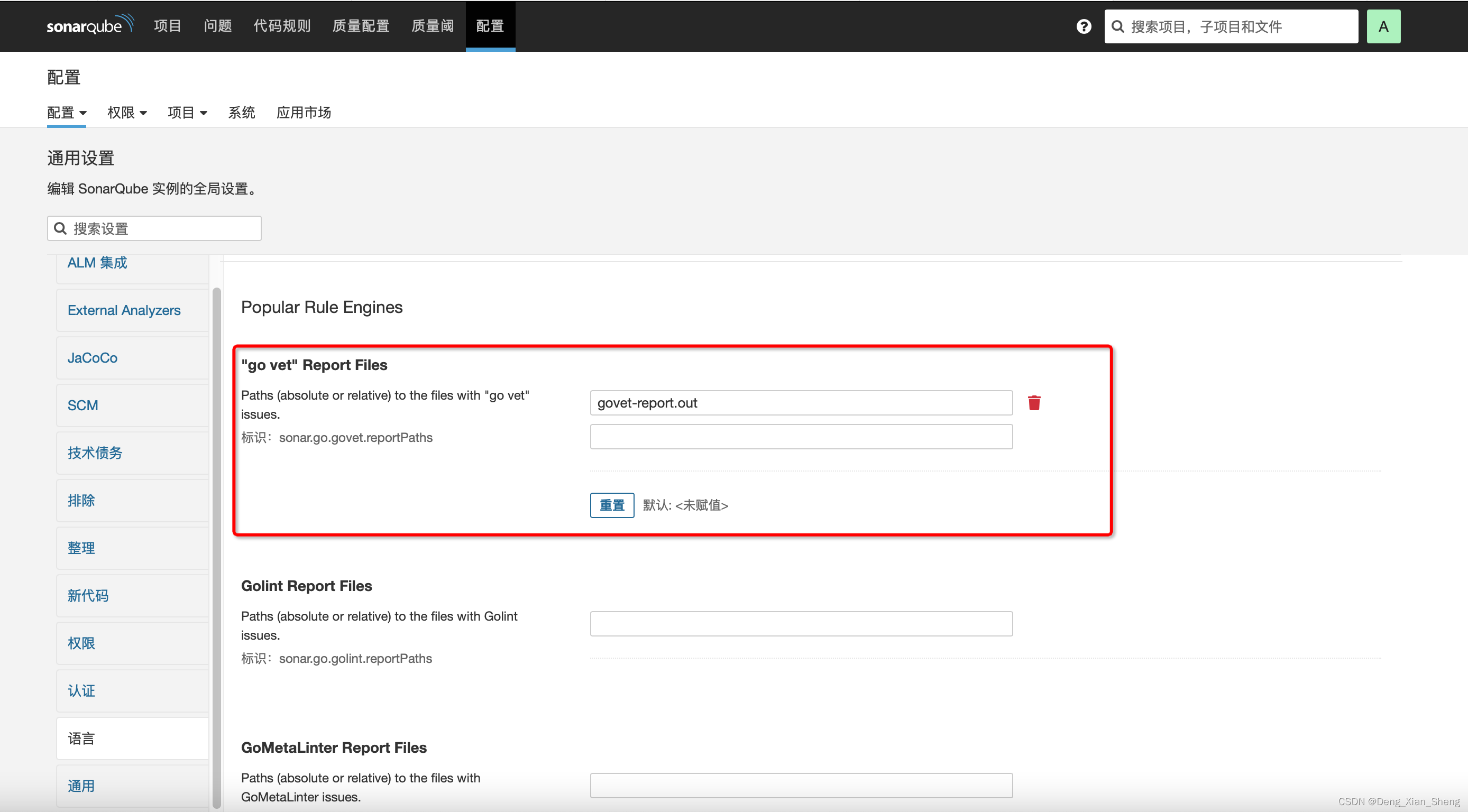

图4-3-6是本次电荷泵的测试电路图。

测试原理图

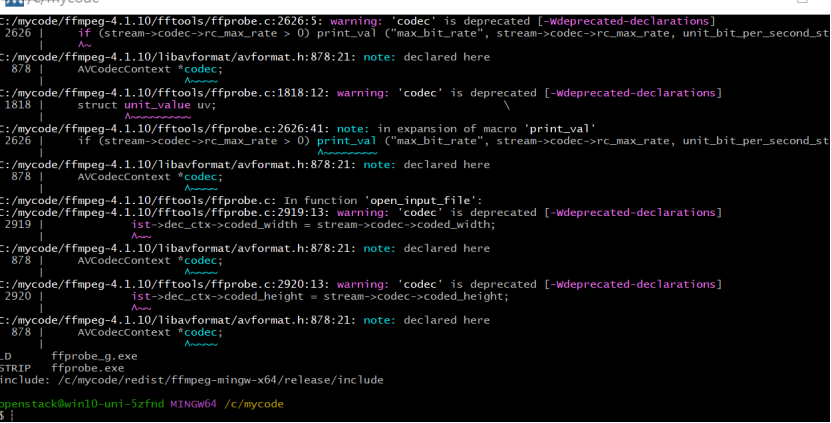

电荷泵充电过程的仿真波形如图4-3-7所示,给 UP 一个幅度为 1.8V 的脉冲信号,采用瞬态仿真的方式,查看 UP 信号和输出节点的电压信号。由图可知,当 UP 信号处于高电平有效时输出电压线性上升,充电结束后输出电压保持不变,电荷泵充电至完全稳定所需要的时间大致为 46ns。

充电测试

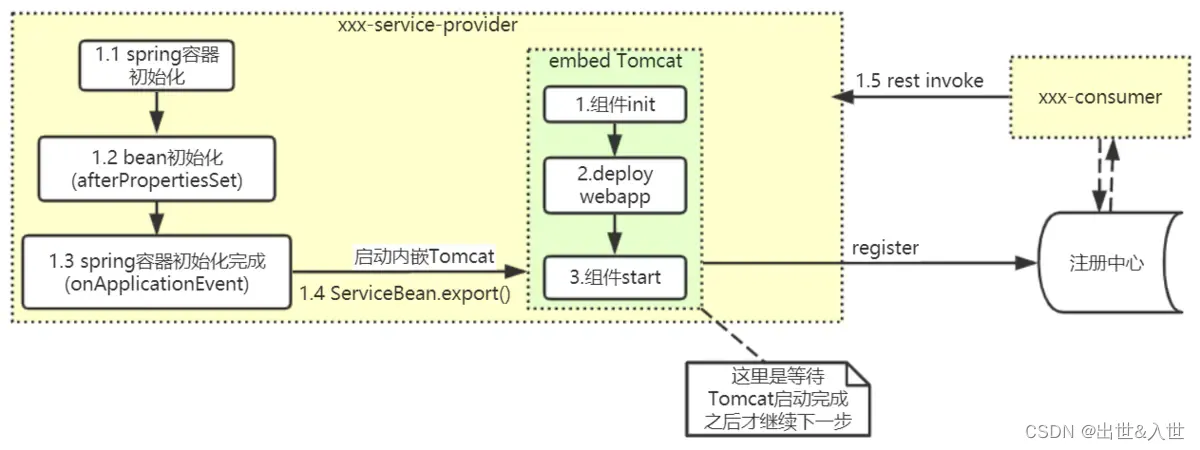

同理,CP 放电过程的仿真波形如图4-3-8所示,可知电荷泵放电至完全稳定所需要的时间大致 70ns。

放电测试

参考文献

[1]王程程. CMOS电荷泵锁相环的研究与设计[D].重庆邮电大学,2019.

[2]来萧桐. 电荷泵锁相环(CPPLL)中的关键模块设计[D].东南大学,2021.

[3]肖乃稼. 高速CMOS电荷泵锁相环设计[D].合肥工业大学,2017.

[4]钟见. 应用于高速电路中的电荷泵锁相环设计[D].东南大学,2016.

[5]王靖瑞. 基于0.18μm CMOS工艺电荷泵锁相环的研究与设计[D].西安电子科技大学,2021.

| 分割线 |

各部分链接链接:

频率综合器(Frequency Synthesizer,FS)设计 链接:【模拟集成电路】频率综合器(Frequency Synthesizer,FS)设计

鉴频鉴相器(PFD)设计 链接:【模拟集成电路】鉴频鉴相器设计(Phase Frequency Detector,PFD)

压控振荡器(VCO)设计 链接:【模拟集成电路】宽摆幅压控振荡器(VCO)设计

环路滤波器(LPF)设计 链接:【模拟集成电路】环路滤波器(LPF)设计

分频器(DIV_TSPC)设计 链接:【模拟集成电路】分频器(DIV_TSPC)设计

![交换字符使得字符串相同[贪心]](https://img-blog.csdnimg.cn/2697794abadd4002bd7f0c3f9f4c2149.png)