1.x和z值

1.1.定义

x:表示不定值

z:表示高阻态,还有一种表达方式“?”

一个x/z可以用来定义十六进制(h)数的4位二进制的状态,八进制(o)数的3位,二进制(b)数的1位,或者十进制(d)数的整体值。

举例如下:

4'b10x0 //位宽为4的二进制数,其bit1为不定值

8'h4z //位宽为8的十六进制数,其低4bit为高阻态(第1种表达方式)

12'd? //位宽为12的十进制数,其值为高阻态(第2种表达方式)

1.2.使用注意

在rtl仿真中,x和z是两个情况,而在综合时被视为一种情况,因此在需要综合的代码中,是不允许出现x和z的。

2.case的使用

2.1.定义

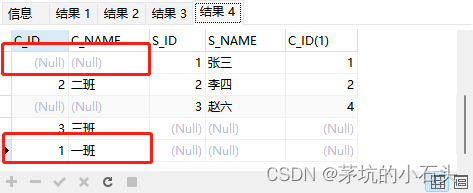

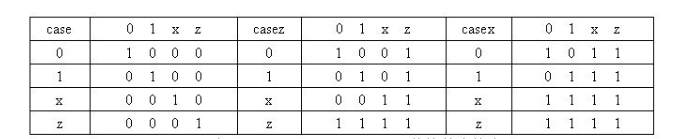

case :按位全等比较

casez:忽略高阻态的bit位,只关注其他位的比较结果

casex:进一步放松比较范围,忽略高阻态或不定态的bit位

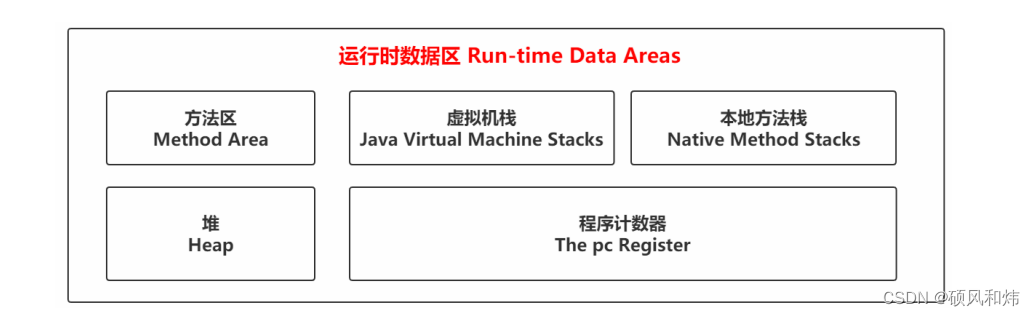

真值表如下:

2.2.使用规则

2.2.1.case 分支中不允许出现x、z/?

case语句中出现“x”,“z”,“?”,容易导致综合前后不一致。

2.2.2.可以使用casez或casex,但是不允许使用z和x

casez和casex仿真不一样,但都可综合且综合后电路一样,尽量使用casez。

使用casez(x)语句可以和”?”配合过滤可忽略bit位,但是语句中不能有“x”和“z”。

举例正确代码如下:“?”表示可忽略的无关比较位,这里不代表高阻态。

wire [2:0] sel;

always@(posedge clk)

casez(sel)

3’b001 : data_out <= data_in0 ;

3’b01? : data_out <= data_in1 ;

3’b1?? : data_out <= data_in2 ;

default: data_out <= 4’b0 ;

endcase2.2.3.default项一定(最好)补齐

default项的补齐避免在组合逻辑中出现latch。