各位同学大家好,欢迎继续做客电子工程学习圈,今天我们继续来讲这本书,硬件系统工程师宝典。

上篇我们说到在电源完整性分析时,如何合理使用去耦电容,知道了对于不同频率的信号噪声采用不同类型的去耦电容。今天我们来看看电源完整性分析的目的和方法。

PI分析的目标

电源完整性设计的目的:

1.控制电源噪声,提供干净稳定的电压;

2.实时响应负载对电流的快速变化;

3.为其他信号提供低噪声回流路径

电源产生波动的原因是实际电源平面存在阻抗,在瞬间电流流过时会产生一定的电压浮动。因此,就要保证足够低的电源平面的阻抗,实现电源的完整性设计。电源系统的目标阻抗定义为:

电源目标阻抗=最大允许文波电压/瞬时动态电流,即ZPDN=V*Ripple/△Imax其中,V是电源电压,Ripple是允许的电压波动范围,一般为5%或3%,△Imax为负载芯片的最大瞬态电流变化量,可以采用负载最大工作电流的一半。

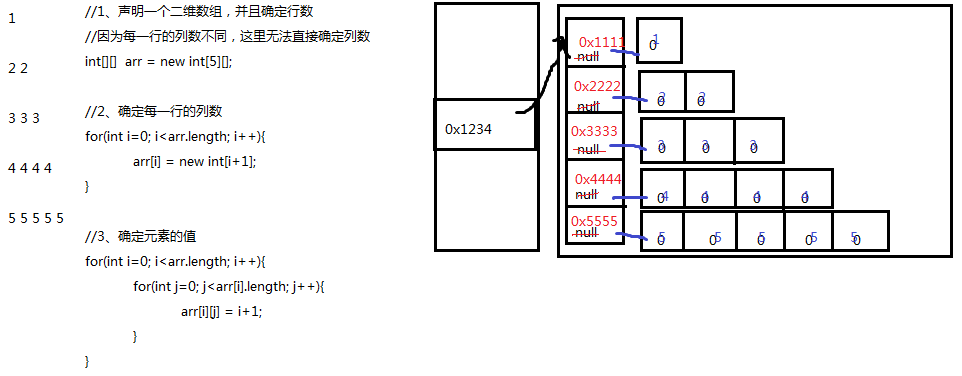

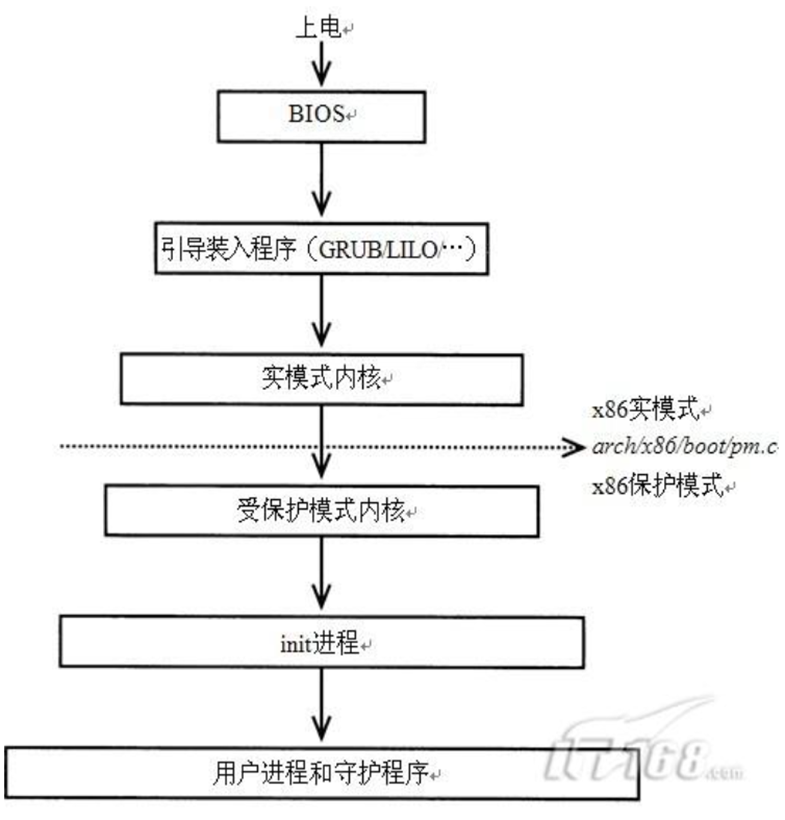

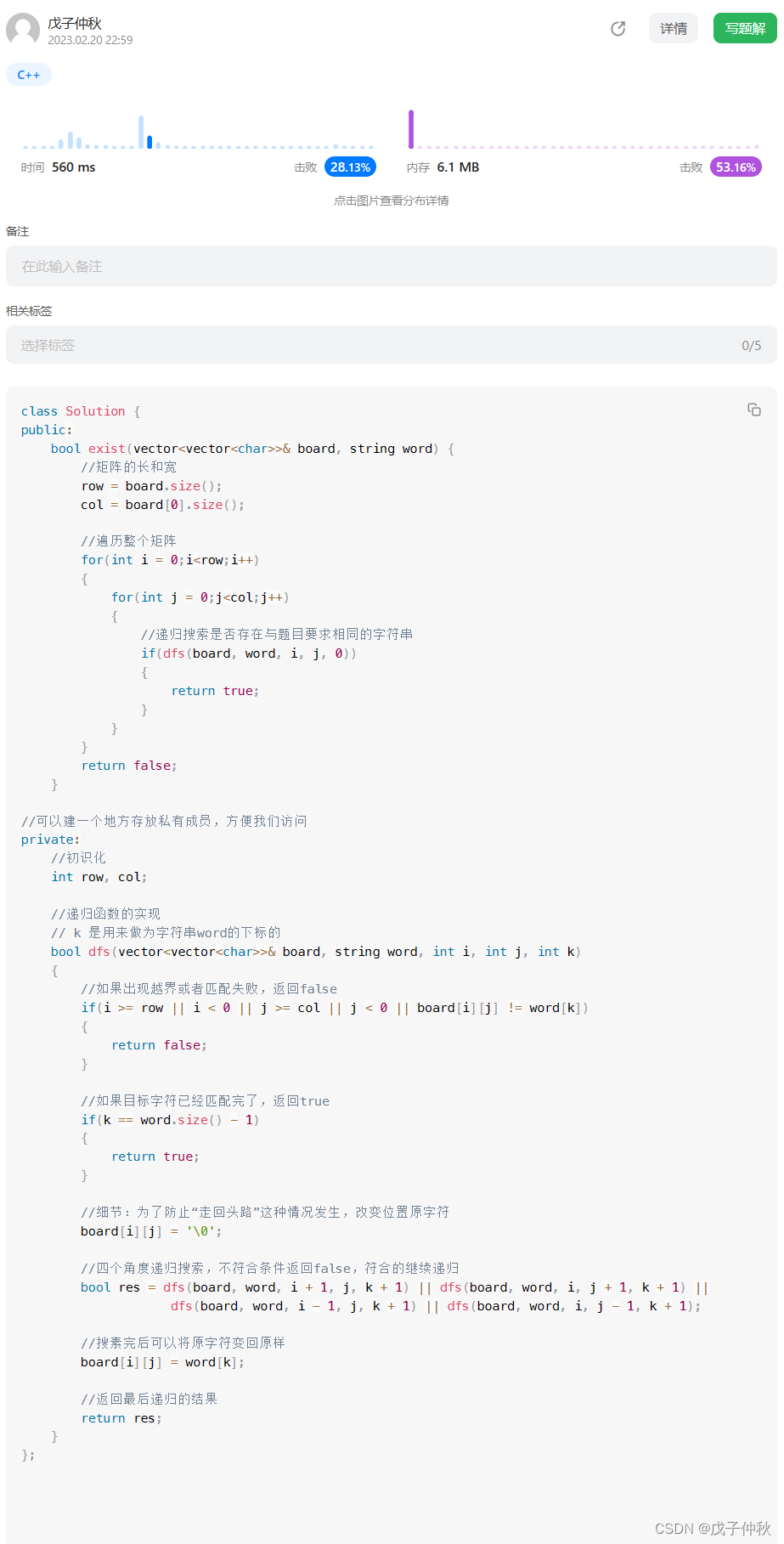

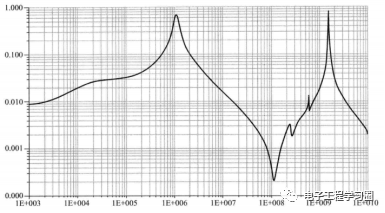

对电源与地平面间的阻抗特性分析可以采用仿真软件进行,可以得到一个PDN(电源分配网络)的输入阻抗,例如下图所示:

PDN网络的输入阻抗

由于不能确定电源的负载电流工作频点,设计要求整个频率范围内都要满足PDN的目标阻抗。虽然因去耦的需求会使用更多的电容,但是使设计具有广泛的实用性。

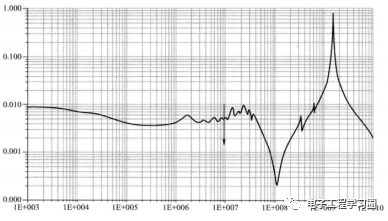

如下图所示是上图例子中加入高低频去耦电容后的PDN网络的频率阻抗特性:

加入高低频去耦电容后的PDN网络的频率阻抗特性

PI分析的设计实现方法

1.电源供电模块VRM设计

供电模块VRM一般放置在电源入口,指DC/DC和LDO,对于此类电路的噪声是由稳压芯片决定的,只能根据Datasheet进行详细设计,合理布局布线。

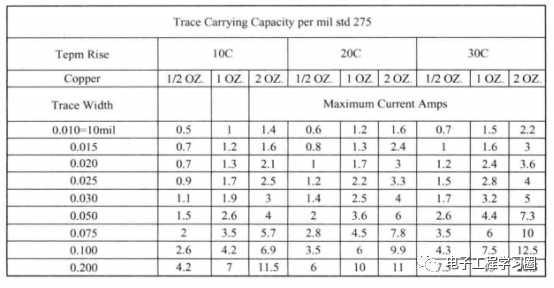

2.直流压降及通流能力

此类噪声主要由走线的直流电阻与寄生电感造成,需要考虑线路板过孔的通流能力,同时也要考虑线宽与电流的关系,如下图所示。

当电流通过狭窄区域时,会产生较大的电流密度,从而导致PCB局部温度升高。我们应该使板上的电流密度分布均匀,最大值不要超过常用的经验门限(100A/mm2),避免出现走线局部电流密度大导致热可靠性问题。

常温下铜皮走线的最大通流能力

3.电源内层平面的设计

PCB内层的电源平面不但可以给器件提供电源,还为信号提供回流。电源平面和地平面都可以作为信号的回流路径,但地信号在单板的分布比单一电源网络要广,地过孔在PCB广泛分布,回流信号会沿着地孔回流到另一个地平面。

电源平面和地平面会构成平面电容,且随着平面距离越小,容值越大,这为高速信号门电路的快速翻转提供能量保障。因此在PCB叠层设计时,应尽可能使电源平面与地平面成对出现且距离接近,距离一般控制在5mil内,最大不超过10mil。若电源平面和地平面之间的距离较大,则需要在芯片电源和地之间额外加去耦电容,增强电源和地平面之间的电容耦合性。

为了使电源具有良好的完整性,元器件布局时一般以相邻面为地平面参考层。在设计走线参考平面层时,尽可能让所有高速信号的参考平面都选择地平面为参考平面。增加地平面参考层是改善信号质量及PCB EMC特性的有效设计方法。信号层需要避免直接相邻,防止信号互相干扰,如无法避免则两个信号层之间走线应采用横平竖直的走线,不重叠走线,增大两个相邻信号层之间的间距。

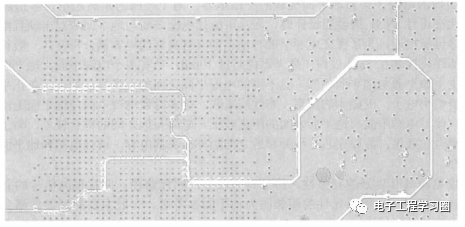

对于BGA类供电电源,有时需要在一个电源平面上布置多个电平的电源,这就需要进行电源平面的分割。分割时应尽可能使各平面的边界形状规则,面积尽可能大。举例如下图所示:

电源平面的分割

电源平面分割要注意:

1.分割方式要简洁合理,满足载流能力

2.考虑不同电压平面之间的爬电距离,相邻的不同压值的电源平面电压值差越大,爬电距离也应设计得越大

另外,整理了一些电子工程类的资料,分享给大家,目前有模拟电路、单片机、C语言、PCB设计、电源相关、FPGA、EMC、物联网、Linux相关学习资料,还有针对大学生的资料包,后续还会有更多资料分享给大家,助力大家学习,成就梦想~

链接可在往期文章中找(在文章的最后有链接)~

模拟电路设计的九个级别,你是模电几段?