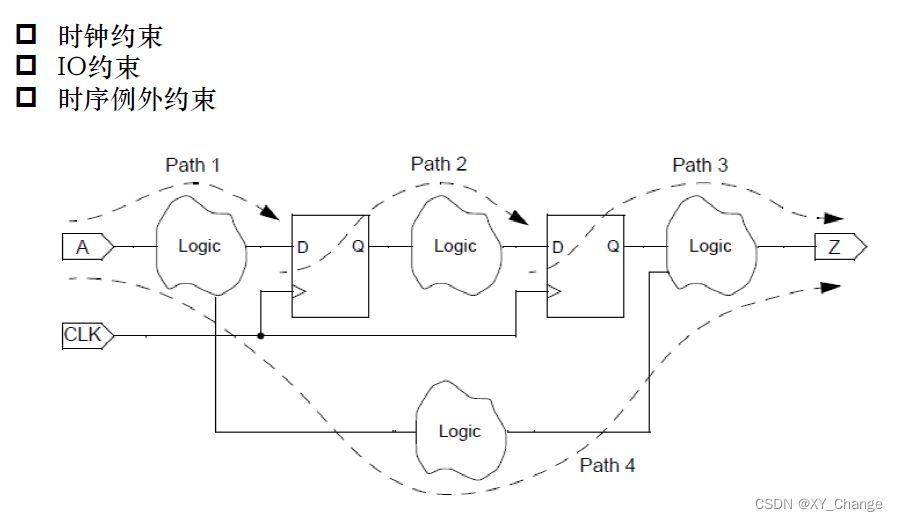

本篇博文讲了三个内容:时序约束基本概念、时序约束命令、时序收敛技巧

时序约束基本概念

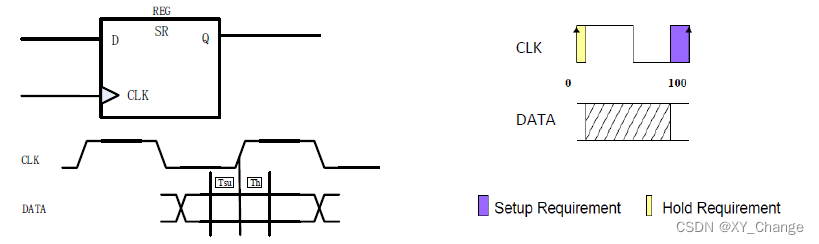

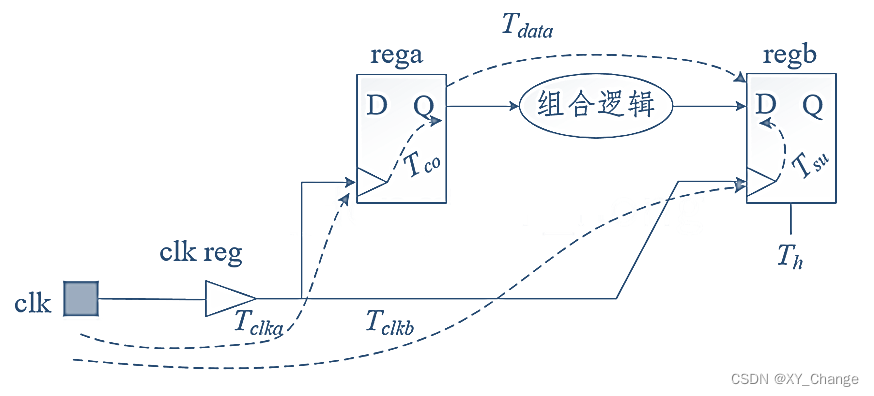

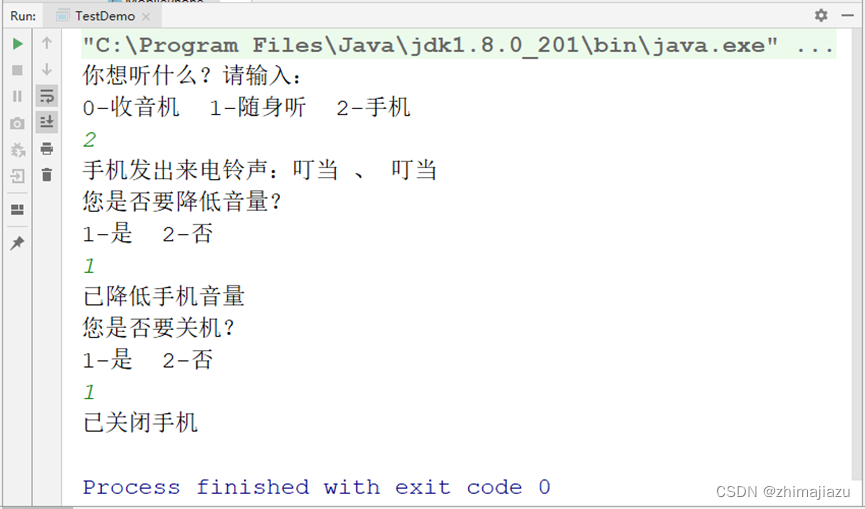

时序设计的实质就是满足每一个触发器的建立(setup)时间和保持(hold)时间。

建立时间(Tsu)

触发器的时钟信号沿到来以前,数据需要稳定的时间。

保持时间(Th)

触发器的时钟信号沿到来以后,数据稳定不变的时间。

Launch Edge

源端寄存器发送数据的时钟边沿。

Latch Edge

目的寄存器捕获数据的时钟边沿,也叫Capture Edge

Tco

时钟到输出的延时时间

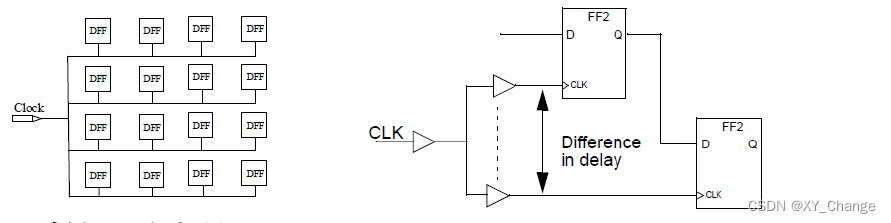

延时偏差Skew

时钟源到不同DFF时钟总输入端的延时差异,这个Skew的存在,会对DFF的时序造成影响。比较坏的情况可能会使得DFF的

setup或hold时序要求无法满足。

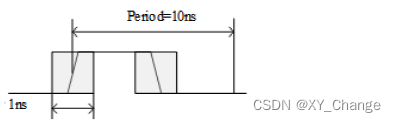

时钟不确定性

时钟不确定性是时钟沿的实际到达时间与理想到达时间,可能存在的偏差。主要因素为时钟抖动,

在FPGA器件中,抖动包含有三种,分别是输入抖动、周期抖动、系统抖动。

发起沿与捕获沿通常差一个时钟周期(共用时钟情况下)

![[Pytorch] Linear层输出nan](https://img-blog.csdnimg.cn/7cd1833b617841f8b29fb1f69f18b489.png)