Makefile逻辑

Makefile就是将一系列的工作流串在一起自动执行,构成Makefile最基本的要素是目标、依赖、命令。也就是为了实现目标需要哪些依赖并执行什么样的命令。

target: dependences1 dependences2 ...

command1 command2 ...

其中,target表示要生成的目标,dependences表示生成target需要的依赖,而command就是生成target要执行什么命令。在格式上,命令所在行行首都有一个。

比如对于c语言来讲,生成.o文件需要.c源文件,而生成目标二进制文件又需要.o文件。

test: test.o

gcc -o test test.o

test.o: test.c

gcc -c test.c -o test.o

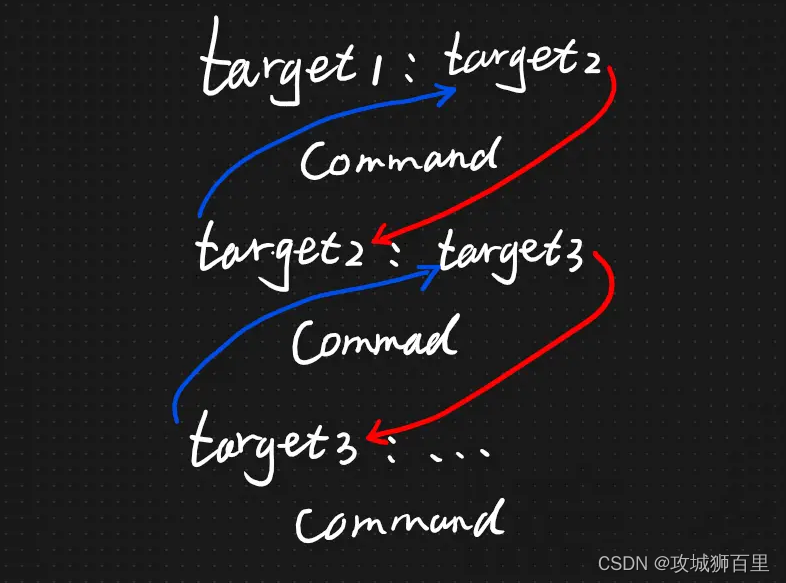

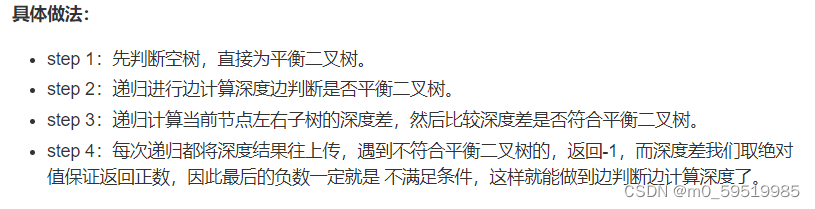

通过上面的例子我们隐约可以感觉到Makefile的解析过程,有点类似函数的递归调用。总是触及到最里层的规则之后,后面的每一次返回实际上都是依赖了上一次的调用。如下图:

当然,在编写代码的时候target相互之间的顺序有可能是打乱的,这里不要太死板。

Makefile的核心逻辑就是上面这点东西,而Makefile的创建有两种方式。

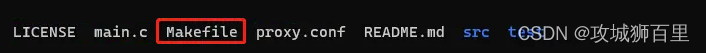

第一,将文件名命令为"Makefile",然后在Makefile文件所在的目录直接使用make命令就可以自动解析"Makefile"文件的内容。比如下面是我自己的一个c语言项目的Makefile。

第二,任意命名,比如我们使用一个叫makefile_test的文件来编写Makefile内容。在执行make的时候使用-f参数指定文件名。如下:

$ make -f makefile_test

当然,Makefile还支持引用其它的Makefile,格式如下:

include <filename>

伪目标

有些时候,我们希望不生成具体的目标文件,只想执行命令,比如在Linux通过源码安装经常会使用make clean来清除安装产生的额外的中间文件,比如:

test: test.o

gcc -o test test.o

clean:

rm -rf *.o test

按照Makefile的规则clean也是一个目标,但我们不希望生成clean目标文件,就可以使用.PHONY将其声明为伪目标,表示只执行命令,不生成目标文件。例如:

.PHONY: clean

test: test.o

gcc -o test test.o

clean:

rm -rf *.o test

当一个Makefile有多个目标的时候,可以通过参数来指定要执行哪个目标,比如上面的clean:

$ make clean

Makefile变量

Makefile也支持变量,使用上和Shell中的变量很相似,比如:

BUILDDIR=./build

...

build:

mkdir -p $(BUILDDIR)

...

上面声明了一个变量BUILDDIR,然后在build目标中使用$(BUILDDIR)来引用变量。Makefile中变量可以分为三大类:默认变量、自定义变量和自动变量。\

1. 默认变量

默认变量是Makefile的约定,比如:

test: $(CC) -o test test.c

其中CC就是一个默认变量,在linux下就是编译器cc。其它比较常用的默认变量如下:

关于命令相关的变量

AR: 函数库打包程序。默认命令是arAS: 汇编语言编译程序。默认命令是asCC: C语言编译程序。默认命令是ccCXX: C++语言编译程序。默认命令是g++CO: 从 RCS文件中扩展文件程序。默认命令是coCPP: C程序的预处理器(输出是标准输出设备)。默认命令是$(CC) –EFC: Fortran 和 Ratfor 的编译器和预处理程序。默认命令是f77GET: 从SCCS文件中扩展文件的程序。默认命令是getLEX: Lex方法分析器程序(针对于C或Ratfor)。默认命令是lexPC: Pascal语言编译程序。默认命令是pcYACC: Yacc文法分析器(针对于C程序)。默认命令是yaccYACCR: Yacc文法分析器(针对于Ratfor程序)。默认命令是yacc –rMAKEINFO: 转换Texinfo源文件(.texi)到Info文件程序。默认命令是makeinfoTEX: 从TeX源文件创建TeX DVI文件的程序。默认命令是texTEXI2DVI: 从Texinfo源文件创建TeX DVI 文件的程序。默认命令是texi2dviWEAVE: 转换Web到TeX的程序。默认命令是weaveCWEAVE: 转换C Web 到 TeX的程序。默认命令是cweaveTANGLE: 转换Web到Pascal语言的程序。默认命令是tangleCTANGLE: 转换C Web 到 C。默认命令是ctangleRM: 删除文件命令。默认命令是rm –f

关于命令参数的变量

ARFLAGS: 函数库打包程序AR命令的参数。默认值是rvASFLAGS: 汇编语言编译器参数。(当明显地调用.s或.S文件时)CFLAGS: C语言编译器参数。CXXFLAGS: C++语言编译器参数。COFLAGS: RCS命令参数。CPPFLAGS: C预处理器参数。( C 和 Fortran 编译器也会用到)。FFLAGS: Fortran语言编译器参数。GFLAGS: SCCS “get”程序参数。LDFLAGS: 链接器参数。(如:ld)LFLAGS: Lex文法分析器参数。PFLAGS: Pascal语言编译器参数。RFLAGS: Ratfor 程序的Fortran 编译器参数。YFLAGS: Yacc文法分析器参数

2. 自定义变量

前面我们声明的BUILDDIR就是一个自定义变量,要注意的是,如果声明了一个和默认变量一样的变量就会覆盖默认变量,这也给我们提供了一个改变默认规则的入口。

自定义变量要注意的是赋值方式,在Makefile中有以下几种赋值方式:

=延迟赋值,在Makefile运行时才会被赋值:=立即赋值,立即赋值是在真正运行前就会被赋值?=空赋值,如果变量没有设置过才会被赋值+=追加赋值,可以理解为字符串的加操作

延迟赋值指的是在Makefile运行时再赋值。

立即赋值和我们的直觉一致

空赋值,是指如果变量没有设置的情况下才会赋值,空赋值只会在变量没有设置的时候才有效

3. 自动变量

Makefile有很多自动变量,这里只介绍几个常用的,分别是<、<、^、$@,其它的可以去参考Makefile文档。

$< 表示第一个依赖的文件,例如:

test: test.o test2.o

echo $<

test.o:

test2.o:

最终结果是test.o,也就是test第一个依赖。

$^ 表示所有依赖,还是上面的例子,例如:

test: test.o test2.o

echo $^

test.o:

test2.o:

最终结果是test.o test2.o,是test全部的依赖。

$@ 表示目标,上面的例子:

test: test.o test2.o

echo $@

test.o:

test2.o:

最终结果是test,也就是Makefile中的test。

Makefile规则

在Makefile中有一些约定俗成的规则,正是这些规则的存在可以大大减少Makefile代码长度,这里我只列出了我认为比较重要的四个规则。

1. 隐含规则

这里以c语言的规则举例,先来看一段Makefile:

main: main.o test.o

cc -o main main.o test.o

在当前目录下,只有main.c和test.c两个文件,并没有.o文件,上面的Makefile之所以能运行,是因为它的隐含规则。对于c语言来讲,如果有地方依赖.o文件,会自动去寻找相同名称的.c文件,并构建出.o文件。

当然隐含规则远没有这么简单,比如Makefile还支持多个步骤的隐形规则链,但这里我们只需要了解到这一步,后面可以查看理详细的文档去深入了解。

2. 通配符

Makefile中支持*、?、三个通配符,其意义和shell中的通配符基本一致。比如表示宿主目录。例如在make clean的时候清除编译中产生的.o中间文件,如下:

clean:

rm -rf *.o

3. 模式匹配

在Makefile中模式匹配使用%来实现,表示匹配任意多个非空字符,相当于shell中的*。模式匹配有什么用呢?假如现在有非常多的.c源文件要生成目标.o文件,我们可以像下面这样写:

%.o: %.c

cc -c %^ -o $@

上面的意思是将所有.c文件都经过编译器编译生成.o文件,其中表示的是所有的依赖,在上面的场景中就是当前目录下所有.c文件。而^表示的是所有的依赖,在上面的场景中就是当前目录下所有.c文件。而表示的是所有的依赖,在上面的场景中就是当前目录下所有.c文件。而@表示目标文件。也就是%.o所代表的所有文件。可以看到模式匹配可以大幅减少Makefile的代码量。

4. 文件搜索

在比较大的工程中,程序可能会有特别多的依赖,Makefile默认会在当前目录下搜索依赖,但是绝大多数情况依赖可能分布在多个目录中,Makefile的VPATH变量可以帮助我们解决依赖搜索的问题,比如:

VPATH=src:../headers

表示Makefile会从src和…headers目录去搜索依赖文件。

VPATH还支持模式匹配,比如

VPATH <pattern> <directories>

比如,下面就表示在headers目录找所有.h文件

vpath %.h headers

还可以通过模式匹配清除搜索目录。注意,这里说的是清除。

VPATH <pattern>

或者清除所有已设置好的目录。

VPATH

Makefile条件分支

Makefile条件分支比较简单,就ifeq和ifneq。比如:

ifeq ($(ARCH), x86)

CC=gcc

else

CC=arm....gcc

endif

这个比较好理解,而ifneq的使用和ifeq几乎是一样的,可以自己试一下。

Makefile函数

Makefile提供了很多内置函数,但这里我只讲其中我认为比较重要的4个函数,分别是:

1. patsubst : 模式匹配与替换

patsubst的原型如下:

$(patsubst <pattern>,<replacement>,<text>)

其语义是,在text中寻找符合pattern模式的内容替换成replacement的模式。这个函数非常有用,还是以c语言为例,在没有生成.o文件之前我们可以通过.c格式的原文件替换最终得到一组.o文件名。比如:

OBJECTS=$(patsubst %.c,%.o, main.c test.c)

最终main.c和test.c会被分别替换成main.o和test.o,然后将结果赋值给变量OBJECTS。

2. notdir : 去掉路径中的目录

notdir的原型如下:

$(notdir <text>)

有时候我们拿到的是一个文件的全路径,但我们只想要文件名,就可以使用notdir函数,比如src/foo.c,我们只想要foo.c,就可以这样写:

FOO=$(notdir src/foot.c)

3. wildcard : 匹配文件

如果我们要从一堆文件里面挑出符合条件的那部分就可以使用wildcard,它的原型如下:

$(wildcard <pattern>)

比如我们想找出所有.h文件

INCLUDES=$(wildcard *.h)

注意,这里使用的通配符是"*",这里表示在当前目录找到所有.h文件。

4. foreach : 批量处理

foreach可以重复相同的逻辑去处理一批数据,它的原型如下:

$(foreach <var>,<list>,<text>)

比如我们要一次性找到a、b、c三个目录下的所有.c文件,就可以这样写:

DIRS:=a b c

FILES=$(foreach dir, $(dirs), $(wildcard $(dir)/*.c))

foreach的参数有三个,我们分别来看一下

- 表示从中遍历出来的每一项

- 是被遍历的原数据列表,可以类比c语言中的数组

-

在text中是可以引用 的也可以使用其它函数, 就是foreach函数处理之后的结果,如果 中有函数就是函数运行之后的结果。

好了,到这里我们所需要的前置知识都有了。下面来通过一个实际项目将上面的知识点串在一起,实现一个相对比较复杂的Makefile。

C++后端开发学习教程:https://ke.qq.com/course/417774?flowToken=1031343

![[数据结构笔记]常见排序算法](https://img-blog.csdnimg.cn/7d5398cccf204d0ea6c9410f9eed400f.png#pic_center)