运动控制器是数控机床

、

高端机器人等自动化设备控制系统的核心

。

为保证控制器的实用性

、

实时性和稳定 性,

提出一种以

STM32

为主控制器

、

FPGA

为辅助控制器的多轴运动控制器设计方案

。

给出了运动控制器的硬件电路设计

, 将 S

形加减速算法融入运动控制器

,

提高了控制精度

,

可有效避免过冲

、

振荡等现象的发生

。

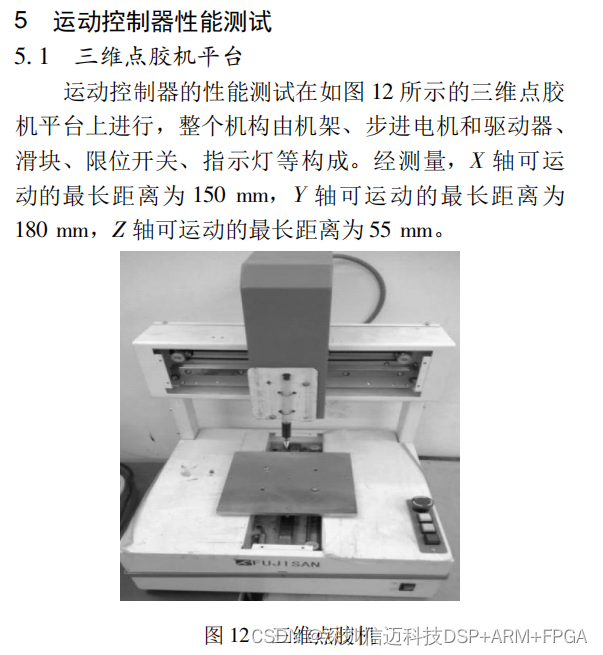

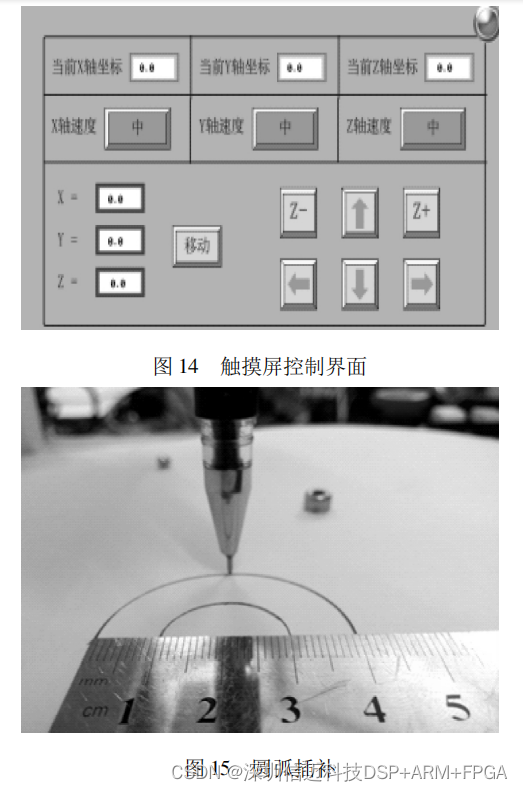

在三维点胶机平台上对运动 控制器的性能进行了测试,

结果表明

:

点胶机各轴能按照设定的轨迹运动

,

运行平稳且实时性高

,

具备良好的应用前景

。

运动控制器性能的好坏直接对自动化系统整体性能的 发 挥 起 决 定 性 作 用[1-2]

。

克 莱 斯 勒

、

西 门 子

、 FANUC、

MAZAK

占据我国

90%

左右的工业用运动控 制器市场。

随着运动控制技术的发展

,

FPGA

、

ARM

、 DSP、

专用芯片等逐渐成为运动控制器的核心部件

, 并日益朝着开放式方向发展[3-4]

。

以单片机为核心的运动控制器运算速度慢、

控制精度低

,

一般用于低 速、

运动轨迹简单的场合

;

以专用芯片为核心的运动 控制器只是发出脉冲信号,

无法接收反馈信号

,

处于开环状态,

不能满足多轴联动和高速

、

高精度的轨迹 插补要求[5-7]

。

基于

PC

的以

FPGA

、

ARM

、

DSP

为核心处理器的运动控制器,

如固高科技

GH-800

,

数据处理速度快、

实时性高

,

可完成多轴协同控制

、

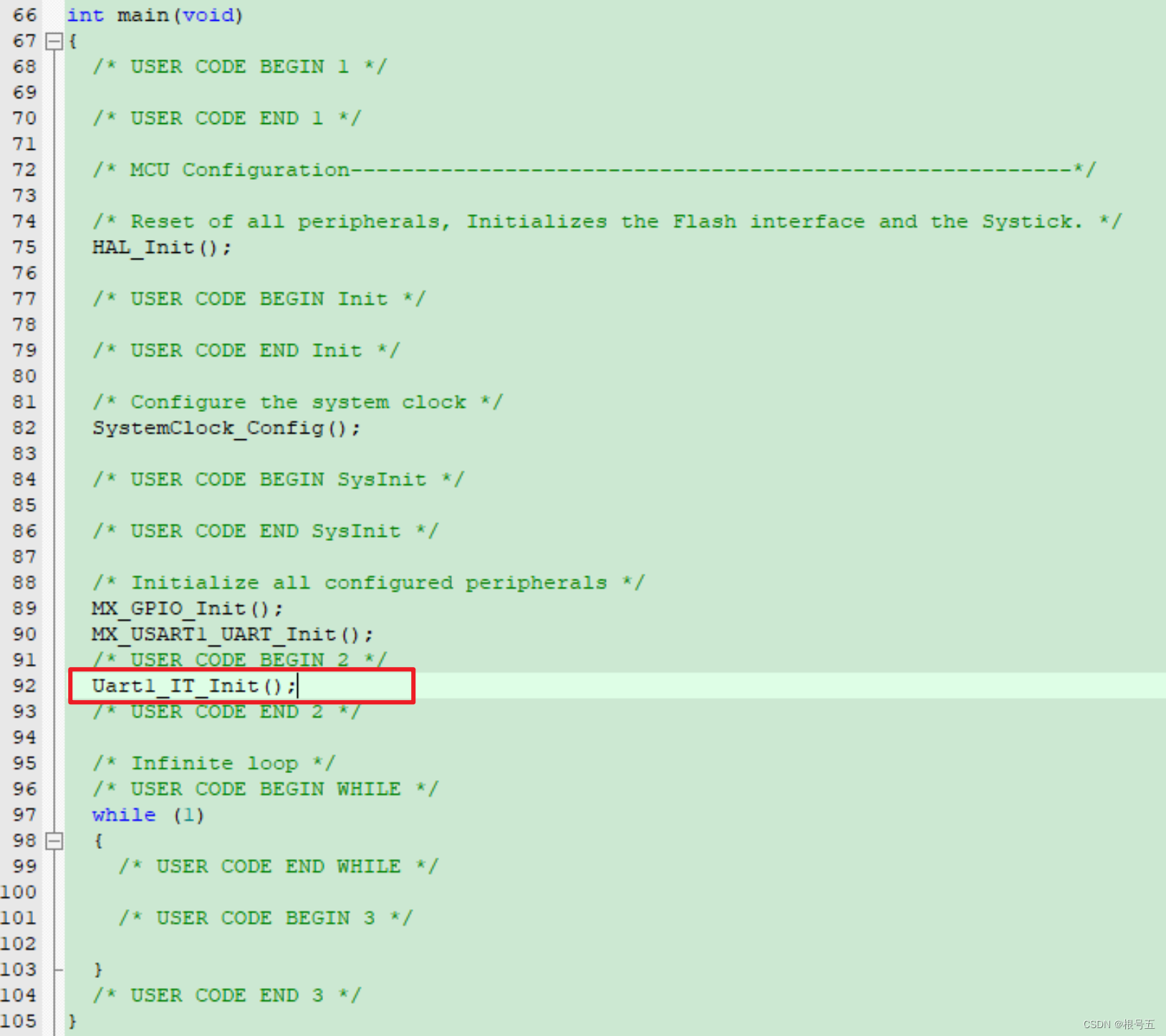

复杂轨迹运动和加减速。 以 STM32

为主控器

、

FPGA

为辅助控制器

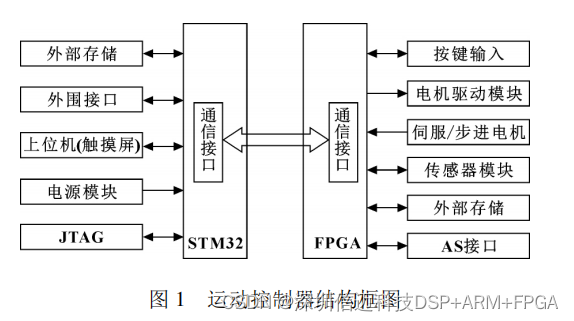

,搭建硬件平台及进行外围电路设计。利用 STM32 丰富的外设资源,完成运动轨迹规划、人机交互、数据存储、数据交互等控制; 利用 FPGA 丰富的逻辑资源,实现各个运动轴脉冲并行输出、输入信号和原点位置的检测、输出开关量控制等功能。控制器设计中引入S 形加减速算法,可有效避免实际运行过程中的过冲、失步及振荡等现象。该运动控制器硬件结构简单,在保证精度、实时性、可靠性的前提下,能有效缩短研发周期。

1

运动控制器结构

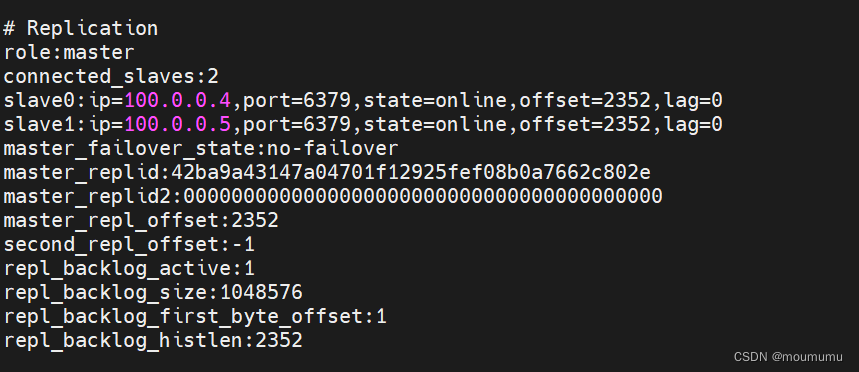

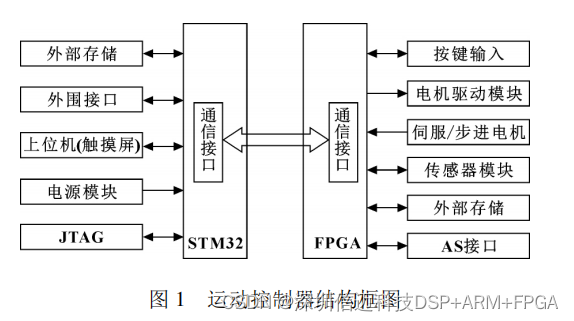

运动控制器采用

STM32+FPGA

的硬件结构形式

,主控制芯片选用 ST

公司的

STM32F4xx

,

辅助控制芯片选择 Altera

公司的

EP2

系列芯片

。

主要模块包括数据存储 模 块、

外部输入检测模块

、

电 机 驱 动 模块、

接口模块

、

人机交互模块等

,

其结构框图如图1 所示

。

主控制器以

STM32

为核心

,

将电机运行过程中的数据存入外部存储器,

使用触摸屏和按键相结合的方式实现人机交互;

触摸屏作为上位机

,

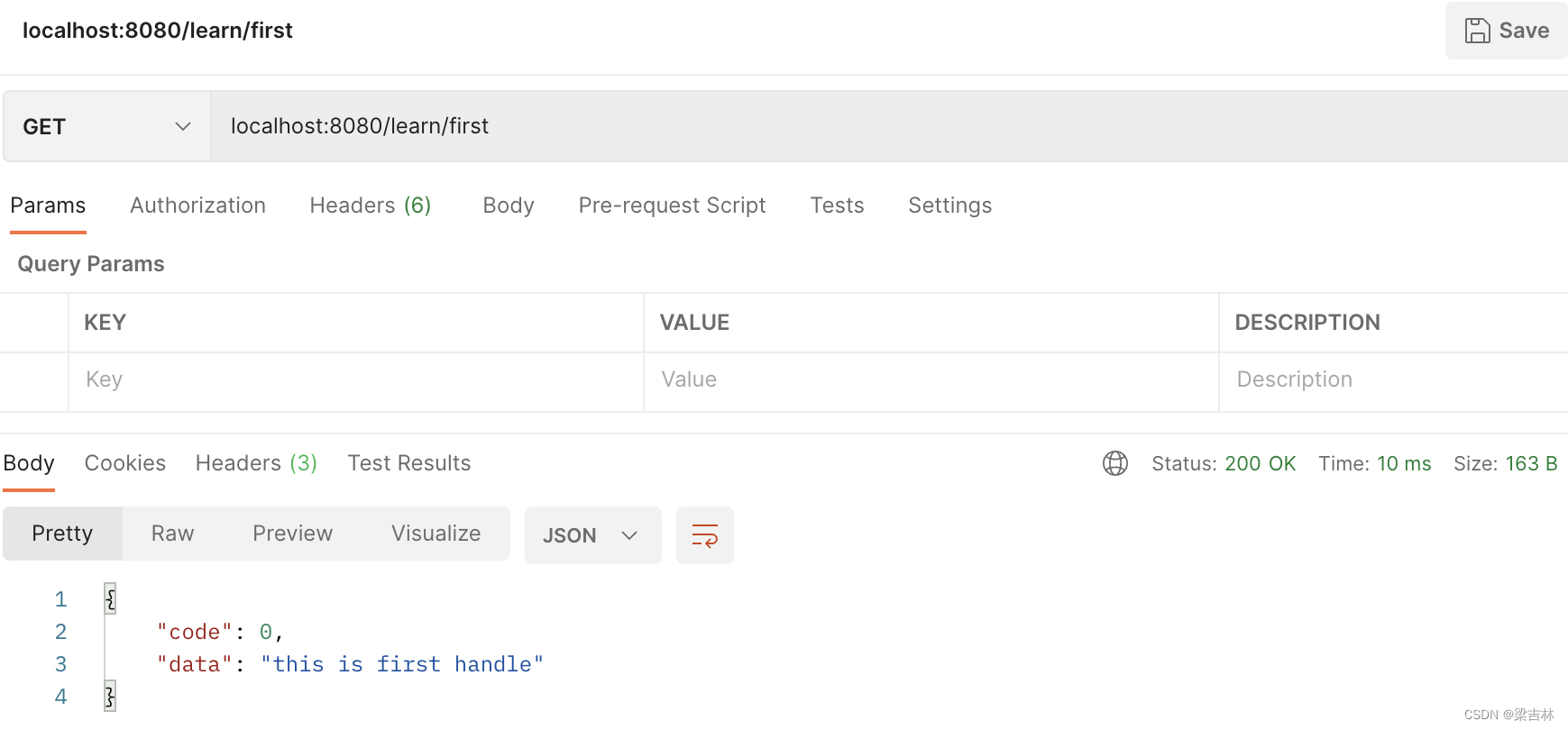

通过串口与 STM32 通信

,

可对整个系统进行调试

,

按键通过

I/O 接口与 FPGA

相连

。

主控制器处理外部数据存储器的插补信息后,

经总线发送给

FPGA

,

FPGA

接到控制指令或插补数据后进行插补运算,

然后通过隔离电路将信号发送到各个电机驱动器,

对各轴电机进行驱动,

完成目标运动轨迹.

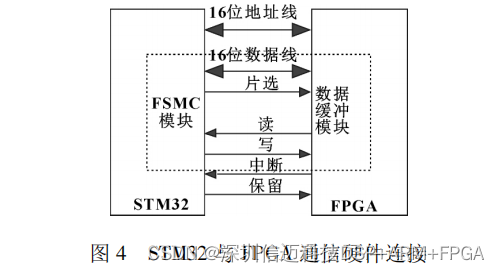

STM32

与

FPGA

的通信接口

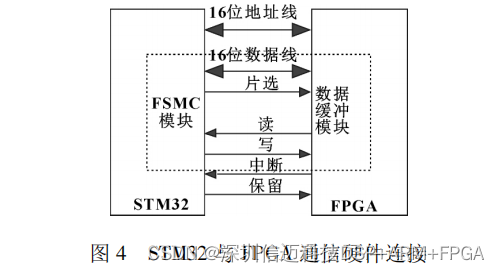

STM32

与

FPGA

之间可以通过可变静态存储控制器 (

Flexible Static Memory Controller

,

FSMC

)

进行通信,

如图

4

所 示

。

根 据

FSMC

的 功 能 特 性

,

设 定STM32 的地址线和数据线宽度为

16

位

,

STM32

片选选中 FPGA

进行数据读写

,

FPGA

通过中断反馈数据处理情况。

STM32

芯片的配置

STM32

芯片外围硬件看门狗能有效监控

CPU

的运行情况。

STM32

需要配置

2

个外部晶振

:

一个频率为 32. 768 kHz

,

主要给芯片内部时钟部件提供低速

、 高精度的时钟;

另一个频率为

25 MHz

,

产生主时钟

,通过分频、

倍频模块后供给各个模块

[4,6]

。

2. 2

FPGA

模块电路设计

FPGA

主要负责插补算法信息的处理

、

脉冲信号的输出、

开关量的输入和输出

、

接收编码器的差分信 号等。

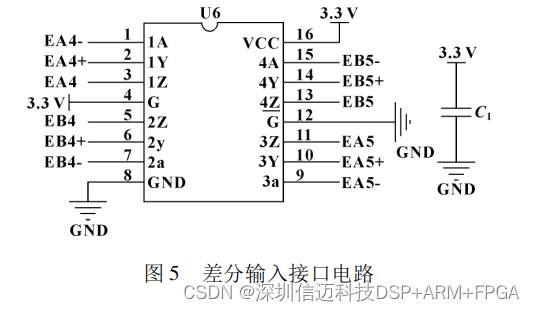

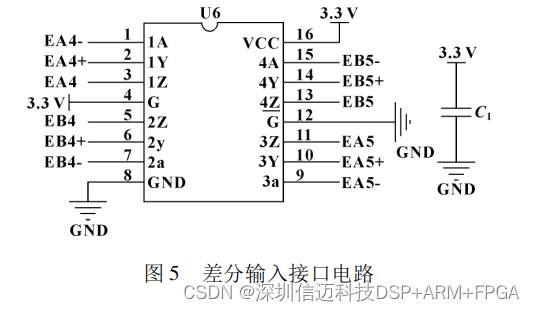

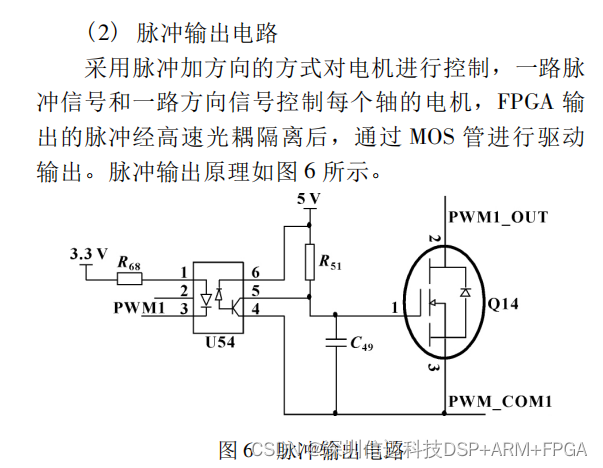

(

1

)

差分输入接口电路

U6

为四路差动信号接收器

,

用来接收编码器输出的差分信号,

将电机的位置信息反馈给

FPGA

。

接口电路如图 5

所示

3

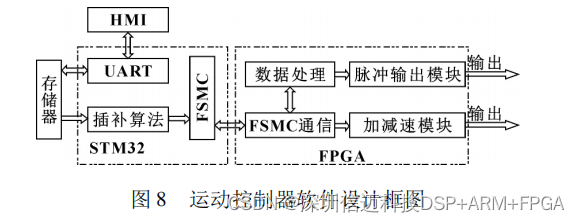

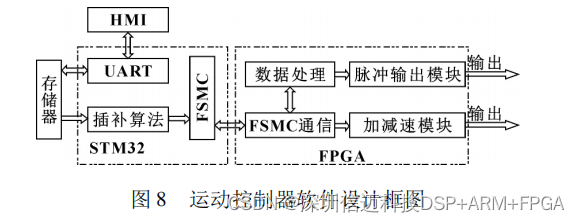

运动控制器软件设计

通过触摸屏

(

HMI

)

发送指令给

STM32

,

STM32 接收到指令后通过动态链表的形式将指令存储于外部存储器;

实时读取存储器

,

将运动轴的位置信息

、

速度信息返回给触摸屏显示,

同时将指令信息和插补算法数据,

由

FSMC

传到

FPGA

处理

;

最后由脉冲发生器产生脉冲指令给电机驱动器,

驱动电机转动

。

运动控制器软件设计框图如图 8

所示

。

4

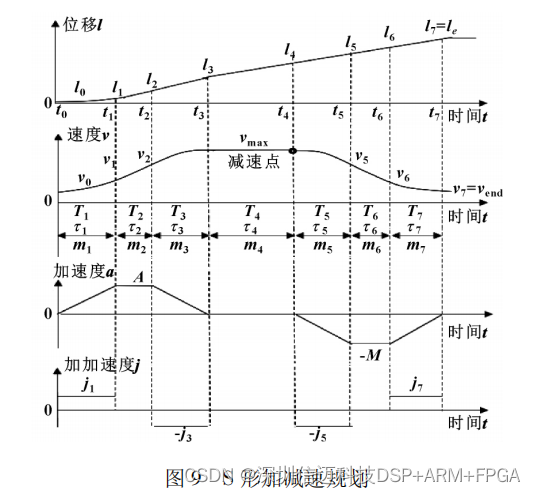

S

形速度规划算法的实现

S

形加减速可充分发挥电机性能

,

因其在加减速阶段速度曲线呈 S

形而得名

。

令加速度的导数为常 数,

改变其 大 小

,

可最大限度减小系统冲击

[10-11]

。 整个加减速过程由 7

个部分构成

[12-13]

,

如图

9

所示

。 图中:

l

为运动的位移

,

v

为速度

,

a

为加速度,j 为

加加速度

,

A

表示匀加速阶段的加速度值

,

M

表示匀减速阶段的加速度值,

T

i

(

i

= 1

,

2

,

3

,......,

7

)

为各阶段的运行时间,

τ

i

(

i

= 1

,

2

,

3

,

......

,

7

)

为以各个起点作为 0

点的时刻

,

t

i

(

i

= 1

,

2

,

3

,

......

,

7

) 为各个过渡点时刻。

实际应用时

,

m

1

~

m

4

的各阶段

都需要判断减速点

,

一般情况下

,

从

0

加速到最大速度和从最大速度减速到 0

所用的时间相同

,

即

T

1

= T3

、

T

5

=

T

7

。

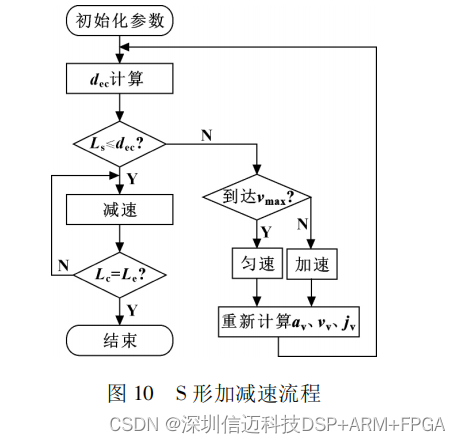

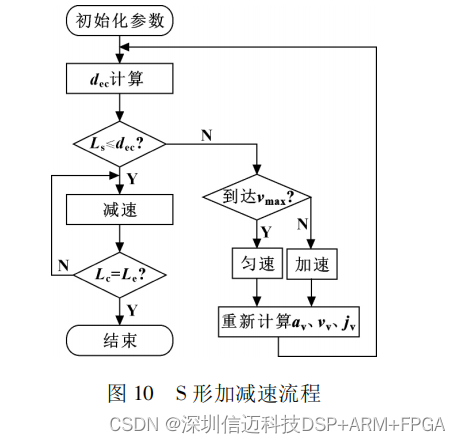

结合图

10

所示的流程

,

算法实现过程如下

:

步骤

1

,

初始化相关的参数

,

包括初始速度

、

目标速度 (

最大运行速度

)

、

加加速度

j

、

最大加速度

A

。

步骤

2

,

计算减速距离

d

ec

,

将

d

ec

与剩余距离

L

s 比较,

其中

L

s

=

L

e

-

L

c

,

L

e

表示指定目标位置值

、

L

c 表示当前位置值。

步骤

3

,

若

L

s

>

d

ec

则减速

,

否则加速或者匀 速 ( 此时如果到达最大速度则匀速

,

未到达则加速

)

。

步骤

4

,

根据步骤

3

的判断

,

重新计算

a

v

、

v

v

、jv 并输出。

步骤

5

,

当

L

c

=

L

e

时

,

到达终点

,

运动停止

,

否则重复步骤 2~ 5

。

6

结束语

本文作者提出了一种以

STM32

为主控制器

、

FPGA 为辅助控制器的运动控制器设计方案

,

完成了控制器硬件平台及外围电路设计,

将

S

形加减速控制算法融入到运动控制器中,

有效避免了运动时由于速度突变引起的过冲、

抖动等现象

,

提高了控制精度

。

对运动控制器进行测试,

结果表明

:

以

STM32+FPGA

为硬件架构的运动控制器实时性好、

可靠性高

,

能满足工业运动控制的要求。

信迈支持STM+FPGA运动控制器、ethercat总线定制。