一、概述

pcie的参考时钟由板级输入,提供给IP内PHY层的PLL使用,由PLL产生core_clk和pipe_clk。

二、REFCLK产生方式

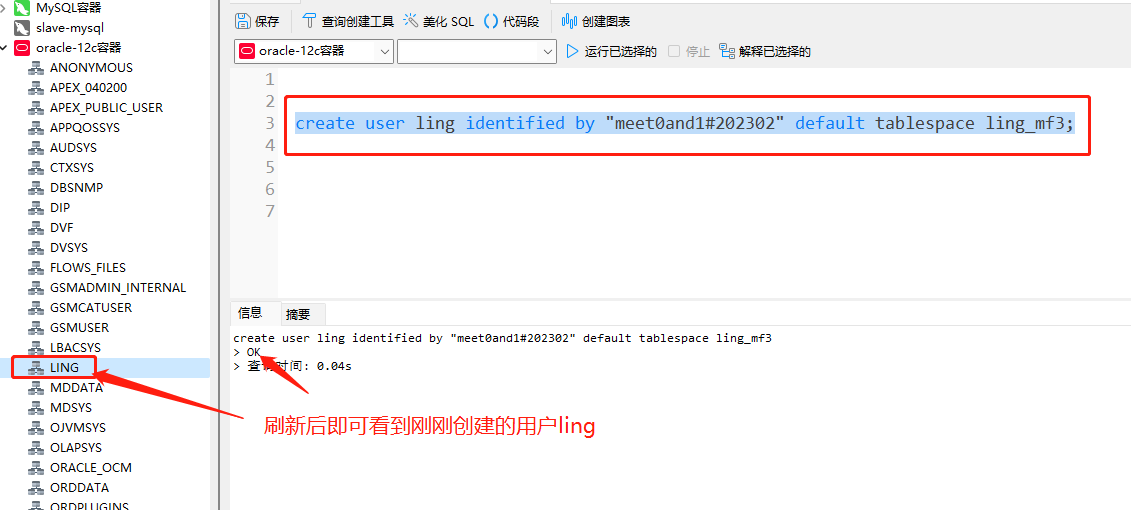

Serdes 所用时钟由 PHY 模块内的PLL生成,PLL的参考时钟可以由common clock(外部背板提供)、separate clock(自身板级提供)或从接收数据流中恢复出来。常用的common clock模式,该模式支持时钟扩频,对时钟要求不如separate clock高。

参考时钟架构可参考链接:PCIe 参考时钟架构 (Refclk Architecture)

2.1 共用时钟架构

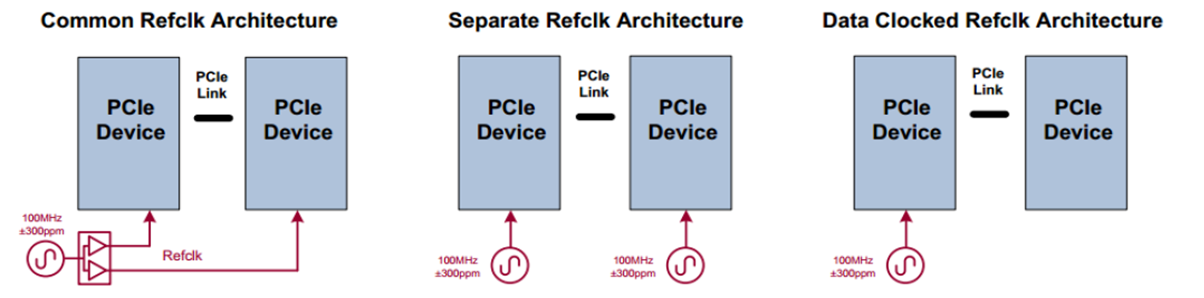

2.2 CDR时钟数据恢复

从接收数据流中依据比特锁定恢复时钟。该方案仅适用于Gen2和Gen3。

通过比特锁定实现时钟恢复。

- 比特锁定

由于发送方使用8/10 bit编码,保证了串行字符流具有频繁的0/1转换,接收方PLL在已接收的比特流使用改转换来同步接收时钟和发送时钟(发送器使用发送时钟来输出已串行化的字符比特序),当接收器的PLL锁定到发送时钟频率上时,则称接收器实现了“比特锁定”。

在链路定向时,发送器设备向接收器发送一连串TS1/2序列,接收方通过改序列实现比特锁定;一旦链路处于L0状态,则链路上会有规律的转换,接收方PLL即可维持比特锁定;当链路处于低功耗状态时,接收方PLL会逐渐丢失同步,发送方会发送电气空闲序列高职接收方不选通输入,防止数据传输错误;此时若发送方向接收方发送FTS序列,接收方则可使用这些序列重新活得比特锁定。

三、时钟干扰和去扰

通常由于板级电路的EMI电磁干扰会产生噪声,进而引起时钟jitter,导致频率不稳定,从而会导致refclk误差,PCie CEM 3.0规定refclk的误差容忍度为100M Hz(-300 ppm ~ +300 ppm),因此除了选择高质量的晶振外,设计时还需要采用一定方法减少干扰。

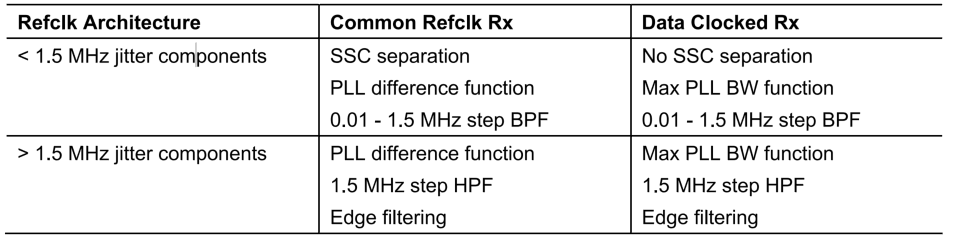

PCie CEM 3.0规定了不同jitter情况下的去扰方案。

扩频时钟调制

时钟补偿

该方法用于数据时钟恢复的refclk的产生方法。在物理层内部增加补偿电路,当接收时钟和发送时钟频率差距较大时需要进行时钟补偿。

如果发送时钟频率高于接收时钟频率达 600ppm,则从缓冲区中删除一个SKP符号;

如果发送时钟频率低于接收时钟频率达 600ppm,则向缓冲区中添加一个SKP符号。