2.1 优化性能设计

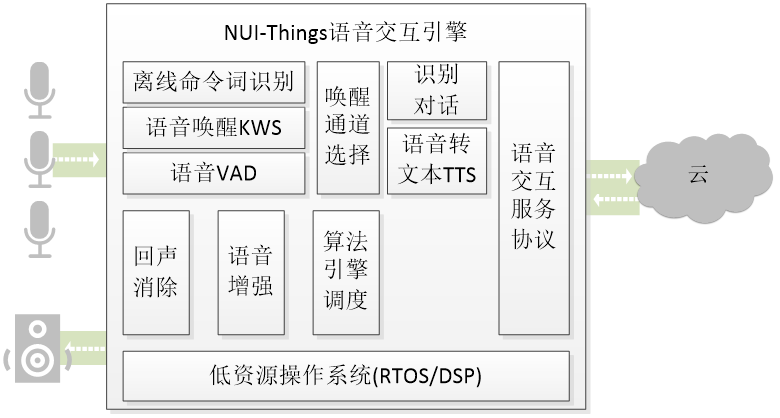

例如,当前需要微处理器强大功能的桌面应用程序包括:

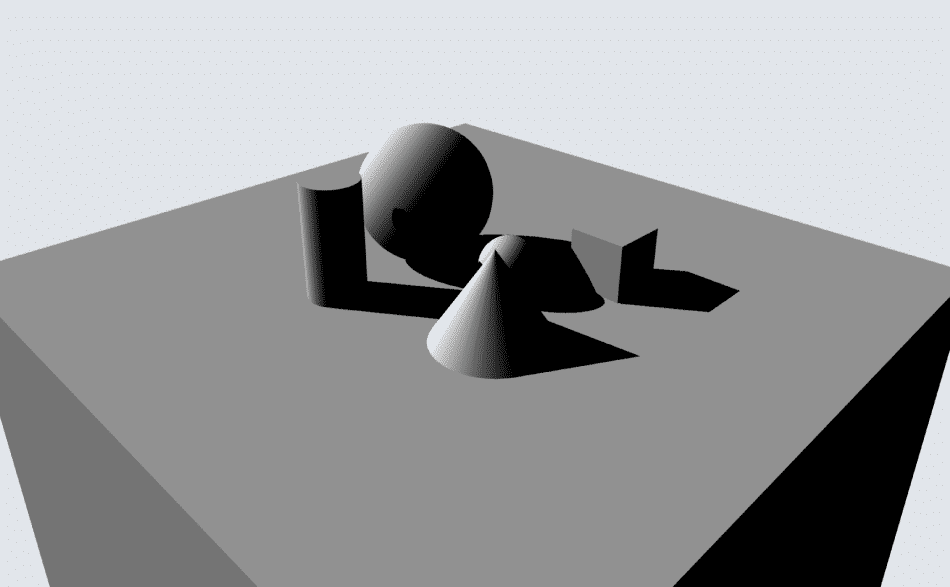

图像处理、三维渲染、语音识别、视频会议、多媒体创作、文件的声音和视频注释、仿真建模

从计算机组成与体系结构的角度来看,一方面,现代计算机的基本组成与50多年前的IAS计算机几乎一样;另一方面,从现有材料中挤出最大性能的技术变得越来越复杂。

随着对计算机各个要素和组成部分的讨论,我们追求两个目标:其一,本书解释了考虑到的每个部分的基本功能;其二,本书讨论了获取最大性能所需要的技术

2.1.1 微处理器速度

只要摩尔定律有效,芯片制造商每三年就可以推出新一代芯片--其晶体管的数量是现在的4倍。对内存芯片而言,每三年动态随机访问存储器的容量就会增加4倍,DRAM仍然是计算机主存的基本技术。

自1978年英特尔推出x86系列以来,新电路的加入以及缩短电路之间距离所带来的速度提升,使其性能每三年就能提高4~5倍。

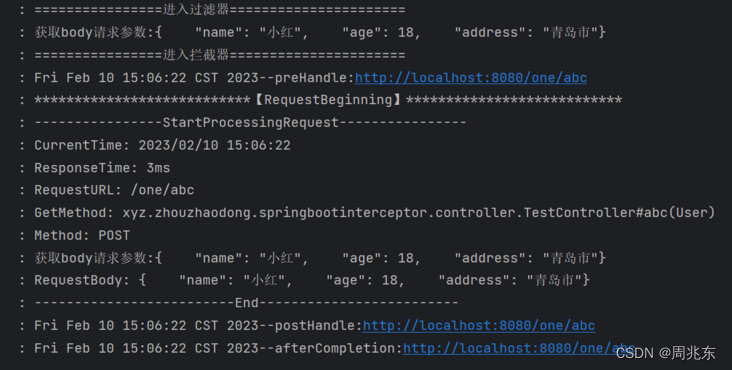

但是微处理器的原始速度无法发挥其潜力,除非是计算机指令的形式向其输入不间断的工作流。任何妨碍其顺畅流动的东西都会削弱处理器的能力。处理器设计者必须拿出越来越复杂的技术来“喂饱”这个芯片怪物。当代处理器内置的技术包括:

流水线:指令的执行涉及多个操作阶段,其中包括取指,译码,取操作数,执行计算等。流水线能够使处理器处理多条指令,这些指令在同一时间内执行不同的阶段操作。

分支预测:处理器从内存预取指令,并根据它预测未来:下一步可能处理那些分支或指令组。如果处理器大部分时间猜测都是正确的,它就能预取正确的指令并缓存它们,使得处理器保持忙碌。

超标量执行:每个处理器时钟周期内发射多条指令的能力。实际上,要使用多条并行地流水线。

数据流分析:处理器分析那些指令依赖其他指令的结果或数据,以便创建优化的指令调度。

推测执行:使用分支预测和数据流分析,一些处理器在程序执行时,可以在指令实际出现前进行预测性的执行,其结果将暂存在临时位置,让其执行单元尽可能保持忙碌。

以上这些处理器内置技术和其他复杂技术的共同作用使得每个处理器周期处理多条指令成为可能,美不是每一条指令都占用多个周期。

2.1.2 性能平衡

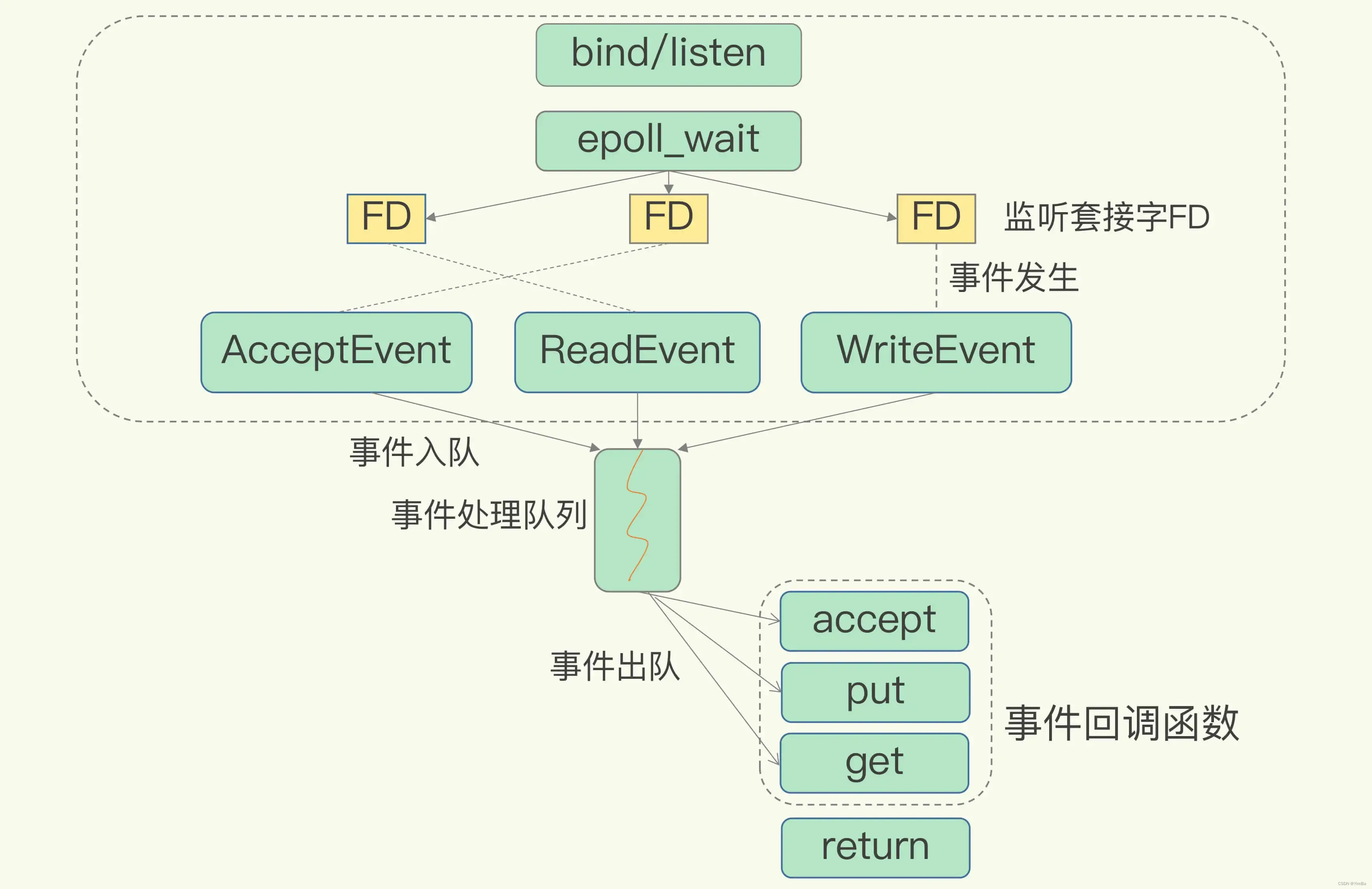

虽然处理器能力以极快的速度向前发展,但计算机的其他关键部件没有跟上发展速度。其结果就是需要寻找性能平衡:对组成和体系结构进行调整/调优,以补偿各组件之间的不匹配。

这种不匹配造成的问题对处理器与主存之间的接口来说尤为重要。因为其接口是计算机中最关键的路径,因为它负责在内存芯片和处理器之间不断传输程序指令和数据,如果该路径无法满足处理器的持续需求,处理器将会处于等待状态。

系统架构师通过多种办法来解决这一问题,所有方法在当代计算机中都有所反映。请思考下列:

让DRAM“更宽”而不是“更深”,以及使用宽总线数据路径来增加一次检索的位数;

让DRAM芯片中包含高速缓存或利用其他缓冲方法来改变DRAM接口,使其更有效。

通过在处理器核主存之间集成日益复杂和高效的高速缓存结构来减少内存访问的频率。这包括在处理器芯片上集成一个或多个高速缓存,以及在靠近处理器芯片的地方集成一个片外高速缓存。

通过使用更高速的总线以及总线层次结构来缓冲和构造数据流,增加处理器与内存之间的互联带宽。

但数据在处理器和外设之间的传输仍然是个问题。应对策略包括缓存和缓冲方案,使用更高速的互连总线,以及更复杂的 互连结构,另外,使用多处理器配置也有助于满足IO需求。

这一切关键是平衡。设计人员不断平衡处理器组件、主存、IO设备和互连结构的吞吐量与处理器需求,以应对2个不断发展的因素:

不同类型的元素在各种技术领域(处理器、总线、内存、外设)中性能变化的速度有很大的不同;

在典型指令文件和数据访问模式方面,新的应用和新的外围设备不断改变着系统需求的性质;

2.1.3 芯片组成与体系结构的改进

在应对平衡处理器与主存以及其他计算机组件的挑战时,仍然需要提高处理器速度。有3种方法可以提高处理器的速度:

1. 提高处理器硬件的速度,原因自傲与缩小了处理器芯片上逻辑门的尺寸。

2.增加处理器与主存之间高速缓存的大小和速度。通过让处理器芯片的一部分专门用于高速缓存来显著降低高速缓存访问时间。

3.改变处理器组成体系结构来提高指令执行的有效速度。涉及使用一种或多种形式的并行。

性能提升的主要因素是时钟速度和逻辑密度的增加。当随着这二者的增加,一些障碍变得更加突出:

功率:随着芯片逻辑密度和时钟速度的增加,功率密度成平方增加;

RC延迟: 延迟会随着RC产品的增加而增加。当芯片上组件的尺寸减少时,其连线会变窄,电阻就会增加。

内存延迟和吞吐量:内存访问的延迟和吞吐量滞后处理器速度;

从20世纪80年代末开始的15年内,2个主要策略被用于提高性能,超越了仅靠增加时钟速度来获得的性能。

其一,增加高速缓存容量。例如处理奔腾芯片上大约10%的区域是高速花奴村,而当代芯片则有超过一半的区域是高速缓存。而且,通常情况下,另一半的3/4用于流水线相关控制和缓冲。

其二,处理器内的指令执行逻辑变得越来越复杂,以便指令能在处理器内并行执行。流水线和超标量是2种值得注意的设计方法。流水线的工作原理和制造工厂中的装配线类似,它能让不同指令的不同执行阶段在流水线中同时发生。超标量方法从本质上看就是允许单个处理器有多条流水线,这样就可以并行执行互不依赖的指令。

到了20世纪90年代中后期,这2种方法都达到了收益递减的拐点。当代处理器的内部组织极其复杂,能够从指令流中挤出大量的并行性。但是这个方向上进一步显著增长似乎将相对平缓。而对处理器芯片上的3级高速缓存来说,每一级的容量都比较大,所以高速缓存的优势似乎也到达了极限。

然而,紧靠增加时钟频率来提高性能就会遇到前面所说的功耗问题。时钟频率越快,消耗的功劳越大,已经达到了一些基本的物理极限。

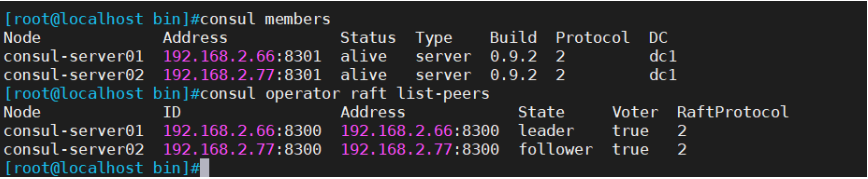

2.2 多核、MIC和GPGPU

考虑到上一节提到的所有困难,设计人员已经转向一种改进性能的全新方法:将多个处理器放在同一个芯片上,并配以大容量的共享高速缓存,即多核处理器。

在处理器内部,性能的提高大致与复杂度增加的平方成正比。但是,如果软件能支持使用多个处理器,那么处理器的数量翻倍几乎就能性能翻倍。

此外,对于两个处理器而言,更大的高速缓存是合理的。这一点很重要,因为芯片上的存储逻辑的功耗比处理逻辑的功耗要小很多。

刚开始的时候,一级高速缓存专门用于单个处理器,二级和三级则由所有处理器共享。现在常见的是,二级高速缓存也是每个内核私有的。

多核和MIC策略涉及单芯片上通用处理器的同构集合,同时,芯片制造商正在寻找另一种设计方案,一个芯片上含有多个通用通用器,再加上图形处理器和专门用于视频及其他任务的内核。

2.4 计算机性能的基本度量

2.4.1 时钟速度

从根本上说,处理器速度由时钟产生的脉冲频率决定,衡量单位是每秒的周期个数,即赫兹Hz。脉冲之间的时间就是周期时间。

时钟频率不是任意的,而是要适合处理器的物理布局。

指令的执行涉及多个离散的步骤,比如从内存取指令,译码指令的各个部分。

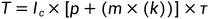

2.4.2 指令执行速度

在任何给定处理器上,诸如加载、存储、分支等不同类型指令需要的时钟周期数不同。令CPI i为i类指令的周期数,

性能因素受五个性能因素受4个系统属性的影响:指令集的设计(称为指令集架构);编译器技术(编译器从高级语言程序生成高校机器语言的效率);处理器的实现,以及告诉缓存和内存层次结构。

另一种常用的性能度量只用于处理浮点指令