时钟硬件电路设计

- 1 简介

- 2 晶振电路中电容的选择

- 3 时钟电路设计要点

- 4 晶振选型

- 5 电路实战

1 简介

晶振时数字电路的心脏,数字电路需要一个稳定的工作时钟信号,时钟电路时硬件电路设计中不可或缺的一个重要内容。晶振一般指晶体振荡器。而在封装内部添加 IC 组成振荡电路的晶体元件称为晶体振荡器。其产品一般用金属外壳、玻璃壳、陶瓷或塑料封装。

晶振工作的原理:

石英晶体振荡器是利用石英晶体的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片,在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了石英晶体谐振器,简称为石英晶体或晶体、晶振。若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应。

晶振的分类:

晶振可以分为有源晶振(crystal)和无源晶振(oscillator)。

内部时钟与外部时钟:

| 时钟 | 描述 |

|---|---|

| 内部时钟 | 单片机的 XTAL1 和 XTAL2 内部有一片内振荡器结构,但仍需要在XTAL1 和 XTAL2 两端连接一个晶振和两个电容才能组成时钟电路,这种使用晶振配合产生信号的方法是内部时钟方式。 |

| 外部时钟 | 单片机还可以工作在外部时钟方式下,外部时钟方式较为简单,可直接向单片机 XTAL1 引脚输入时钟信号方波,而 XTAL2 管脚悬空。 |

外部时钟方式相对内部时钟较为方便,大多数单片机系统还是选择内部时钟方式。这是因为单片机的内部振荡器能与晶振、电容构成一个性能非常好的时钟信号源,而如果要产生这样的信号作为外部时钟信号输入到单片机中,则需要添加的器件远不止一个晶振和两个电容这么简单。

2 晶振电路中电容的选择

-

因为每一种晶振都有各自的特性,所以按制造厂商所提供的数值选择外部元器件。

-

在许可范围内,C1,C2 值越低越好。C 值偏大虽有利于振荡器的稳定,但将会增加起振时间。

不同厂家生产的石英晶体谐振器和陶瓷谐振器的特性和品质都存在较大差异,在选用,要了解该型号振荡器的关键指标,如等效电阻,厂家建议负载电容,频率偏差等。在实际电路中,也可以通过示波器观察振荡波形来判断振荡器是否工作在状态。

3 时钟电路设计要点

顶层设计模块时钟选择:

时钟大小一把都说时时钟频率或者时钟周期,

1、接口类

- 有些标准接口,协议就订好了时钟频率,比如Ethernet、USB、UART等;

- 有些接口,时钟频率没有限定,就由需求来确定时钟频率,比如SPI、IIC等。

2、系统内部

比如CPU、总线、Memory等,关乎系统性能,希望吸能高,时钟频率就要高。做到尽量低,尽量少。

- 尽量低是指做工作频率可以尽可能设定得比较低,比满足需要的时钟频率略高或者相等。这样可以提高系统的稳定性降低功耗,时许也会更加宽松。

- 尽量少是指时钟域的数量尽量少。不同模块尽量使用相同的时钟频率,这样可以有效减少跨时钟域的情况发生。Xilinx 的 FPGA 的时钟信号会使用特定的时钟资源,使用过多的时钟频率会导致布线困难。

3、时钟设计

一般是由FPGA板上提供源时钟,使用FPGA内部的MMCM(Mixed-Model Clock Manager—混合模式时钟管理器,实现了最低的抖动和抖动滤波,为高性能的 FPGA 设计提供更高性能的时钟管理功能)。等倍频得到系统所需要的时钟,比较简单的设计中,源时钟直接驱动逻辑电路也是可以的。为方便约束,时钟逻辑最好都在一个module中,包括MMCM、BUFG、BUFGMUX、clock Gating、除频等。时钟约束不用设计,需要设计的时系统的时钟结构,时钟约束时使用综合工具所支持的语法将时钟结构描述出来,以便工具进行综合。

FPGA设计要点:时钟树

对于FPGA来说,要尽可能避免异步设计,尽可能采用同步设计。同步设计的第一关键就是时钟树。具体的设计细则如下:

-

尽可能使用单一时钟。

-

如果有多个时钟域,一定要仔细划分。

-

跨时钟域的信号一定要做同步处理。

对于控制信号,可以采用双采样;

对于数据信号,可以采用异步FIFO。

注意:异步FIFO不是万能的,一个异步FIFO也只能解决一定范围内的频差问题。

-

尽可能将FPGA内部的PLL、DLL利用起来。

-

对于特殊的IO接口,需要仔细计算

-

Tsu(setup time)、Tco(clock output delay)、Th(hold time),并利用 PLL、DLL、DDIO、管脚可设置的 delay

等多种工具来实现。简单对管脚进行 Tsu、Tco、Th 的约束往往是不行的。

4 晶振选型

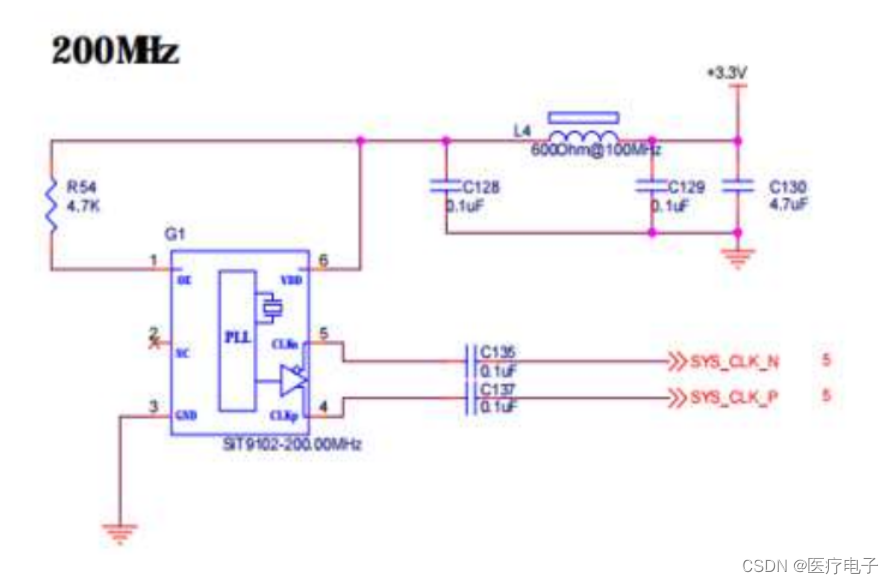

- 频率选择:频率越高、价格越高。频率越高,频差越大。综合考虑,一般工程师会选用频率低但稳定的晶振,自己做倍频电路。(总之,频率时根据需求选择,并不是频率越大越好。)

- 频率稳定度:ppm。

- 电源电压:常用的有1.8V、2.5V、3.3V、5V等。

- 4输出:根据需要采用不同输出。(HCMOS,TTL,PECL,LVDS,LVHCMOS 等)每种输出类型都有它的独特波形特性和用途。对称性、上升和下降时间以及逻辑电平对某些应用来说也有具体要求。

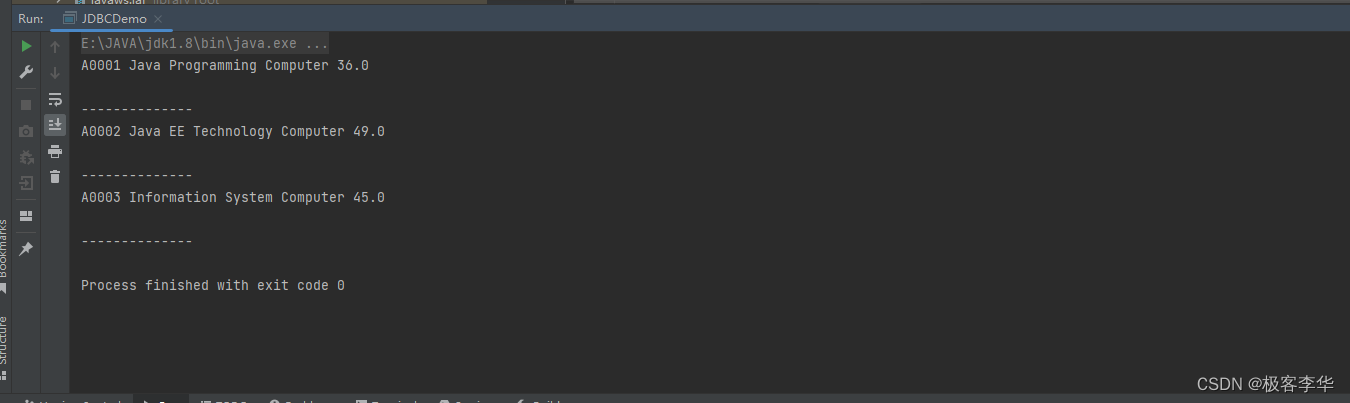

5 电路实战

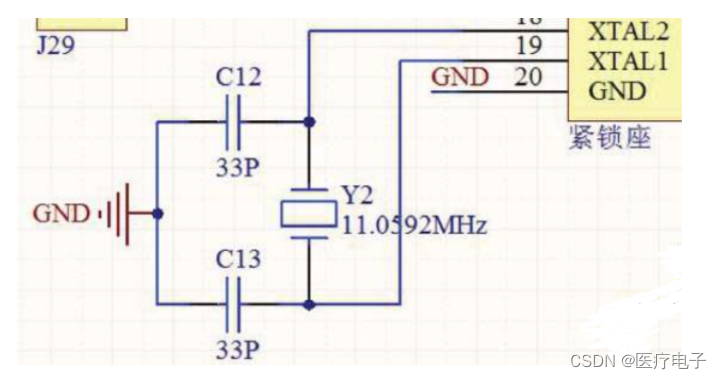

若直接将晶振接入单片机晶振引脚,会发现系统工作不稳定,这是因为晶振起振的一瞬间会产生一些电感,为了消除这个电感所带来的干扰,可以在此晶振两端分别加上一个电容,电容的选取需要无极性的,另一端需要共地。根据选取的晶振大小决定电容值,通常电容可在 10-33PF 值范围内选取。

有源晶振设计

下一篇…

![[附源码]计算机毕业设计JAVA龙虎时代健身房管理系统](https://img-blog.csdnimg.cn/d9bf27ede9ee4c9d99abf10cf414b028.png)