-

文章目录

- 7. 用户自定义元件模型

- 7.1 UDP应用实例

- 8. 基本门级元件和模块的延时建模

- 8.1 门级延迟建模

- 8.1.1 门级延迟的基本延迟表达形式

- 8.1.2 门级延迟的最小、典型、最大延迟表达形式

- 8.1.3 例子用VerilogHDL建立图5.8-1 模块D的延迟仿真模块

- 8.2 模块延迟建模

- 8.2.1 延迟说明块 Specify Block

- 8.2.2 路径延迟描述方式

- 8.3 与时序检查相关的系统任务

7. 用户自定义元件模型

-

!!!!现在UDP用的很少,几乎不用了,但是它是作为Verilog HDL 的一个点,还是依然存在,主要是了解一下

-

Verilog HDL 语言提供了一种扩展基元的方法,允许用户自己定义元件(User DefinedPrimitives,UDP)。通过 UDP,可以把一块组合逻辑电路或时序逻辑电路封装在一个 UDP内,并把这个 UDP 作为一个基本门元件来使用。需要注意的是,UDP 不能综合,只能用于仿真。

-

UDP实际上就是查表的方式

-

函数和任务是一定要放在模块内部的,而UDP不是放在里面,它和模块是等同的一个概念

-

我们在做设计的时候经常会采用真值表的方式,对于模块来说我们用的是模块名,然后是case语句,这一点和UDP也不同

-

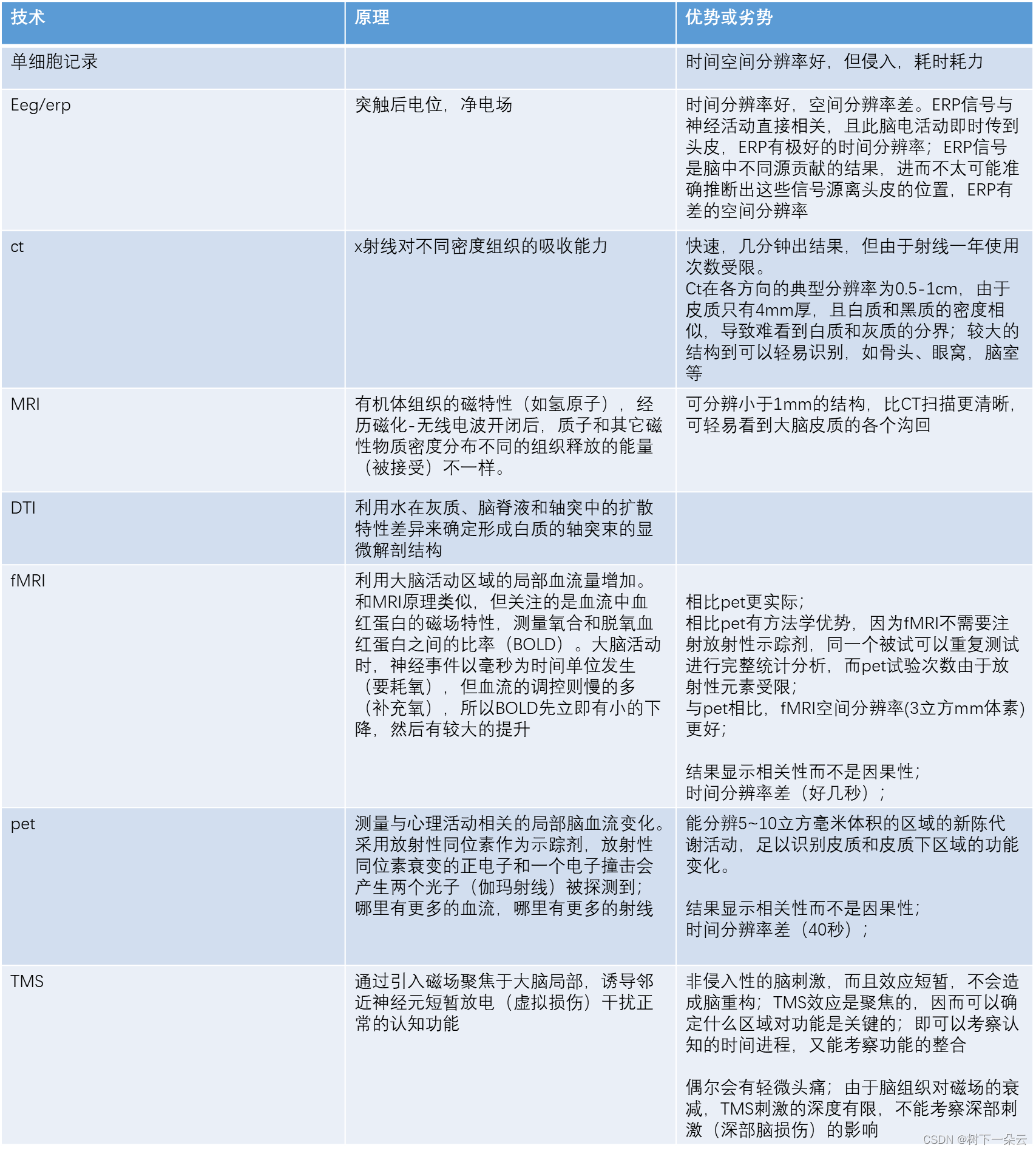

UDP的特点

(1)UDP的输出端口只能有一个,且必须位于端口列表的第一项。只有输出端口能定义为reg类型。

(2)UDP的输入端口可有多个,一般时序电路UDP的输入端口最多9个,合电路UDP的输入端口可多至10个。

(3)所有端口变量的位宽必须是1比特。

(4)在 table 表项中,只能出现0、1、x这三种状态,z将被认为是x状态。 -

调用

-

因为可综合逻辑设计可以完全替代primitive,所以用的很少了

7.1 UDP应用实例

- 组合电路UDP应用实例

- 组合电路UDP应用实例

- 时序电路UDP元件

- 混合电路UDP元件

- !!非常混乱,而且也只是仿真,用的人很少

8. 基本门级元件和模块的延时建模

- 这是一个非常重要的概念,集成电路一定是会有延迟的

8.1 门级延迟建模

- 门级延迟分为四类

(1)上升延迟:表示信号由0、x或z状态变化到1状态时受到的门传输延迟

(2)下降延迟:表示信号由 1、x或z状态变化到0状态时受到的门传输延迟

(3)到不定态的延迟:表示信号由01或z态变化到x状态时受到的门传输延迟(只在仿真有意义)

(4)截止延迟:表示信号由 0、1或x状态变化到z状态时受到的门传输延迟

8.1.1 门级延迟的基本延迟表达形式

- 在门级延迟的基本表达形式下,delay 内可以包含0~3个延迟值,表 5.8-1 给出了指定的不同延迟值个数时 delay 的4种表示形式

- 当delay 没有指定门延迟值时,默认的延迟值为 0。这意味着元件实例的“上升延迟值”、“下降延迟值”、“截止延迟值”和“到不定态的延迟值”均为0。

例中,门级延迟值为0,因为没有定义延迟,所以元件实例 U0的“上升延迟值”、“下降延迟值”、“截止延迟值”和“到不定态的延迟值”均为0。 - 当 delay 内只包含1个延迟值时,给定的延迟值d将同时代表着元件实例的“上升延迟值”、“下降延迟值”、“截止延迟值”和“到不定态的延迟值”。

例中,门级延迟值为 20,且只包含 1 个延迟值,说明元件实例 1 所有类型的门级延迟都是 20个单位时间。 - 当delay 内包含了2个延迟值时,元件实例的“上升延迟值”由给定的d1指定,“下降延迟值”由给定的d2 指定,而“截止延迟值”和“到不定态的延迟值”将由d1和d2中的最小值指定。

例中,门级延迟值为(10,20),包含了2个延迟值 10和20,这表明元件实例U2 将具有10个单位时间的“上升延迟”和 20 个单位时间的“下降延迟”,而它的“截止延迟”和“到不定态的延迟”将由 10和20 中的最小值指定,即10个单位时间。 - 当 delay 内包含了3 个延迟值时,元件实例的“上升延迟值”由给定的 dA 指定“下降延迟值”由给定的dB 指定,“截止延迟值”由给定的dC 指定,而它的“到不定态的延迟值”将由 dA、dB 和 dC 中的最小值指定。

例中,门级延迟值为(10.2030),包含了3个延迟值 10、20和30,这表明元实例U3具有10个单位时间的“上升延迟”、20个单位时间的“下降延迟”和30个单位时间的“截止延迟”,而它的“到不定态的延迟”将由 10、20 和 30 中的最小值指定,即 10个单位时间

- !!这个概念可以对一个元器件的延迟进行一个非常完整清楚的描述

8.1.2 门级延迟的最小、典型、最大延迟表达形式

- !!所有的东西不可能完全一样,虽然集成电路在纳米级的差异已经非常小了,但是我们要承认所有生产出来的东西都有差异

- !!在所有的参考手册都有一个值,对所有的信号参量它不会告诉你一个准确的值,因为世界上就没有一个准确的值,对于电子产品他会怎么样表示一个参数呢?他会采用最小、典型、最大,语法格式如下:

- 采用“最小、典型、最大”延迟表达形式时,delay 内可以包含 1~3 个延迟值

- 例1:

其中,delay 中只包含 1 个延迟值,其最小值为 4、典型值为 5、最大值为 6。元件实例 U1的“上升延迟值”、“下降延迟值”、“截止延迟值”和“到不定态的延迟值”如表 5.8-2所示。

- 例2:

其中,delay 中包含了2个延迟值,第一个延迟值的最小值为 3、典型值为 4、最大值为5,第二个延迟值的最小值为 5、典型值为 6、最大值为 7。元件实例 U2 的“上升延迟值”由第一个延迟值指定,“下降延迟值”由第二个延迟值指定,“到不定态的延迟值”和“截止延迟值”均由两个延迟值中的最小值指定。各值的取值情况如表 5.8-3 所示

- 例3:

其中,delay 中包含了3 个延迟值,第一个延迟值的最小值为 2、典型值为 3、最大值为4,第二个延迟值的最小值为 3、典型值为 4、最大值为 5,第三个延迟值的最小值为 4、典型值为5最大值为6元件实例 U3 的“上升延迟值”由第一个延迟值指定,“下降延迟值由第二个延迟值指定,“截止延迟值”由第三个延迟值指定,而它的“到不定态的延迟值”由二个延迟值中的最小值指定。各值的取值情况如表 5.8-4 所示

8.1.3 例子用VerilogHDL建立图5.8-1 模块D的延迟仿真模块

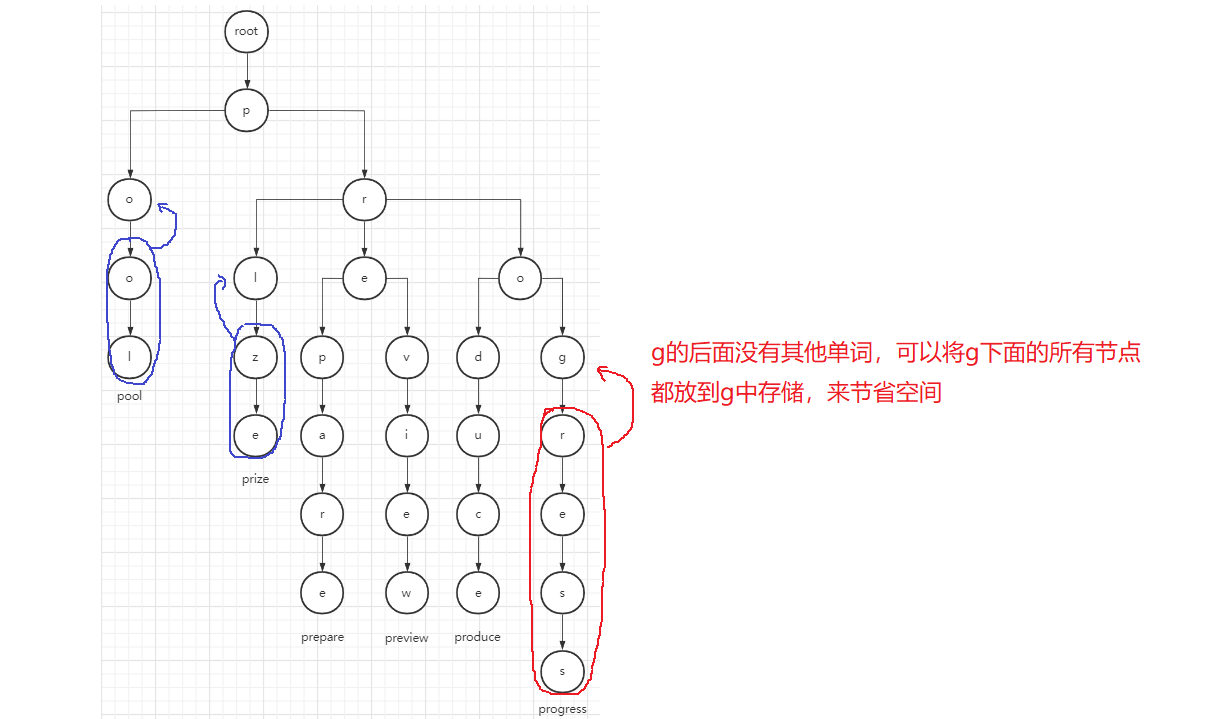

- 图 5.8-1 逻辑电路的功能是 out =(a*b)+ c。

- 其门级实现如图所示,其中包含了一个延迟时间为 5 个单位时间的与门和一个延迟时间为 4个单位时间的或门

- 信号输出

8.2 模块延迟建模

- 对于由用户自己定义设计的模块,可以采用“加入门级延迟说明”的办法,通过“延迟说明块(Specify Block)”的结构来对模块的传输延迟进行说明。注意,延迟说明块既可以出现在行为描述模块内,也可以出现在结构描述模块内。

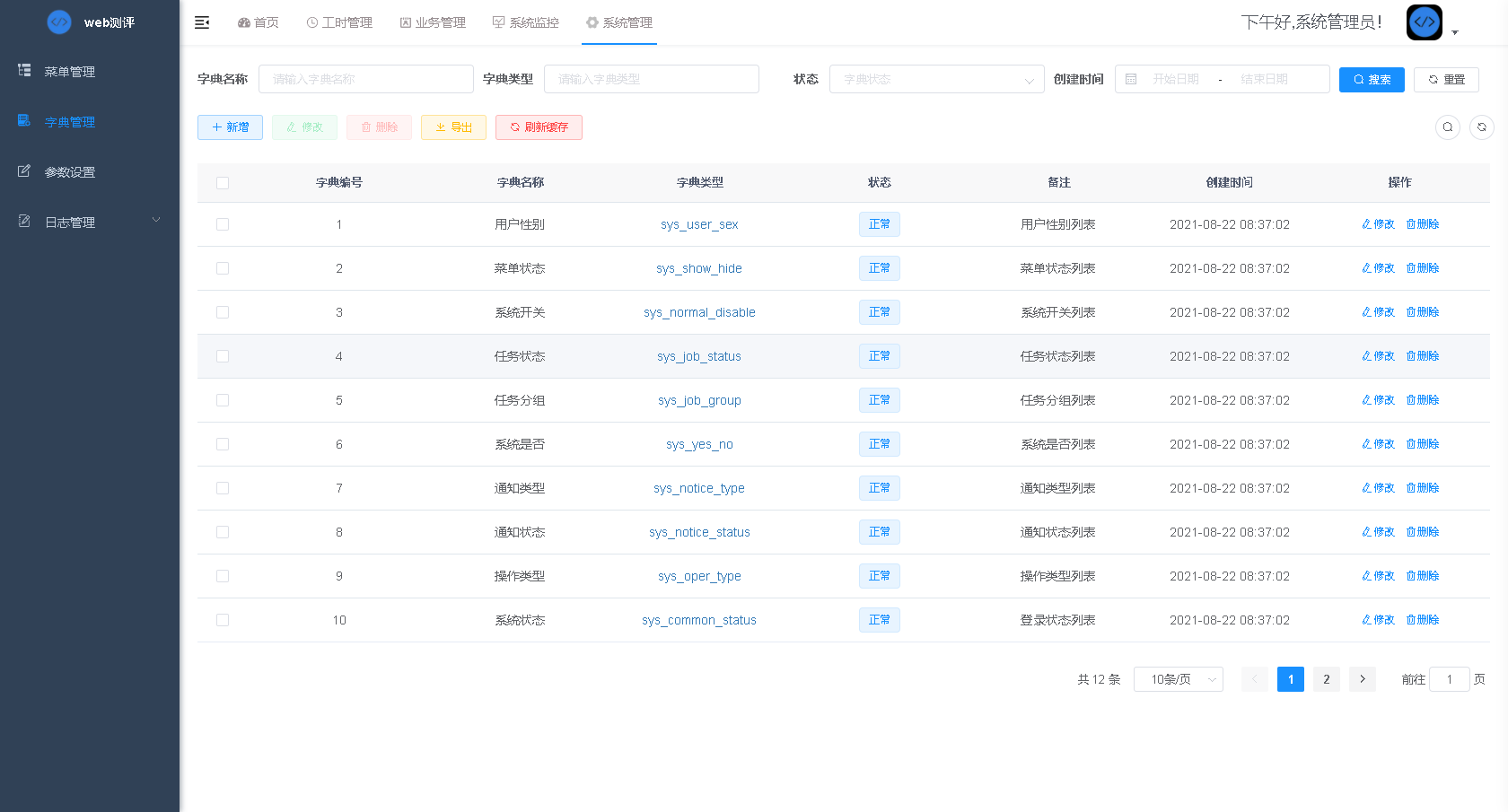

8.2.1 延迟说明块 Specify Block

- 在模块输入和输出引脚之间的延迟称为模块路径延迟

- specify块包含下列操作语句:

(1)定义穿过模块的所有路径延迟(主要作用)

(2)在电路中设置时序检查(主要作用)

(3)定义specparam 常量(特殊性) - 举例:以图5.8-3为例,用specify 块来描述图中M模块的路径延迟

- 可以看到specify语句是嵌套在模块内部的

- 问题:有什么作用呢?

- !!器件的延迟是固有的,但是在仿真过程中(功能仿真,网表仿真,时序仿真),对于结构的电路的仿真,我们是从整个的过程中有一个定义的,如果加不上这样的延迟,所有的电路级的仿真都会在模能两可的状态下进行。如果加上这样一个延迟就表征了我们怎样在电路设计的初始阶段就能够保证时序的这样的要求,这实际上是一个非常高档的方式。这个做好很困难,但是集成电路有一个出发点,任何流片之前的仿真和测试,大家都喜欢投入更多的精力去做,因为问题发现在萌芽阶段成本就会低

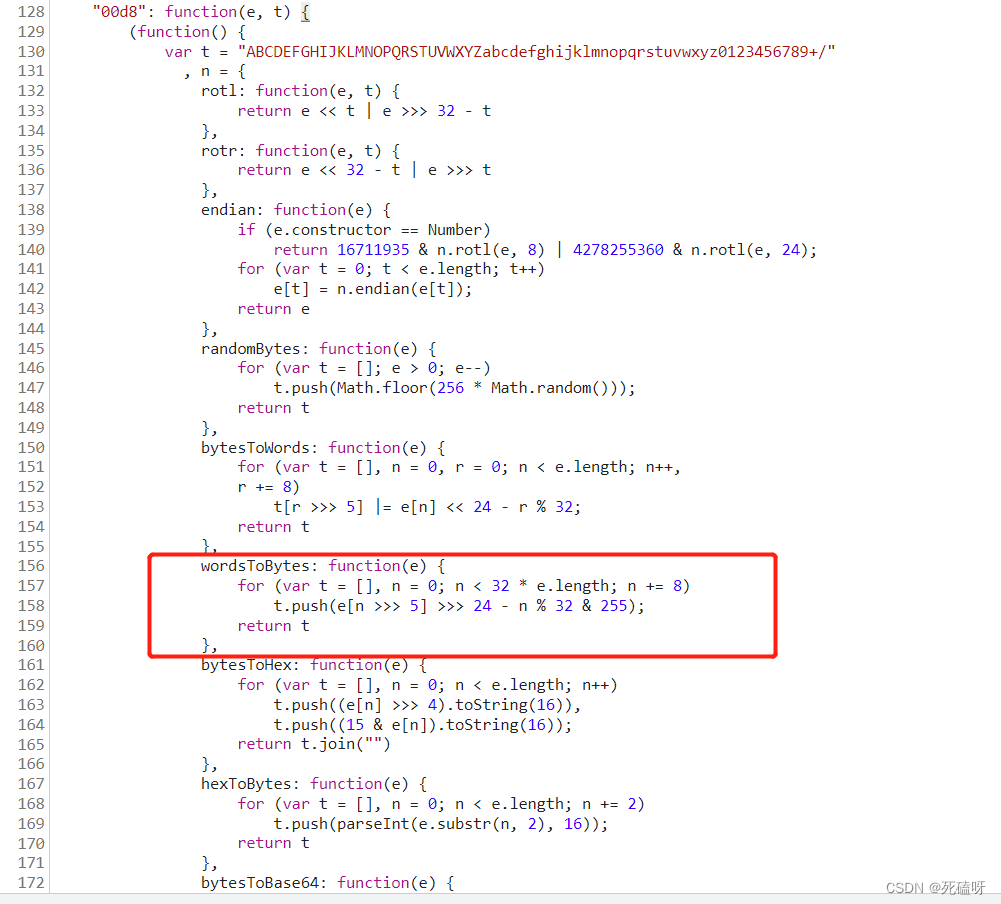

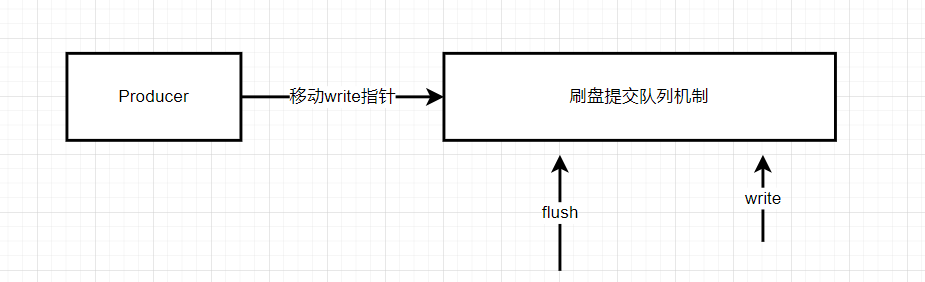

8.2.2 路径延迟描述方式

-

并行连接

在specify 块中,用符号“=>”说明并行连接,其语法格式如下

其中,<delay_value>可以包含 1-3 个延迟量,也可以采用“最小、典型、最大”延迟表达形式,和刚刚讲的方式完全一样。在延迟量由多个值组成的情况下,应在延迟量的外面加上一对括号

表示的是输入 a 到输出b的最小、典型和最大延分别是 8910个时间单位

在并行连接中,源域中的每一位与目标域中相应的位连接。如果源域和目标域是向量必须有相同的位数,否则会出现不匹配。因此,并行连接说g明了源域的每一位到目标域的每一位之间的延迟。

-

全连接

source_field是源域,destination_field是目标域,*>表示全连接

-

该例描述了四条全连接的路径延迟,其中定义了端口a和端口b到端口 out 的路径延迟为9个时间单位,端口c和端口d到端口out的路径延迟为 11个时间单位

-

!!需要注意如果是并行连接,前后两个的bit位数应该相同。如果采用全连接,表示的是一组线,这时任何信号位宽不一样都可以

- spacparam 声明语句

specparam 用来定义specify 块中的参数,参数是可以用来简化程序修改的过程(希望只改变参数)

- 和parameter的区别(实际上是完全不同)

(1)specparam语句只能在延迟说明块(specify 块)中出现,而 parameter 语句则不能在延迟说明块内出现。

(2)由specparam 语进行定义的参数只能是延迟参数,而由 parameter 语句定义的参数可以是任何数据类型的常数参数。

(3)由specparam 语定义的延迟参数只能在延迟说明块内使用,而parameter 语句定义的参数则可以在模块内的任意位置处使用。

8.3 与时序检查相关的系统任务

- Verilog HDL提供了系统任务来进行时序检查,该类任务很多,表 5.8-5 列举了部分与时序检查相关的系统任务。

- !!对于测试方法,有一种自动测试,当出问题的时候,我才会对这个参数进行说明。对于时序来说,最好的方式就是出了问题提示,不出问题就不提示,这是在仿真中追求的最好的一种测试方式,叫做自动测试。但是怎么进行自动测试,硬件描述语言给出了一些系统任务,这些不能说覆盖了所有自动测试,但是对于时序出现问题的地方一定会给提示说明

- 如果要写这个,一定要在模块中的specify语句中定义

-

setup

建立时间检查可以使用系统任务$setup。

举例:

该程序的功能是建立时间检查,clock 为参考信号,data 是被检查的信号,如果time_posedge_clock - time data<3,则报告违反约束 -

hold

保持时间检查可以使用系统任务Shold

举例:

- !!关于建立时间和保持时间可以看我的数电博客https://blog.csdn.net/y_u_yu_yu_/article/details/127641915

- !!!!对于高速电路,在时序上可能出问题的是建立时间还是保持时间?建立时间,建立时间速度快,时间压缩的非常短,所以当时间有要求的时候,建立时间是很困难的。所以以后在设计高速电路时,要面对的绝大多数问题都是建立时间不够。什么时候是保持时间不够的,是在信号变化非常长的时候,信号有可能在时钟没到来时掉下来,比如用的22nm的工艺,明明可以做到几个G的频率,但是非要做一个50M的信号,这时候信号变化要比时钟变化要快,所以这时候一定是保持时间,所以在超低功耗等器件的时候要注意考虑保持时间