【学习笔记】Cadence电子设计全流程(三)Capture CIS 原理图绘制(下)

- 3.16 原理图中元件的编辑与更新

- 3.17 原理图元件跳转与查找

- 3.18 原理图常见错误设置于编译检查

- 3.19 低版本原理图文件输出

- 3.20 原理图文件的锁定与解锁

- 3.21 Orcad 与 Allegro 软件交互式布局设置

- 3.22 Allegro Product Choices

- 3.23 两份原理图文件对比设置

- 3.24 物料 BOM 表的设置与导出

- 3.25 原理图的 PDF 打印输出

- 3.26 层次原理图的概念与设计

全部内容见专栏:【Cadence从原理图到PCB设计】

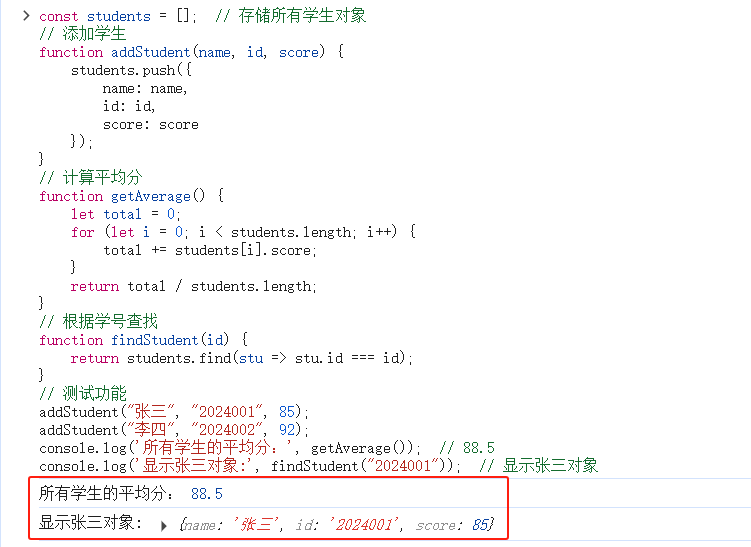

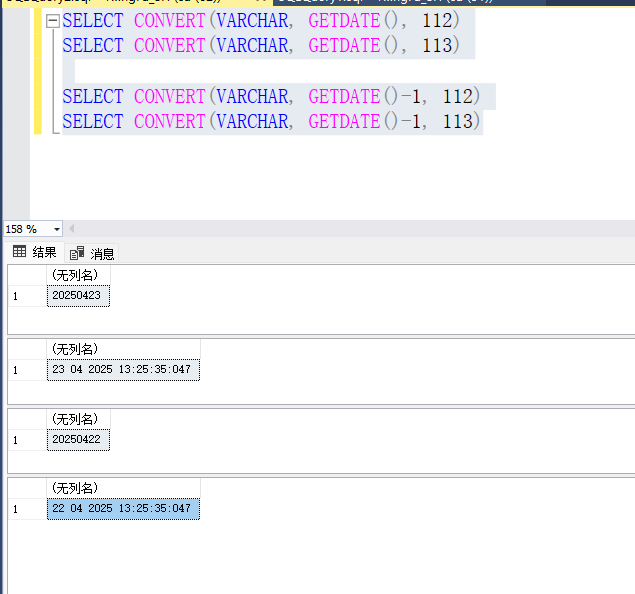

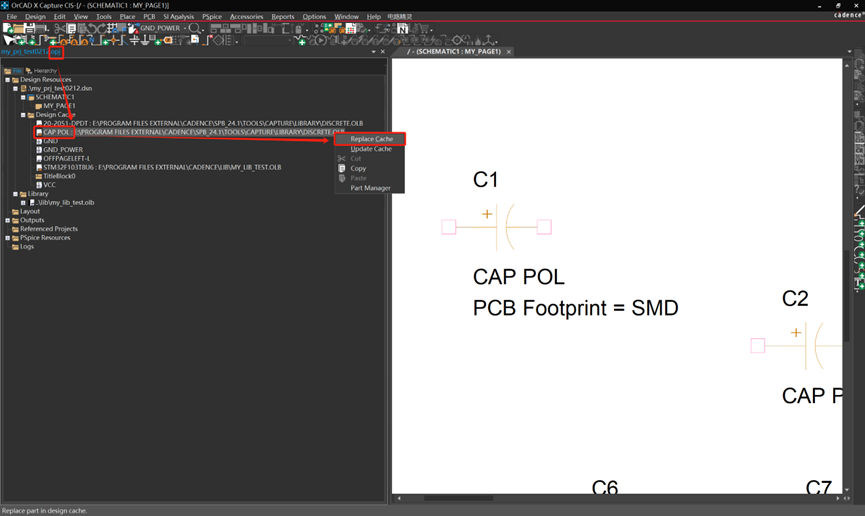

3.16 原理图中元件的编辑与更新

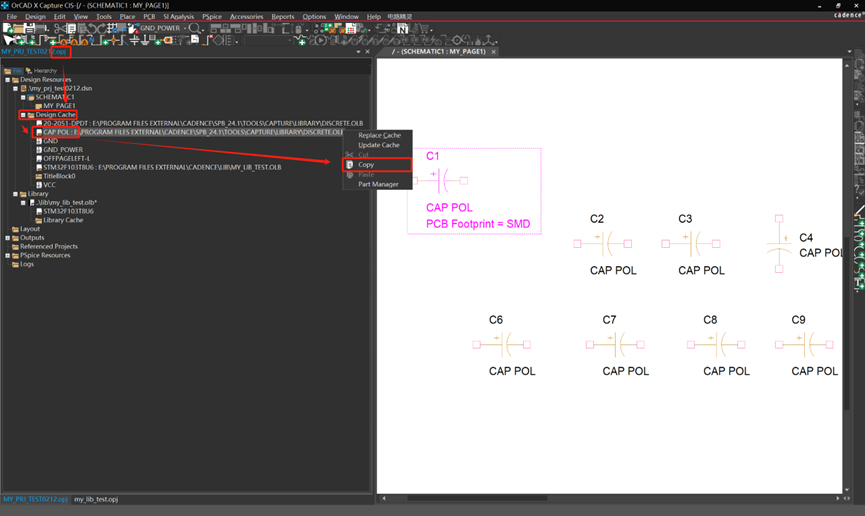

方式1 在原理图中直接更新

缺点:元器件和库中内容是不一样的,下一次调用库时仍需要修改,修改只是应用于当下原理图。

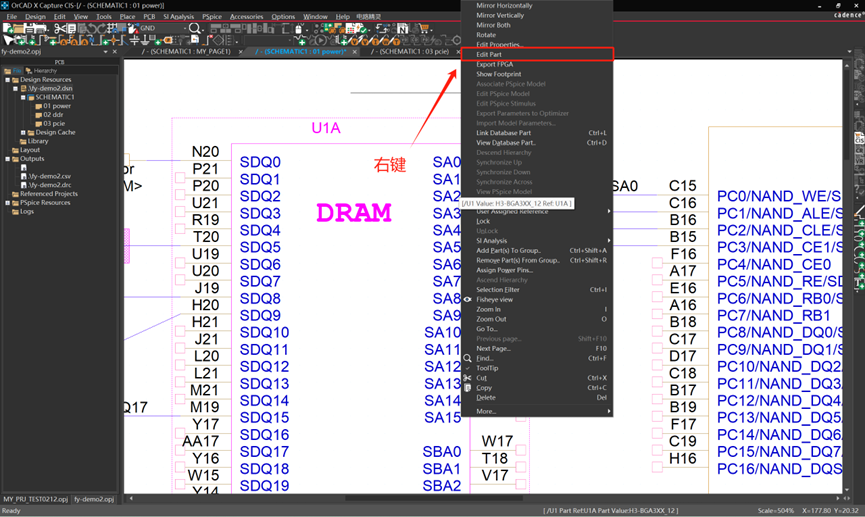

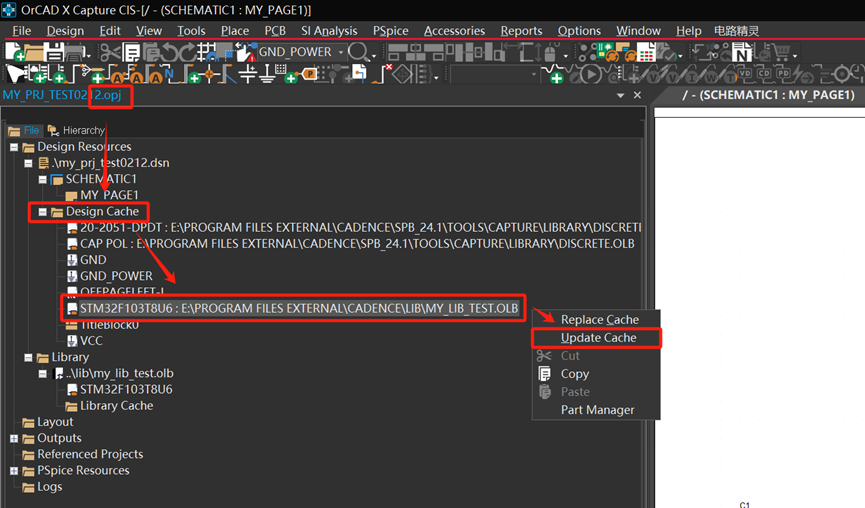

方式2 在库中更新

找到本地库直接打开修改后,进行更新

可以直接从缓存文件中复制/粘贴,找到想要提取的元器件,copy,于库中粘贴

替换的时候,需要先替换掉库的路径

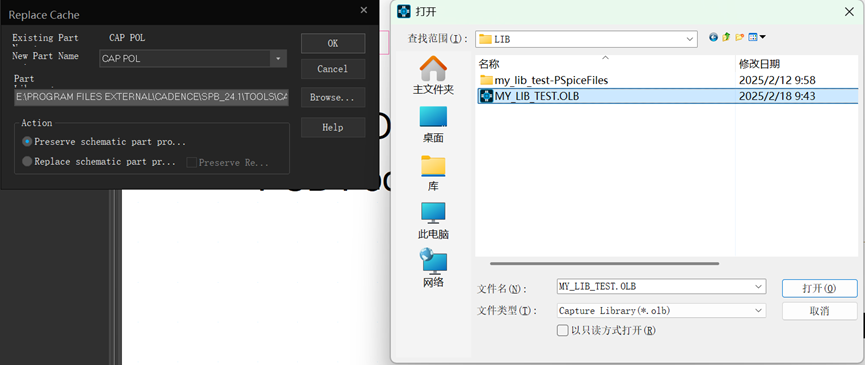

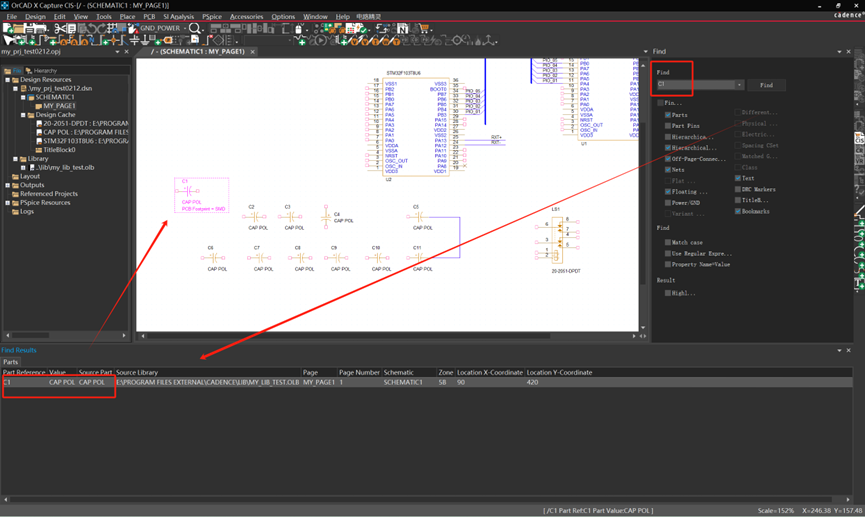

3.17 原理图元件跳转与查找

选择原理图跟目录,进行全局查询;或者选中某一页原理图,在当前页面进行搜索,这一步操作很重要,不然没法进行搜索

执行菜单【Edit】→【Find】命令,或者按快捷键【Ctrl+F】进行查找,弹出原理图的搜索框进行搜索跳转

在搜索框中输入所要搜索的位号字符等,点击Fimd按钮在左下角的窗口中双击找到的结果即可高亮并定位到器件位置

搜索完成以后,软件会自动弹出该元素所在的界面,若该元素有很多个,则下面会有一个列表,点击即可跳转,如图所示,若没有该元素,则不会有界面弹出

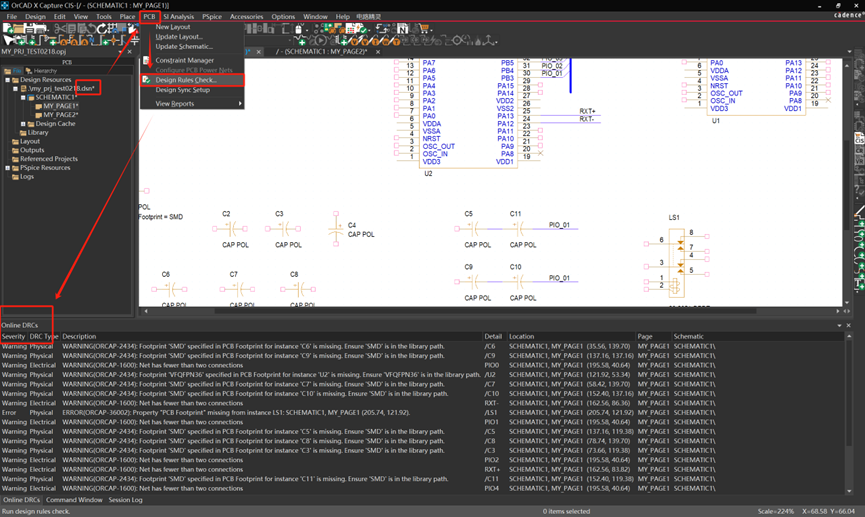

3.18 原理图常见错误设置于编译检查

在输出网表与PCB设计之前,进行DRC检测

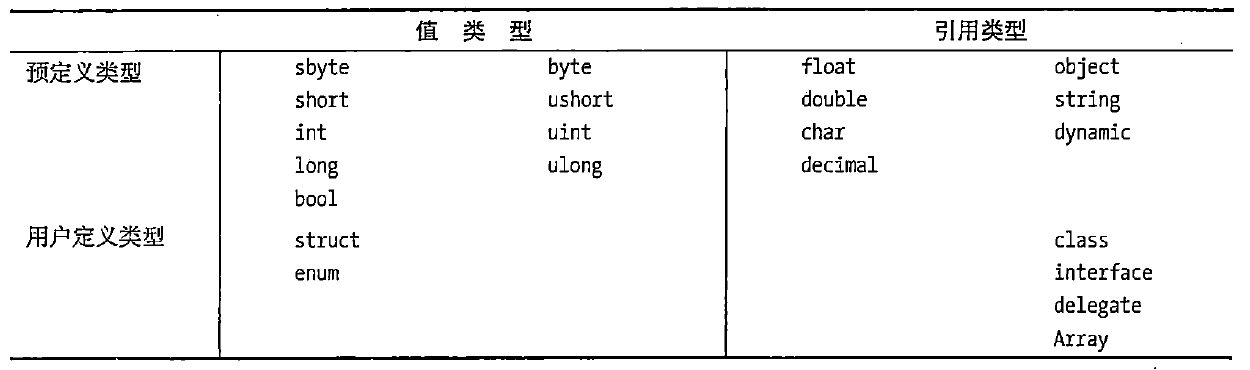

| Check 事项 | 含义 |

|---|---|

| Check single node nets | 检查设计中的单端网络 |

| Check no driving source and pin type… | 检查器件属性无源管脚与有源管脚的连接是否正确 |

| Check duplicate net name | 检查重复的网络名称 |

| Check off-page connector connect | 检测分页图纸间接口的连接性 |

| Check hierarchical port connection | 检测阶层端口的连接性 |

| Check unconnected bus net | 检测没有连接的总线网络 |

| Check unconnected pins | 检查没有连接的管脚 |

| Check power pin visible | 检测电源属性的管脚是否显示了管脚名称与编号 |

| Check missing/illegal PCB Footprint | 检测封装名称是否填写。是否含有非法字符 |

| Check Normal convert view system | 检测一个部件的正常视图上的pin号是否与转换视图上的pin号不同 |

| Check incorrect pin group assignment | 检查同一个Pin Group的所有插脚是否有相同的类型 |

| Check high speed props syntax | 在设计中检查网络高速属性的语法是否正确 |

| Check missing pin number | 检测缺失管脚编号的管脚 |

| Check device with zero pins | 检测设计中是否含有零宽度的管脚 |

| Check power ground short | 检测一个Part内部的电源网络名称是否有两个不同的网络标号名称 |

| Check Name Prop consistency | 检测层次原理结构中是否含有相同的网络名称 |

| Report all net name | 报告所有网络的名称 |

| Report off-grid object: | 报告不在格点上是器件 |

| Report hierarchical ports and off-page connection | 报告阶层端口和分页图纸间接口的连接 |

| Report Misleading Tap Connection | 报告易误解的连接 |

| Report Visible unconnected power pins | 报告所有具有可见电源属性的管脚是否有连接 |

| Report unused part packages | 报告原理图中未使用的器件part |

| Report invalid Refdes | 报告原理图中无效的器件位号 |

| Report identical part references | 报告原理图相同的位号 |

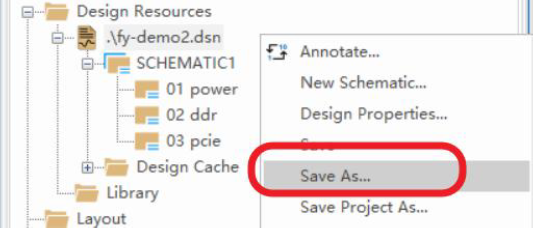

3.19 低版本原理图文件输出

需要选中降低原理图的根目录就是DSN文件,如图所示选中之后,点击鼠标右键,SaveAs,就可以存为低的版本

在弹出的界面中,在保存类型那一栏可以选择低的版本,般是存为16.2的版本,这样就存为了低的版本了

这里可以看到有这样的一个情况,就是Orcad存为低的版本的时候,只能存为一个版本,那就是16.2的版本。其实在Orcad设计的时候,16.2之前的版本,机制都是通用的,都可以打开,16.2以后版本的机制是一样的,所以存为低版本的时候,是以16.2为分界点来处理就可以了

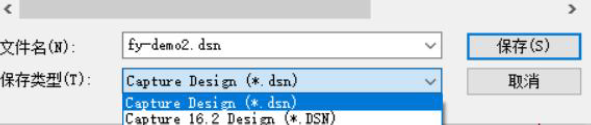

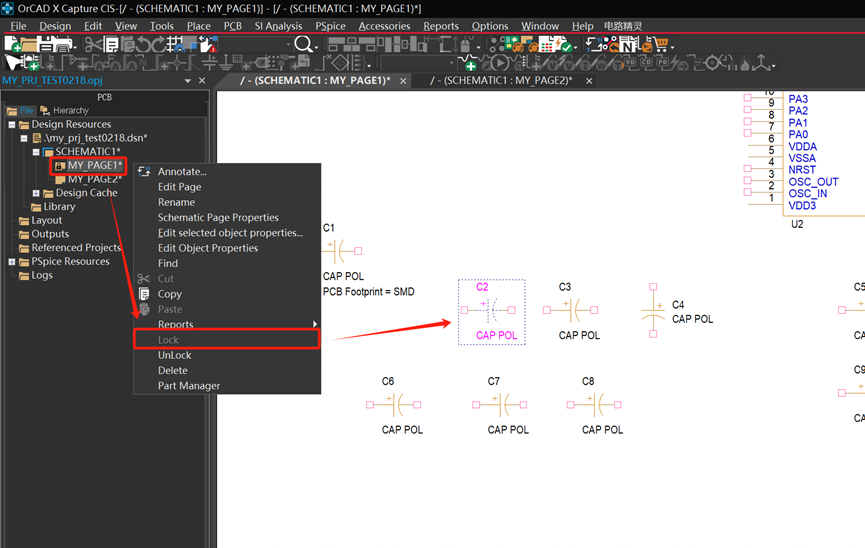

3.20 原理图文件的锁定与解锁

选中图纸点击右键LOCK即可锁定。工程可设置密码。

防止PCB工程师误操作。

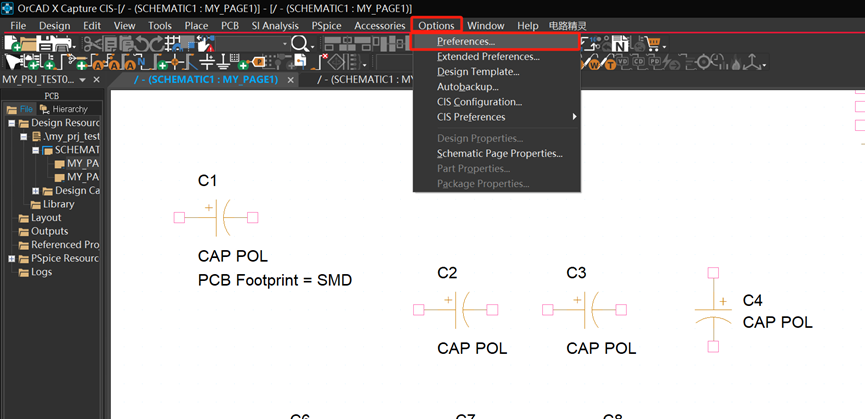

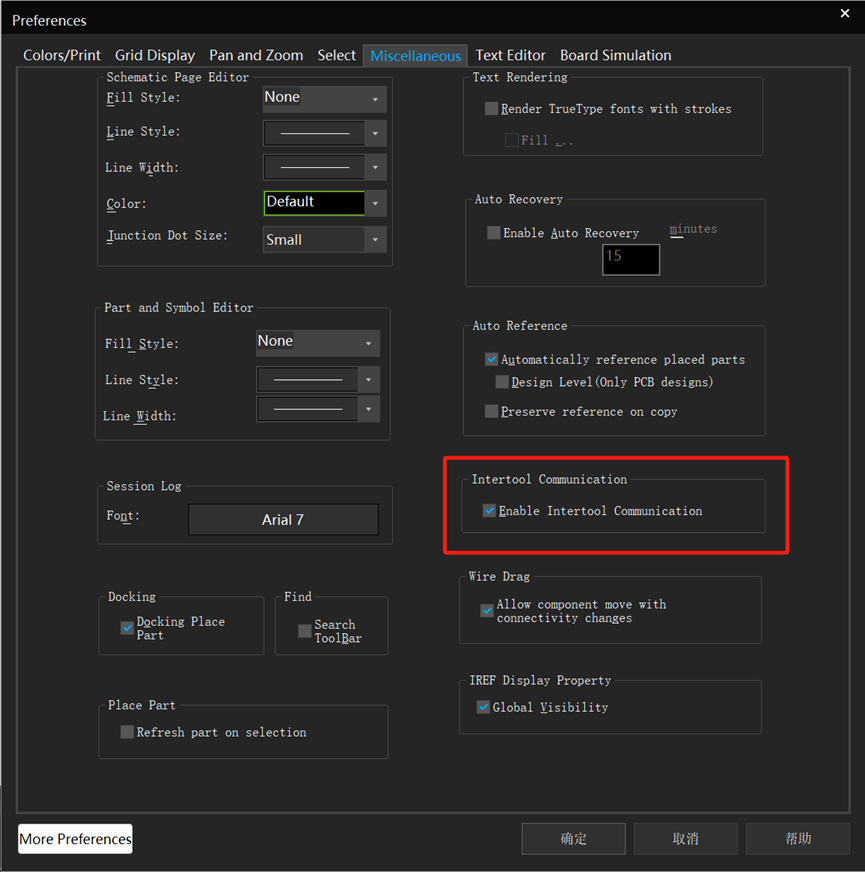

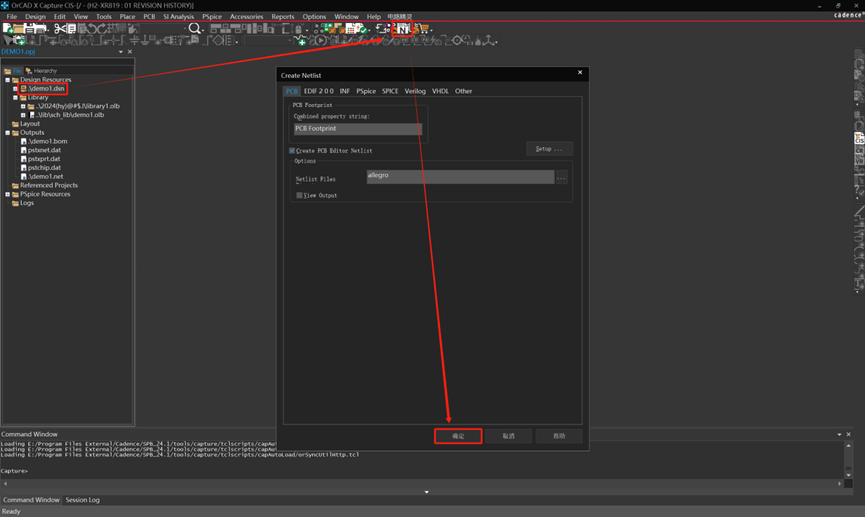

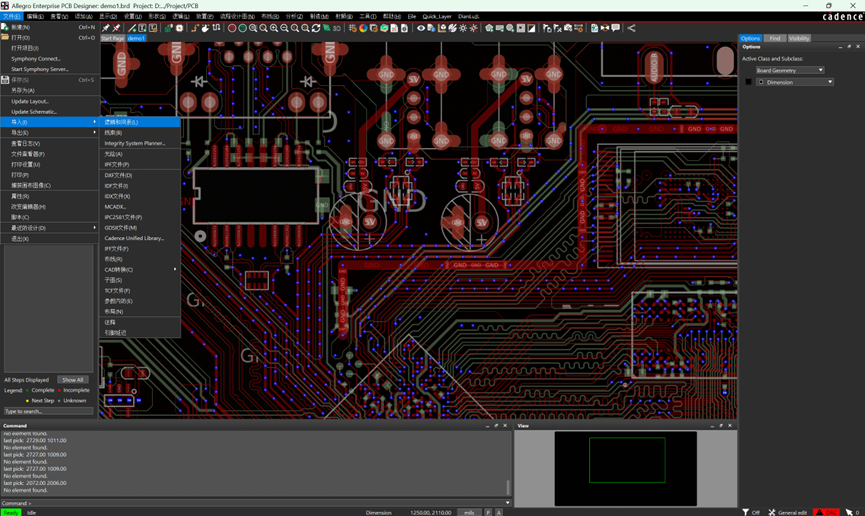

3.21 Orcad 与 Allegro 软件交互式布局设置

在做pcb设计的时候,原理图选中一个元器件,PCB中可以直接选中。

- 为了达到原理图和PCB两两交互,需要在ORCAD中将允许交互进行勾选,执行菜单命令Options-Preference,打开参数界面,选择Miscellaneous菜单,将交互模式进行勾选;

- 使能交互式布局

- 网表必须是导入第一方网表,第三方无效;

- 在allegro中使能/关闭交互式布局功能

- 当前两个步骤完成后,原理图与PCB的交互就已经完成,在原理图选中器件在PCB中进行交互的时候,需要先在PCB中执行MOVE命令,PCB中相应器件才会被选中;

- 在PCB选中器件在原理图中进行交互的时候,需要先在PCB中执行高亮命令,原理图中相应器件才会被选中

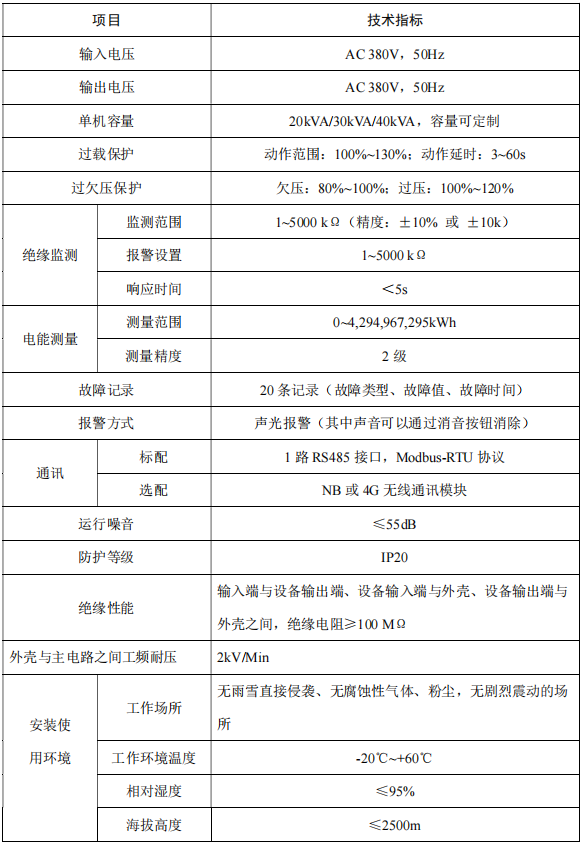

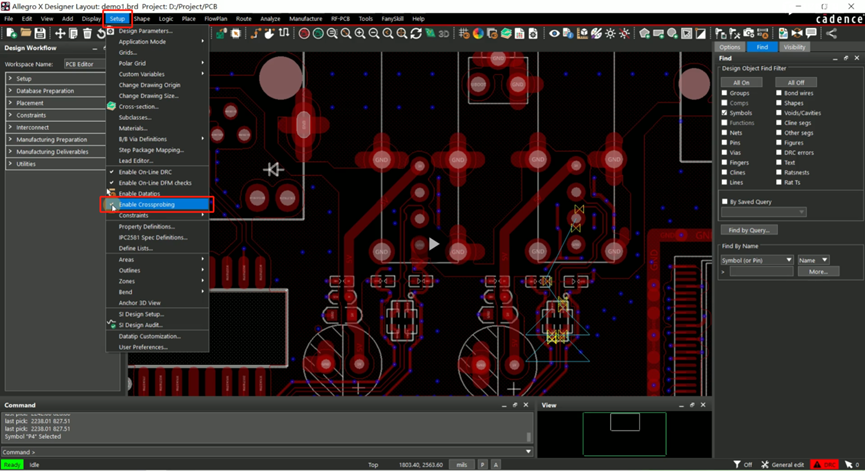

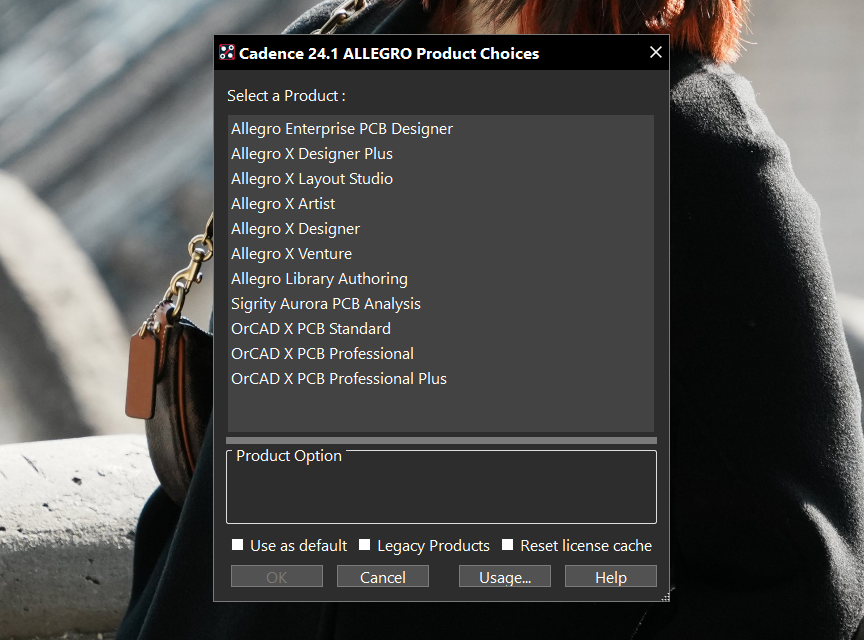

3.22 Allegro Product Choices

在 Cadence Allegro 中打开 PCB 文件时,如果出现“Allegro Product Choices”对话框,并且列出了多个选项(如你提到的这些),选择哪个取决于你的具体需求和许可证权限。

以下是这些选项的详细说明,帮助你做出选择:

| Allegro Product Choices | 功能/适用场景 |

|---|---|

| Allegro Enterprise PCB Designer | 这是 Allegro 的最高版本,包含所有高级功能,如高速设计、约束管理、信号完整性分析、电源完整性分析等。适合复杂的高速 PCB 设计,尤其是需要高级仿真和分析的项目。 |

| Allegro X Designer Plus | 提供完整的设计功能,包括布局、布线、约束管理等,但可能缺少一些企业版的高级功能。适合中高复杂度的 PCB 设计。 |

| Allegro X Layout Studio | 专注于 PCB 布局和布线,适合中小型项目。适合不需要高级仿真和分析的常规 PCB 设计。如果你的设计复杂度较低,可以选择这个。 |

| Allegro X Artist | 提供基本的 PCB 设计功能,适合初学者或小型项目。适合简单的 PCB 设计任务。如果你的设计需求较简单,可以选择这个。 |

| Allegro X Designer | 提供标准的设计功能,包括布局、布线和约束管理。适合中等复杂度的 PCB 设计。如果你需要标准的设计功能,可以选择这个。 |

| Allegro X Venture | 这是一个入门级工具,功能较为基础。适合非常简单的 PCB 设计或学习用途。如果你的设计需求非常基础,可以选择这个。 |

| Allegro Library Authoring | 专门用于创建和管理元件库(封装、符号等)。适合需要创建或编辑元件库的场景。如果你只需要编辑元件库,选择这个。 |

| Sigrity Aurora PCB Analysis | 专注于 PCB 的信号完整性(SI)、电源完整性(PI)和热分析。适合需要进行仿真和分析的项目。如果你需要仿真分析,选择这个。 |

| OrCAD X PCB Standard | OrCAD 的标准版本,提供基本的 PCB 设计功能。适合中小型项目。如果你习惯使用 OrCAD,且设计复杂度较低,可以选择这个。 |

| OrCAD X PCB Professional | OrCAD 的专业版本,提供更多高级功能,如约束管理和高速设计支持。适合中高复杂度的 PCB 设计。如果你需要更多功能,且习惯使用 OrCAD,可以选择这个。 |

| OrCAD X PCB Professional Plus | OrCAD 的最高版本,包含所有高级功能,如信号完整性分析和高速设计支持。适合复杂的高速 PCB 设计。如果你需要全面的功能,且习惯使用 OrCAD,可以选择这个。 |

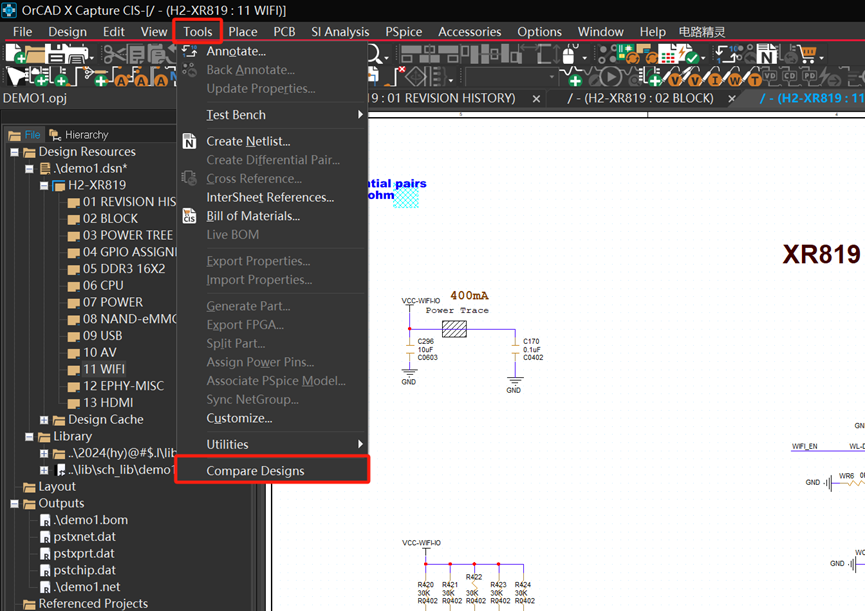

3.23 两份原理图文件对比设置

要对比两份原理图的差别,查看那里进行了改动。

选择Tools-Compare Designs就可以开启DSN设计差异对比的功能

Schematic,Page可以设置对比的范围其目的就是能够设置对部分原理图文件或者所有的原理图页面进行对比,方便工程师进行差异化的选择对比。

Output选择栏目里面可以对输出的参数进行配置,HTMLPath需要注意不要有中文路径,非法的字符等。指定的目录需要有读写权限。

Compare对比开启后,就会弹出Design Difference Summary显出差异的报告。

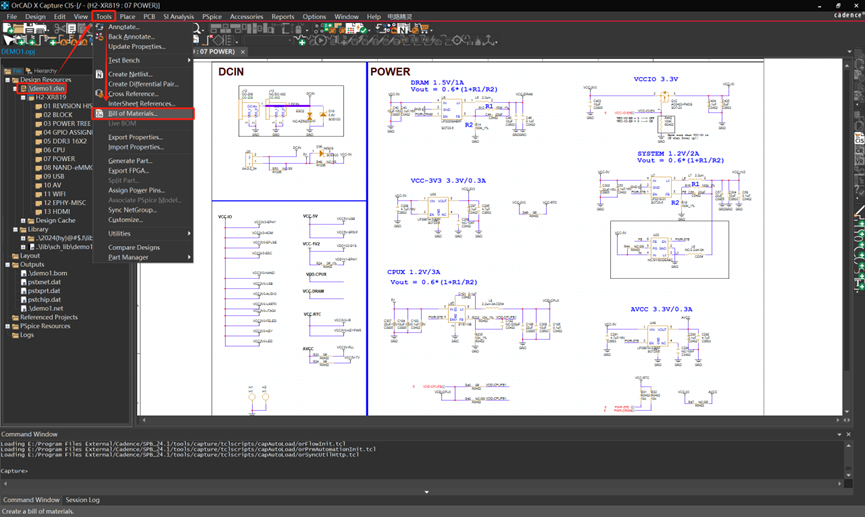

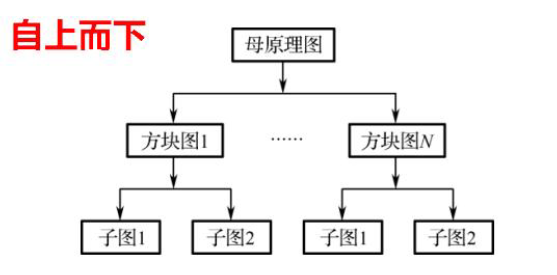

3.24 物料 BOM 表的设置与导出

- 选中.DSN根目录以后,执行菜单命令Tools-Bi1lof Materials…命令,来进行B0M清单的输出

- 在Header以及Combined Property String栏中,分别列出了需要输出的元素,依次是器件的数量、器件的位号、器件的属性值;

- 缺失器件的封装属性值,需要单独加上,格式就是跟Header以及Combined Property String致,勾选上Open in Excel,这样输出BOM清单就用EXCEL表格打开了,进行编辑整理,得到需要的BOM清单。

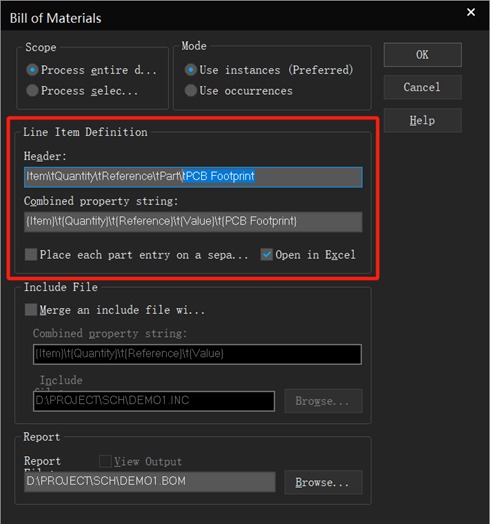

3.25 原理图的 PDF 打印输出

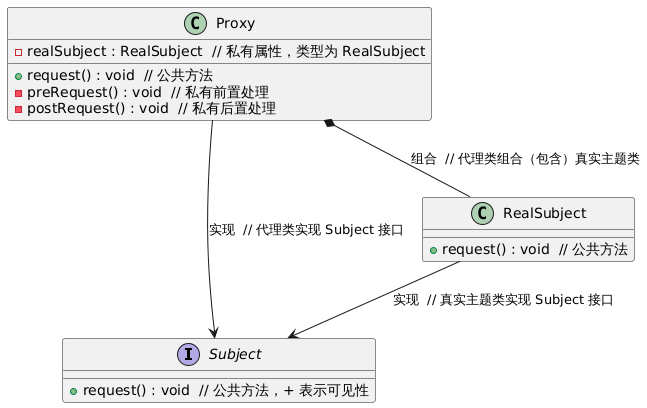

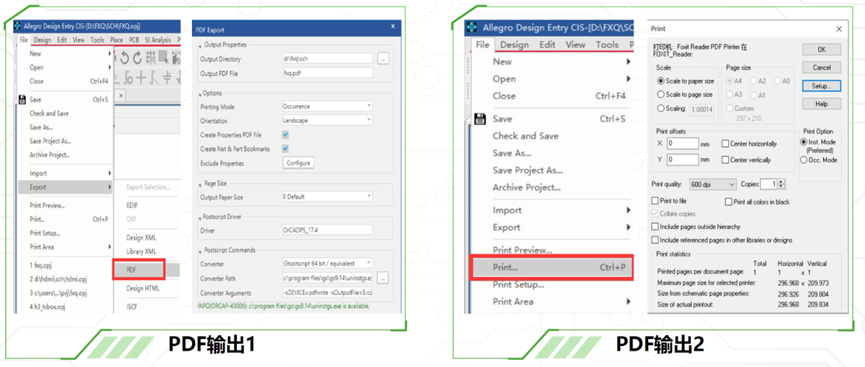

3.26 层次原理图的概念与设计

层次原理图就是把完整的电路系统按照功能划分为若干子系统,即子功能电路模块。这样,设计人员就可以把每一个子功能电路模块的相应原理图绘制出来,然后在这些子原理图之间建立连接关系,从而完成整个电路系统的设计。

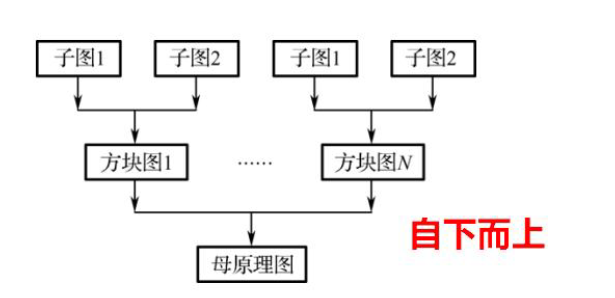

层次原理图设计的概念很像文件管理树状结构,设计者可以从绘制电路母原理图(简称母图)开始,逐级向下绘制子原理图(简称子图);也可以从绘制基本的子原理图开始,逐级向上绘制相应的母原理图。因此,层次原理图的设计方法可以分为两种,即自上而下的层次原理图设计方法和自下而上的层次原理图设计方法。

-

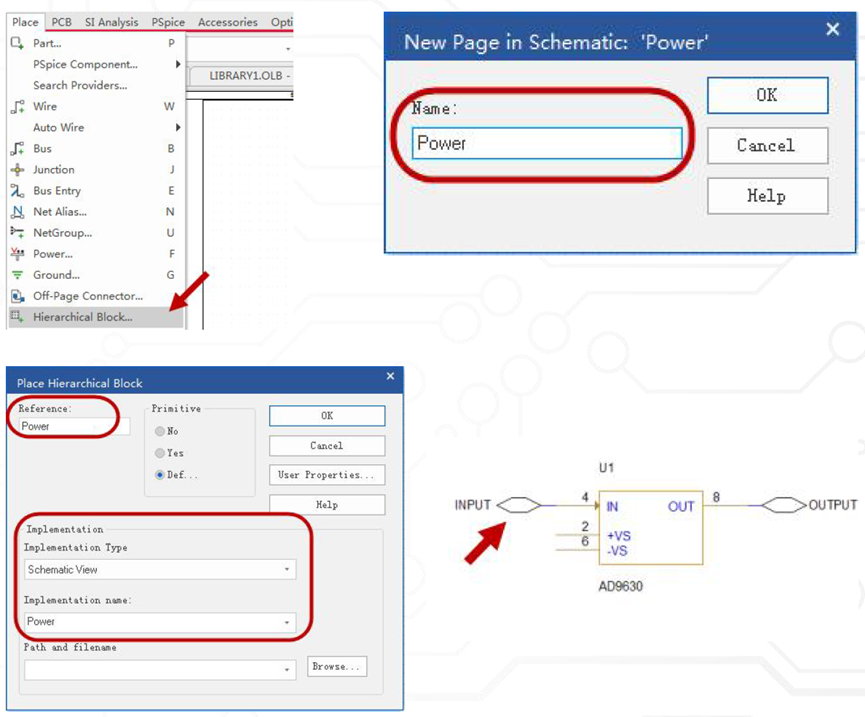

创建分级的模块Hierarchical Block,在原理图设计的页面,执行命令Place>Hierarchical Block…

-

在弹出的对话框中,输入分级模块的名称,如图所示,选择合适的参数,一般如图所示设置即可,点击OK,则层次式原理图分级模块创建完毕

-

在原理图页面画出合适的分级模块框框的大小这个也可以后面进行调整,用于分配子端口的以及总线的位置

-

双击新生成的图框,或者选中图框进行右击选择Descend Hierarchy,进行子图的设置在弹出来的对话框中填写原理图页面名,然后点击“OK”按钮,如图所示,设置子图的原理图页的名称

-

在新生成的原理图页面中进行原理图的子图绘制设置,并放置好与总框图的接口Hierarchical Port

-

双击放置的Hierarchical Port名,修改其名称,点击“OK”退出

-

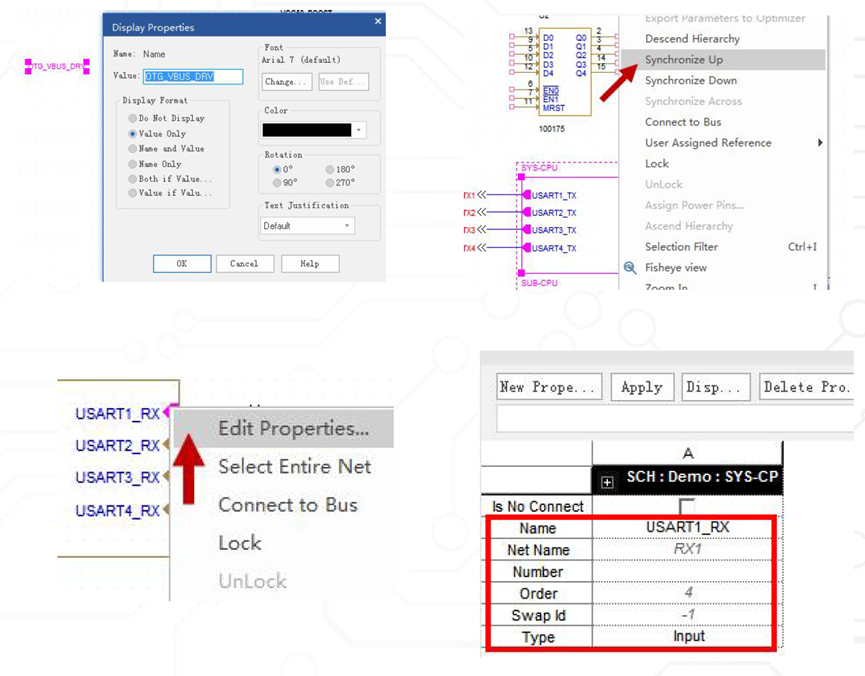

然后返回到放置Hierarchical Block的页面,选中已放置好的框并右击选取Synchronize Up,然后在此框边缘会出面子原理图页面中的Hierarchical Port,如图所示

-

选取需修改的Hierarchical Port右击选取Edit Properties进行编辑,如图所示

-

在弹出来的对话框对其属性进行修改,然后保存退出即可,如图所示,这样我们的层次原理图的模块就绘制完毕了。

最后

更多内容见专栏:【硬件设计遇到了不少问题】

Cadence 笔记传送门:【Cadence从原理图到PCB设计】

![[Java · 铢积寸累] 数据结构 — 数组类型 - 增 删 改 查](https://i-blog.csdnimg.cn/direct/6104fcecf60e445999cf0e525c22499f.png)