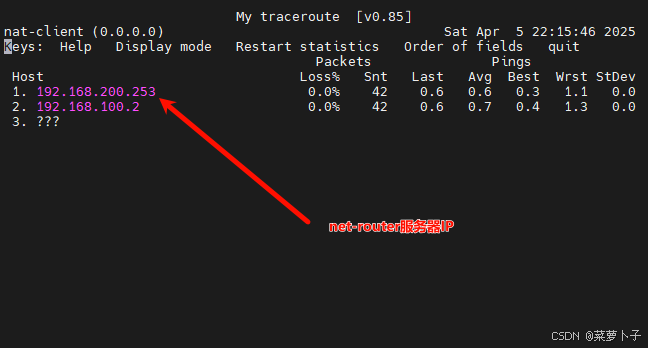

ARM CPU 中用于存储访问某个进程的页表的寄存器是 TTBR(Translation Table Base Register)。有TTBR0和TTBR1。TTBR0用户空间的一级页表基址,1是内核页表。cpu访存获取物理地址流程 如果mmu发现tlb里面miss就通过pdbg拿pa物理地址。Intel是CR3。ARMv7 架构中每个 CPU 核也都有相应的 TTBR 寄存器来支持进程地址空间的管理。MMU 在进行地址映射时,会根据 TTBCR(TTB 控制寄存器)中的值以及虚拟地址的高位地址来选择对应的 TTBR 寄存器。V8架构更多,根据运行级别还有不同的TTBR更多参考:arm和intel的页表目录基地址寄存器。

每次进程切换的时候会把进程控制块(Process Control Block,PCB在linux中是task struct接口)的mm_struct中的属于进程页表的一级页表基地址写入TTBR寄存器。这个结构是mm_struct的pgd_t * pgd

当CPU访问虚拟内存的时候,如果tlb misss,MMU(Memory Management Unit 内存管理单元)会根据TTBR寄存器的值(是硬件提供给软件配置的接口)MMU能够动态的根据配置去获取不同进程页表的一级页表地址,然后依次根据偏移逐级获取到虚拟地址对应的物理地址,或者对应的IO地址。并且通过本次访问之后会将映射关系存入MMU的TLB(Translation Lookaside Buffer,转换后备缓冲器。MMU中的一个高速缓存,用于存储最近使用的虚拟地址到物理地址的转换映射信息。TLB的作用是加速地址转换过程,减少内存访问时间,提高系统性能)中,方便下次快速访问。

当通过MMU将虚拟地址转化为物理地址的最后一级页表的时候,如果发现当前页表不在内存中(比如被换出到swap分区),页表的标记位present位0表示不在内存中。会触发缺页中断,缺页中断处理例程中会将实际内存从swap分区切换到内存中。该部分用户不感知。具体内促访问磁盘还是物理内存的时延差别待进一步确认。

【微知】ARM CPU是如何获取某个进程的页表的?(通过TTBR寄存器,MMU进行处理)

news2026/2/16 8:07:44

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/2329525.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

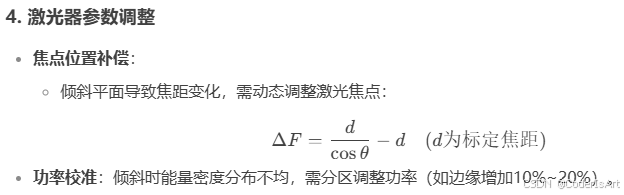

激光加工中平面倾斜度的矫正

在激光加工中,加工平面的倾斜度矫正至关重要,直接影响加工精度和材料处理效果。以下是系统的矫正方法和步骤: 5. 验证与迭代 二次测量:加工后重新检测平面度,确认残余误差。 反馈优化:根据误差分布修正补偿…

rdiff-backup备份

目录

1. 服务器备份知识点

1.1 备份策略

1.2 备份步骤和宝塔面板简介

1.3 CentOS7重要目录

2. 备份工具

2.1 tar -g

备份演示

2. rsync

备份演示

3. rdiff-backup

备份演示

4. 差异和优缺点

3. rdiff-backup安装和使用

3.1 备份命令rdiff-backup

3.2 恢复命令--…

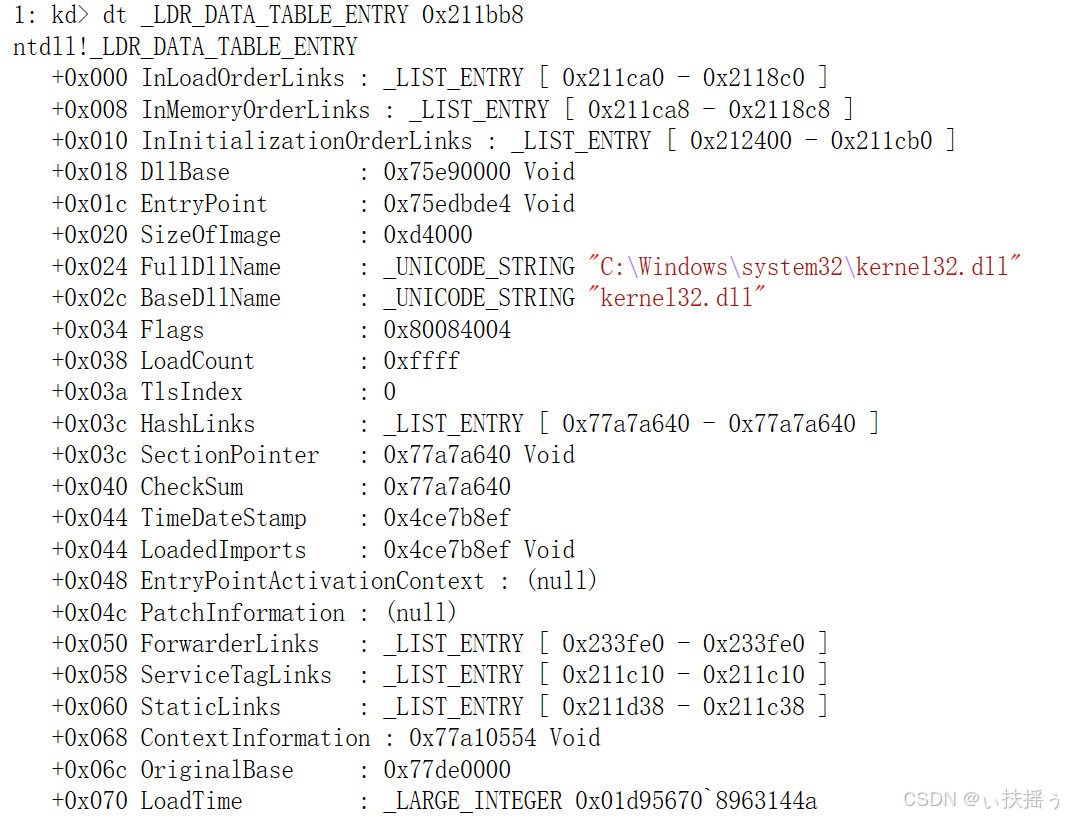

PE结构(十五)系统调用与函数地址动态寻找

双机调试

当需要分析一个程序时,这个程序一定是可以调试的,操作系统也不例外。在调试过程中下断点是很重要的

当我们对一个应用程序下断点时,应用程序是挂起的。但当我们对操作系统的内核程序下断点时,被挂起的不是内核程序而是…

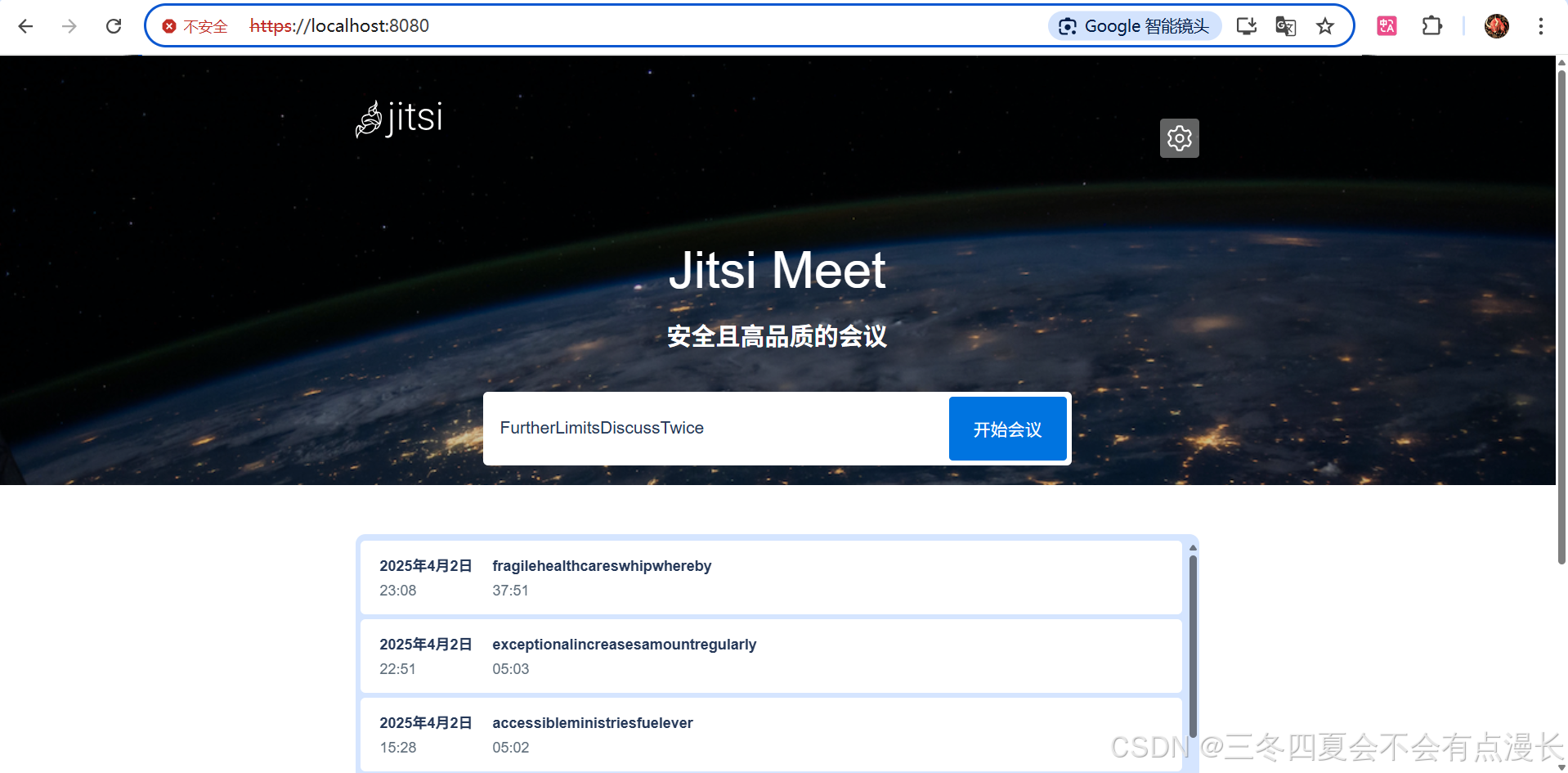

webrtc 本地运行的详细操作步骤 1

前言

选修课的一个课程设计,需要我们本地运行这个开源项目,给我的压力非常大,因为确实不是很熟练这种操作。但是还是得做。谨以此文,纪念这个过程。 之前自己在 github 上面看到有代码仓库,但是比较复杂,在…

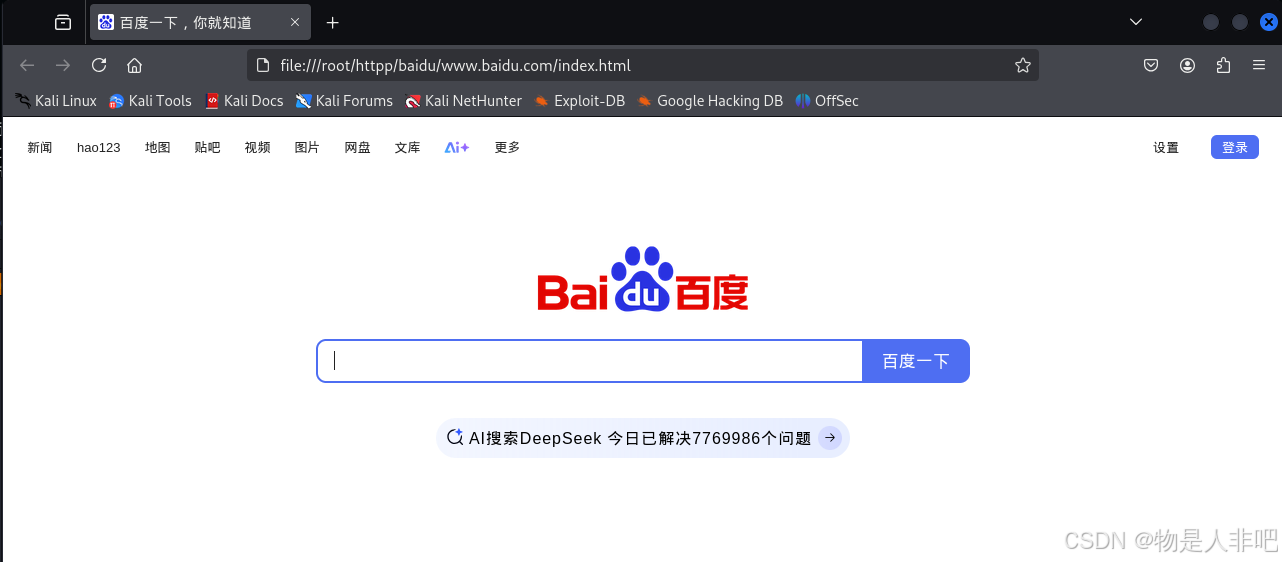

kali——httrack

目录

前言

使用教程 前言

HTTrack 是一款运行于 Kali Linux 系统中的开源网站镜像工具,它能将网站的页面、图片、链接等资源完整地下载到本地,构建出一个和原网站结构相似的离线副本。 使用教程

apt install httrack //安装httrack工具

httrac…

【计算机网络】Linux配置SNAT/DNAT策略

什么是NAT?

NAT 全称是 Network Address Translation(网络地址转换),是一个用来在多个设备共享一个公网 IP上网的技术。

NAT 的核心作用:将一个网络中的私有 IP 地址,转换为公网 IP 地址,从而…

AI安全:构建负责任且可靠的系统

AI已成为日常生活中无处不在的助力,随着AI系统能力和普及性的扩展,安全因素变得愈发重要。从基础模型构建者到采用AI解决方案的企业,整个AI生命周期中的所有相关方都必须共同承担责任。 为什么AI安全至关重要?

对于企业而言&…

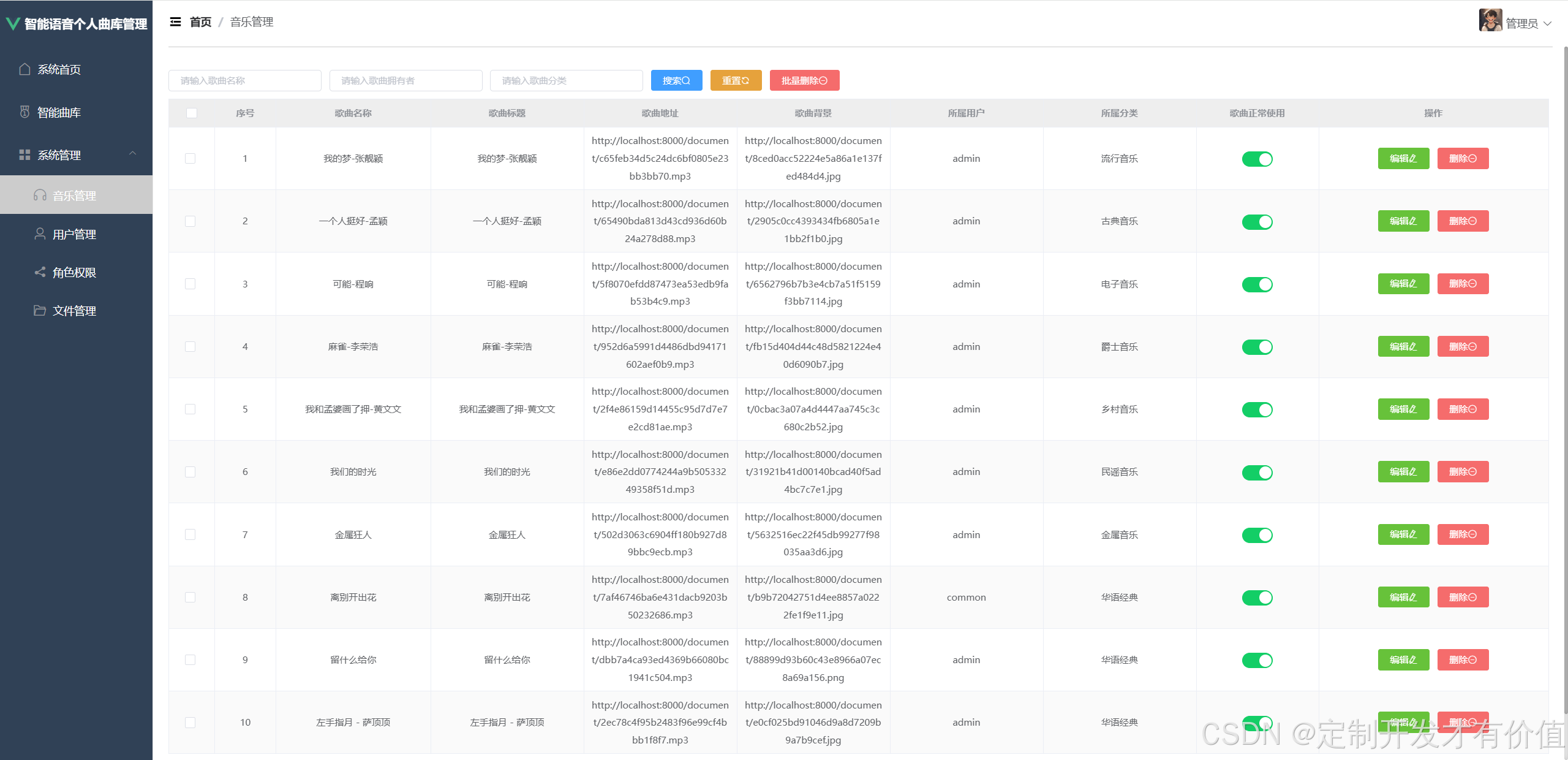

VUE+SPRINGBOOT+语音技术实现智能语音歌曲管理系统

语音控制歌曲的播放、暂停、增删改查 <template><div class"Music-container"><div style"margin: 10px 0"><!--检索部分--><el-input style"width: 200px;" placeholder"请输入歌曲名称"v-model"sen…

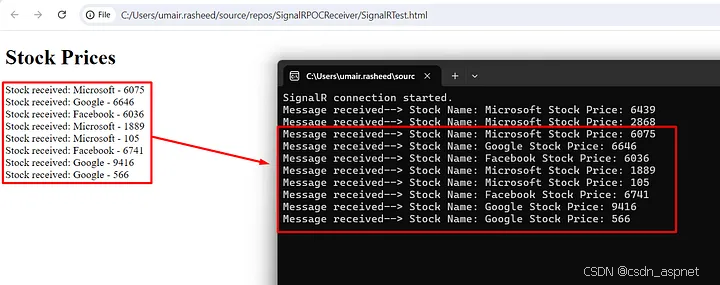

使用 SignalR 在 .NET Core 8 最小 API 中构建实时通知

示例代码:https://download.csdn.net/download/hefeng_aspnet/90448094

介绍 构建实时应用程序已成为现代 Web 开发中必不可少的部分,尤其是对于通知、聊天系统和实时更新等功能。SignalR 是 ASP.NET 的一个强大库,可实现服务器端代码和客户…

复古未来主义屏幕辉光像素化显示器反乌托邦效果PS(PSD)设计模板样机 Analog Retro-Futuristic Monitor Effect

这款模拟复古未来主义显示器效果直接取材于 90 年代赛博朋克电影中的黑客巢穴,将粗糙的屏幕辉光和像素化的魅力强势回归。它精准地模仿了老式阴极射线管显示器,能将任何图像变成故障频出的监控画面或高风险的指挥中心用户界面。和……在一起 2 个完全可编…

技术驱动革新,强力巨彩LED软模组助力创意显示

随着LED显示技术的不断突破,LED软模组因其独特的柔性特质和个性化显示效果,正逐渐成为各类应用场景的新宠。强力巨彩软模组R3.0H系列具备独特的可塑造型能力与技术创新,为商业展示、数字艺术、建筑装饰等领域开辟全新视觉表达空间。 LED…

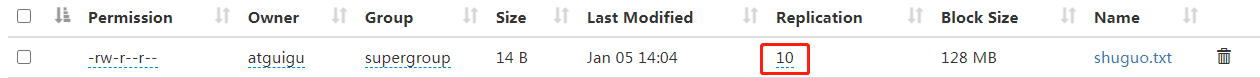

Spark,HDFS概述

HDFS组成构架: 注: NameNode(nn):就是 Master,它是一个主管、管理者。 (1) 管理 HDFS 的名称空间; (2) 配置副本策略。记录某些文件应该保持几个副本; (3) 管理数据块(…

【数据结构】图论进阶:生成树、生成森林与权值网络的终极解析

图的基本概念 导读一、图中的树与森林1.1 生成树与生成森林1.1.1 生成树1.1.2 生成森林1.1.3 生成树、生成森林与连通分量结点的关系边的关系 1.2 有向图中的树与森林1.2.1 有向树与有向森林1.2.2 生产有向树与生成有向森林1.2.3 有向树与生成有向树的区别1.2.4 有向森林与生成…

C和C++(list)的链表初步

链表是构建其他复杂数据结构的基础,如栈、队列、图和哈希表等。通过对链表进行适当的扩展和修改,可以实现这些数据结构的功能。想学算法,数据结构,不会链表是万万不行的。这篇笔记是一名小白在学习时整理的。

C语言

链表部分

…

【KWDB创作者计划】_KaiwuDB 2.1.0 单节点裸机部署

大家好,这里是 DBA学习之路,专注于提升数据库运维效率。 目录 前言KWDB 介绍安装准备环境信息配置要求操作系统软件依赖端口要求安装包下载 部署 KWDB简单实用连接数据库创建数据库创建用户创建时序表 前言

今天无意间在墨天轮看到一个征文活动 征文大赛…

前端快速入门学习3——CSS介绍与选择器

1.概述

CSS全名是cascading style sheets,中文名层叠样式表。 用于定义网页样式和布局的样式表语言。 通过 CSS,你可以指定页面中各个元素的颜色、字体、大小、间距、边框、背景等样式,从而实现更精确的页面设计。

HTML与CSS的关系:HTML相当…

Redash:一个开源的数据查询与可视化工具

Redash 是一款免费开源的数据可视化与协作工具,可以帮助用户快速连接数据源、编写查询、生成图表并构建交互式仪表盘。它简化了数据探索和共享的过程,尤其适合需要团队协作的数据分析场景。 数据源

Redash 支持各种 SQL、NoSQL、大数据和 API 数据源&am…

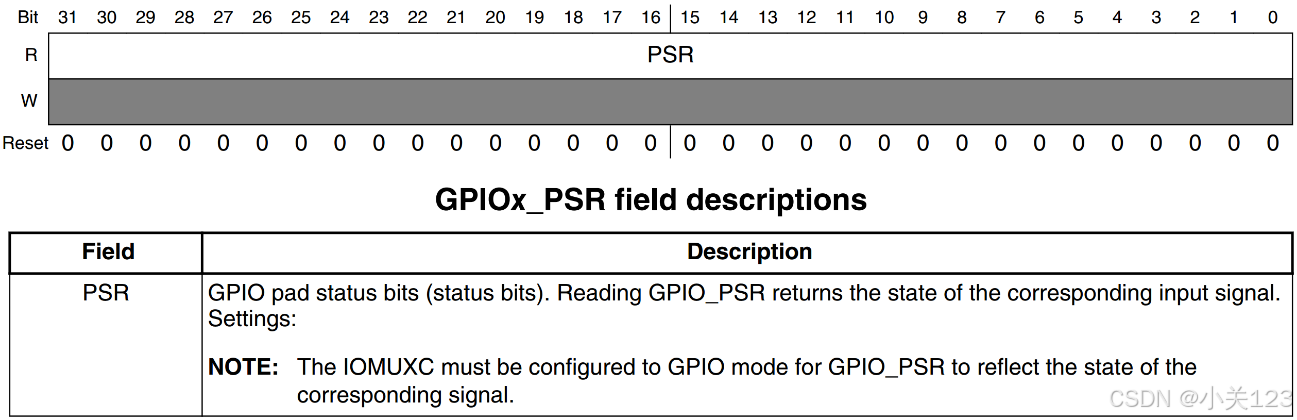

嵌入式Linux驱动—— 1 GPIO配置

目录

1.GPIO操作

1.1 IO命名

1.2 GPIO 时钟使能(CCM)

1.3 IO 复用(IOMUXC)

1.4 IO 配置

1.5 GPIO 配置 1.GPIO操作

GPIO操作主要是以下流程:

使能某组GPIO模块(GPIO1、2、...)&#…

[ICLR 2025]Biologically Plausible Brain Graph Transformer

论文网址:Biologically Plausible Brain Graph Transformer

英文是纯手打的!论文原文的summarizing and paraphrasing。可能会出现难以避免的拼写错误和语法错误,若有发现欢迎评论指正!文章偏向于笔记,谨慎食用 目录 …

SpringBoot+MyBatis Plus+PageHelper+vue+mysql 实现用户信息增删改查功能

静态资源展示

(1)静态资源下载 (2)下载后文件放到resources/static 目录下 (3) main函数启动项目访问对应文件,http://127.0.0.1:8080/user-list.html

数据库添加表和数据

SET FOREIGN_KEY_CHECKS0;-- --------…

![[ICLR 2025]Biologically Plausible Brain Graph Transformer](https://i-blog.csdnimg.cn/direct/0a5fd0c5509a47d1a980a2b2d0453c66.png)