目录

一、实验目的

二、实验环境

三、实验原理

四、实验任务

代码

一、实验目的

1. 理解MIPS处理器指令格式及功能。

2. 掌握lw, sw, beq, bne, lui, j, jal指令格式与功能。

3. 掌握ModelSim和ISE\Vivado工具软件。

4. 掌握基本的测试代码编写和FPGA开发板使用方法。

二、实验环境

1. 装有ModelSim和ISE\Vivado的计算机。

2. Sword\Basys3\EGo1实验系统。

三、实验原理

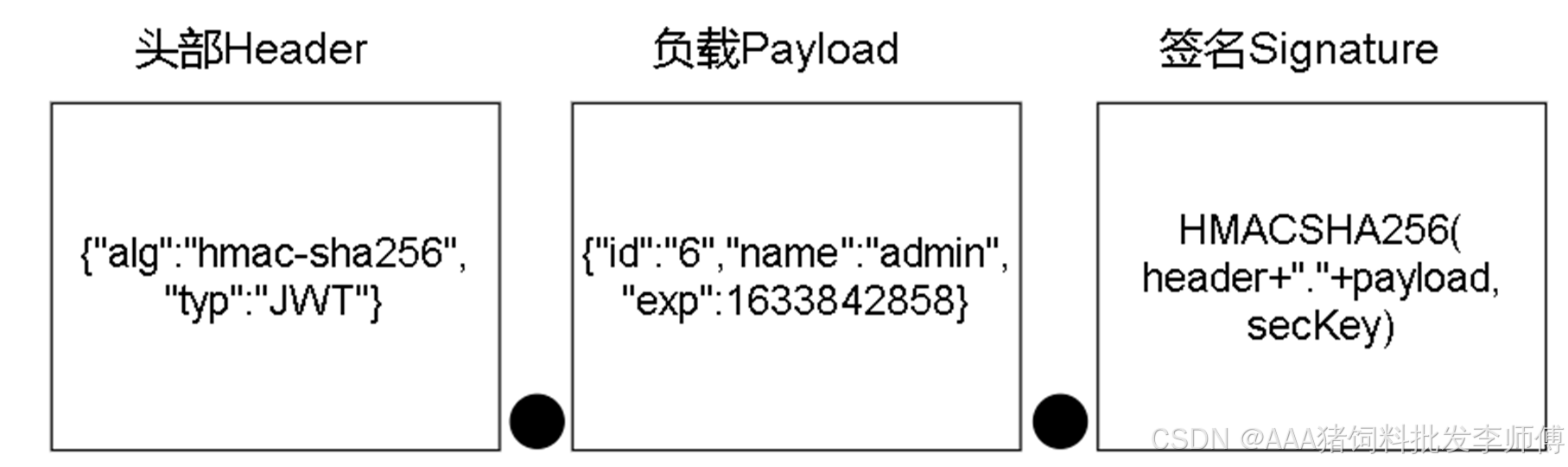

MIPS 32位处理器的指令格式分为R型、I型和J型。R型为寄存器型,即两个源操作数和目的操作数都是寄存器性。I型为操作数含有立即数。而J型特指转移类型指令,如图1所示。

如图2所示,本次实验将实现实验挑选剩余部分MIPS处理器指令进行实现。主要是部分R型和J型指令。指令的格式如图2所示,指令的功能参考资料1(李亚民. 计算机原理与设计:Verilog HDL版)。

如图3所示为按照单指令周期设计MIPS处理器内部结构。所有控制信号及字段均标注出来。另外,每条指令周期都包含2个clk,即PC模块用1个clk,Regfile和DataMem模块用1个clk,也可以说是由2个时钟构成的指令流水线。为了便于今后的扩展,将MIPS处理器进行了分阶段设计,这样结构更清晰,也有利于流水线的设计。随着后续指令的不断添加,处理器内部结构设计也会进行相应的调整,但时序部分应保持不变。

四、实验任务

1. 用Verilog HDL设计32位MIPS处理指令实现,参照图3的MIPS内部结构示意图,先编写基本实现代码,即能实现j和jal指令的取指令和执行指令,在Modelsim上仿真测试。

2. 参照图2,将设计的MIPS处理器改造为分阶段实现方案,注意每条指令周期平均只包含1个时钟周期。

3.编写指令存储测试文件,在Modelsim上调试通过。

代码

`define RstEnable 1'b1

`define RstDisable 1'b0

`define RomEnable 1'b1

`define RomDisable 1'b0

`define Zero 0

`define Valid 1'b1

`define Invalid 1'b0

//I

`define Inst_ori 6'b001101

`define Inst_addi 6'b001000

`define Inst_andi 6'b001100

`define Inst_xori 6'b001110

`define Inst_lui 6'b001111

`define Inst_subi 6'b001001

//R

`define Inst_r 6'b000000

`define Inst_add 6'b100000

`define Inst_sub 6'b100010

`define Inst_and 6'b100100

`define Inst_or 6'b100101

`define Inst_xor 6'b100110

`define Inst_sll 6'b000000

`define Inst_srl 6'b000010

`define Inst_sra 6'b000011

//J

`define Inst_j 6'b000010

`define Inst_jal 6'b000011

`define Inst_jr 6'b001000

`define Inst_beq 6'b000100

`define Inst_bne 6'b000101

`define Nop 6'b000000

`define Or 6'b000001

`define Add 6'b000010

`define And 6'b000011

`define Xor 6'b000100

`define Lui 6'b000101

`define Sub 6'b000110

`define Sll 6'b000111

`define Srl 6'b001000

`define Sra 6'b001001

`define J 6'b001010

`define Jal 6'b001011

`define Beq 6'b001100

`define Bne 6'b001101

`define Jr 6'b001110`include "define.v"

module EX(

input wire rst,

input wire [5:0] op,

input wire [31:0] regaData,

input wire [31:0] regbData,

input wire regcWrite_i,

input wire [4:0]regcAddr_i,

output reg [31:0] regcData,

output wire regcWrite,

output wire [4:0] regcAddr

);

always@(*)

if(rst == `RstEnable)

regcData = `Zero;

else

begin

case(op)

`Or:

regcData = regaData | regbData;

`Add:

regcData = regaData + regbData;

`And:

regcData = regaData & regbData;

`Xor:

regcData = regaData ^ regbData;

`Lui:

regcData = regaData;

/*`Lui:

regcData = regaData | regbData;

*/

`Sub:

regcData = regaData - regbData;

`Sll:

regcData = regbData << regaData;

`Srl:

regcData = regbData >> regaData;

`Sra:

regcData = ($signed(regbData)) >>> regaData;

`J:

regcData = `Zero;

`Jr:

regcData = `Zero;

`Jal:

regcData = regbData;

`Beq:

regcData = `Zero;

`Bne:

regcData = `Zero;

default:

regcData = `Zero;

endcase

end

assign regcWrite = regcWrite_i;

assign regcAddr = regcAddr_i;

endmodule

`include "define.v";

module ID (

input wire rst,

input wire [31:0] pc, //J

input wire [31:0] inst,

input wire [31:0] regaData_i,

input wire [31:0] regbData_i,

output reg [5:0] op,

output reg [31:0] regaData,

output reg [31:0] regbData,

output reg regaRead,

output reg regbRead,

output reg regcWrite,

output reg [4:0] regaAddr,

output reg [4:0] regbAddr,

output reg [4:0] regcAddr,

output reg [31:0] jAddr, //J

output reg jCe//J

);

wire [5:0] inst_op = inst[31:26];

reg [31:0] imm;

//R

wire[5:0] func = inst[5:0];

//J

wire [31:0] npc = pc + 4;

always@(*)

if(rst == `RstEnable)

begin

op = `Nop;

regaRead = `Invalid;

regbRead = `Invalid;

regcWrite = `Invalid;

regaAddr = `Zero;

regbAddr = `Zero;

regcAddr = `Zero;

imm = `Zero;

jCe = `Invalid;//J

jAddr = `Zero;//J

end

else

begin

jCe = `Invalid;//J

jAddr = `Zero;//J

case(inst_op)

`Inst_ori:

begin

op = `Or;

regaRead = `Valid;

regbRead = `Invalid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = `Zero;

regcAddr = inst[20:16];

imm = {16'h0, inst[15:0]};

end

`Inst_andi:

begin

op = `And;

regaRead = `Valid;

regbRead = `Invalid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = `Zero;

regcAddr = inst[20:16];

imm = {16'h0, inst[15:0]};

end

`Inst_xori:

begin

op = `Xor;

regaRead = `Valid;

regbRead = `Invalid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = `Zero;

regcAddr = inst[20:16];

imm = {16'h0, inst[15:0]};

end

`Inst_addi:

begin

op = `Add;

regaRead = `Valid;

regbRead = `Invalid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = `Zero;

regcAddr = inst[20:16];

imm = {

{16{inst[15]}}, inst[15:0]};

end

`Inst_subi:

begin

op = `Sub;

regaRead = `Valid;

regbRead = `Invalid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = `Zero;

regcAddr = inst[20:16];

imm = {

{16{inst[15]}}, inst[15:0]};

end

`Inst_lui:

begin

op = `Lui;

regaRead = `Invalid;

regbRead = `Invalid;

regcWrite = `Valid;

regaAddr = `Zero;

regbAddr = `Zero;

regcAddr = inst[20:16];

imm = {inst[15:0],16'h0};

end

`Inst_r:

case(func)

`Inst_add:

begin

op = `Add;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`Inst_or:

begin

op = `Or;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`Inst_sub:

begin

op = `Sub;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`Inst_and:

begin

op = `And;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`Inst_xor:

begin

op = `Xor;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = `Zero;

end

`Inst_sll:

begin

op = `Sll;

regaRead = `Invalid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = `Zero;

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = {27'b0,inst[10:6]};

end

`Inst_srl:

begin

op = `Srl;

regaRead = `Invalid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = `Zero;

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = {27'b0,inst[10:6]};

end

`Inst_sra:

begin

op = `Sra;

regaRead = `Invalid;

regbRead = `Valid;

regcWrite = `Valid;

regaAddr = `Zero;

regbAddr = inst[20:16];

regcAddr = inst[15:11];

imm = {27'b0,inst[10:6]};

end

`Inst_jr:

begin

op = `Jr;

regaRead = `Valid;//rs

regbRead = `Invalid;

regcWrite = `Invalid;

regaAddr = inst[25:21];

regbAddr = `Zero;

regcAddr = `Zero;

jAddr = regaData;

jCe = `Valid;

imm = `Zero;

end

default:

begin

regaRead = `Invalid;

regbRead = `Invalid;

regcWrite = `Invalid;

regaAddr = `Zero;

regbAddr = `Zero;

regcAddr = `Zero;

imm = `Zero;

end

endcase

//J

`Inst_j:

begin

op = `J;

regaRead = `Invalid;

regbRead = `Invalid;

regcWrite = `Invalid;

regaAddr = `Zero;

regbAddr = `Zero;

regcAddr = `Zero;

jAddr = {npc[31:28], inst[25:0], 2'b00};

jCe = `Valid;

imm = `Zero;

end

`Inst_jal:

begin

op = `Jal;

regaRead = `Invalid;

regbRead = `Invalid;

regcWrite = `Valid;

regaAddr = `Zero;

regbAddr = `Zero;

regcAddr = 5'b11111;

jAddr = {npc[31:28], inst[25:0], 2'b00};

jCe = `Valid;

imm = npc;

end

//J

`Inst_beq:

begin

op = `Beq;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Invalid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = `Zero;

jAddr = npc+{

{14{inst[15]}},inst[15:0],2'b00};

jCe=(regaData==regbData)?`Valid:`Invalid;

/* if(regaData==regbData)

jCe = `Valid;

else

jCe = `Invalid;*/

imm = `Zero;

end

`Inst_bne:

begin

op = `Bne;

regaRead = `Valid;

regbRead = `Valid;

regcWrite = `Invalid;

regaAddr = inst[25:21];

regbAddr = inst[20:16];

regcAddr = `Zero;

jAddr = npc+{

{14{inst[15]}},inst[15:0],2'b00};

jCe=(regaData!=regbData)?`Valid:`Invalid;

/* if(regaData!=regbData)

jCe = `Valid;

else

jCe = `Invalid;

*/

imm = `Zero;

end

default:

begin

op = `Nop;

regaRead = `Invalid;

regbRead = `Invalid;

regcWrite = `Invalid;

regaAddr = `Zero;

regbAddr = `Zero;

regcAddr = `Zero;

imm = `Zero;

end

endcase

end

always@(*)

if(rst == `RstEnable)

regaData = `Zero;

else if(regaRead == `Valid)

regaData = regaData_i;

else

regaData = imm;

always@(*)

if(rst == `RstEnable)

regbData = `Zero;

else if(regbRead == `Valid)

regbData = regbData_i;

else

regbData = imm;

endmodule

`include "define.v"

module IF(

input wire clk,

input wire rst,

input wire [31:0] jAddr,//J

input wire jCe,//J

output reg ce,

output reg [31:0] pc

);

always@(*)

if(rst == `RstEnable)

ce = `RomDisable;

else

ce = `RomEnable;

/* always@(posedge clk)

if(ce == `RomDisable)

pc = `Zero;

else

pc = pc + 4;

*/

always@(posedge clk)

if(ce == `RomDisable)

pc = `Zero;

else if(jCe == `Valid)//J

pc = jAddr;

else

pc = pc + 4;

endmodule

`include "define.v"

module MIPS(

input wire clk,

input wire rst,

input wire [31:0] instruction,

output wire romCe,

output wire [31:0] instAddr

);

wire [31:0] regaData_regFile, regbData_regFile;

wire [31:0] regaData_id, regbData_id;

wire [31:0] regcData_ex;

wire [5:0] op;

wire regaRead, regbRead;

wire [4:0] regaAddr, regbAddr;

wire regcWrite_id, regcWrite_ex;

wire [4:0] regcAddr_id, regcAddr_ex;

//J

wire [31:0] jAddr;

wire jCe;

IF if0(

.clk(clk),

.rst(rst),

.jAddr(jAddr),//J

.jCe(jCe),//J

.ce(romCe),

.pc(instAddr)

);

ID id0(

.pc(instAddr),//J

.jAddr(jAddr),//J

.jCe(jCe),//J

.rst(rst),

.inst(instruction),

.regaData_i(regaData_regFile),

.regbData_i(regbData_regFile),

.op(op),

.regaData(regaData_id),

.regbData(regbData_id),

.regaRead(regaRead),

.regbRead(regbRead),

.regaAddr(regaAddr),

.regbAddr(regbAddr),

.regcWrite(regcWrite_id),

.regcAddr(regcAddr_id)

);

EX ex0(

.rst(rst),

.op(op),

.regaData(regaData_id),

.regbData(regbData_id),

.regcWrite_i(regcWrite_id),

.regcAddr_i(regcAddr_id),

.regcData(regcData_ex),

.regcWrite(regcWrite_ex),

.regcAddr(regcAddr_ex)

);

RegFile regfile0(

.clk(clk),

.rst(rst),

.we(regcWrite_ex),

.waddr(regcAddr_ex),

.wdata(regcData_ex),

.regaRead(regaRead),

.regbRead(regbRead),

.regaAddr(regaAddr),

.regbAddr(regbAddr),

.regaData(regaData_regFile),

.regbData(regbData_regFile)

);

endmodule

`include "define.v"

module RegFile(

input wire clk,

input wire rst,

input wire we,

input wire [4:0] waddr,

input wire [31:0] wdata,

input wire regaRead,

input wire regbRead,

input wire [4:0] regaAddr,

input wire [4:0] regbAddr,

output reg [31:0] regaData,

output reg [31:0] regbData

);

reg [31:0] reg32 [31 : 0];

always@(*)

if(rst == `RstEnable)

regaData = `Zero;

else if(regaAddr == `Zero)

regaData = `Zero;

else

regaData = reg32[regaAddr];

always@(*)

if(rst == `RstEnable)

regbData = `Zero;

else if(regbAddr == `Zero)

regbData = `Zero;

else

regbData = reg32[regbAddr];

always@(posedge clk)

if(rst != `RstEnable)

if((we == `Valid) && (waddr != `Zero))

reg32[waddr] = wdata;

else ;

endmodulemodule SoC(

input wire clk,

input wire rst

);

wire [31:0] instAddr;

wire [31:0] instruction;

wire romCe;

MIPS mips0(

.clk(clk),

.rst(rst),

.instruction(instruction),

.instAddr(instAddr),

.romCe(romCe)

);

InstMem instrom0(

.ce(romCe),

.addr(instAddr),

.data(instruction)

);

endmodule

`include "define.v"

module soc_tb;

reg clk;

reg rst;

initial

begin

clk = 0;

rst = `RstEnable;

#100

rst = `RstDisable;

#10000 $stop;

end

always #10 clk = ~ clk;

SoC soc0(

.clk(clk),

.rst(rst)

);

endmodule