微控制器 (MCU) 的时钟系统是系统运行的核心,它提供了各模块所需的时钟信号。本文以 GD32E103 系列 MCU 为例,详细讲解其 时钟树结构(Clock Tree)。通过理解时钟源、分配与预分频器设置,可以灵活配置系统时钟以实现高性能与低功耗平衡。

因为最近发现纯软件实现的AI应用并没什么竞争力,或者说被抄袭的成本比较低,复制也比较简单,于是重新开始上课学习MCU,顺便记录一点东西

在前面的文章如何在资源受限例如1核和1G内存的设备上运行一个合适的向量存储库及如何优化 有简单测试了下可能性,后续我会慢慢实现,做一个只能的玩偶~

时钟源

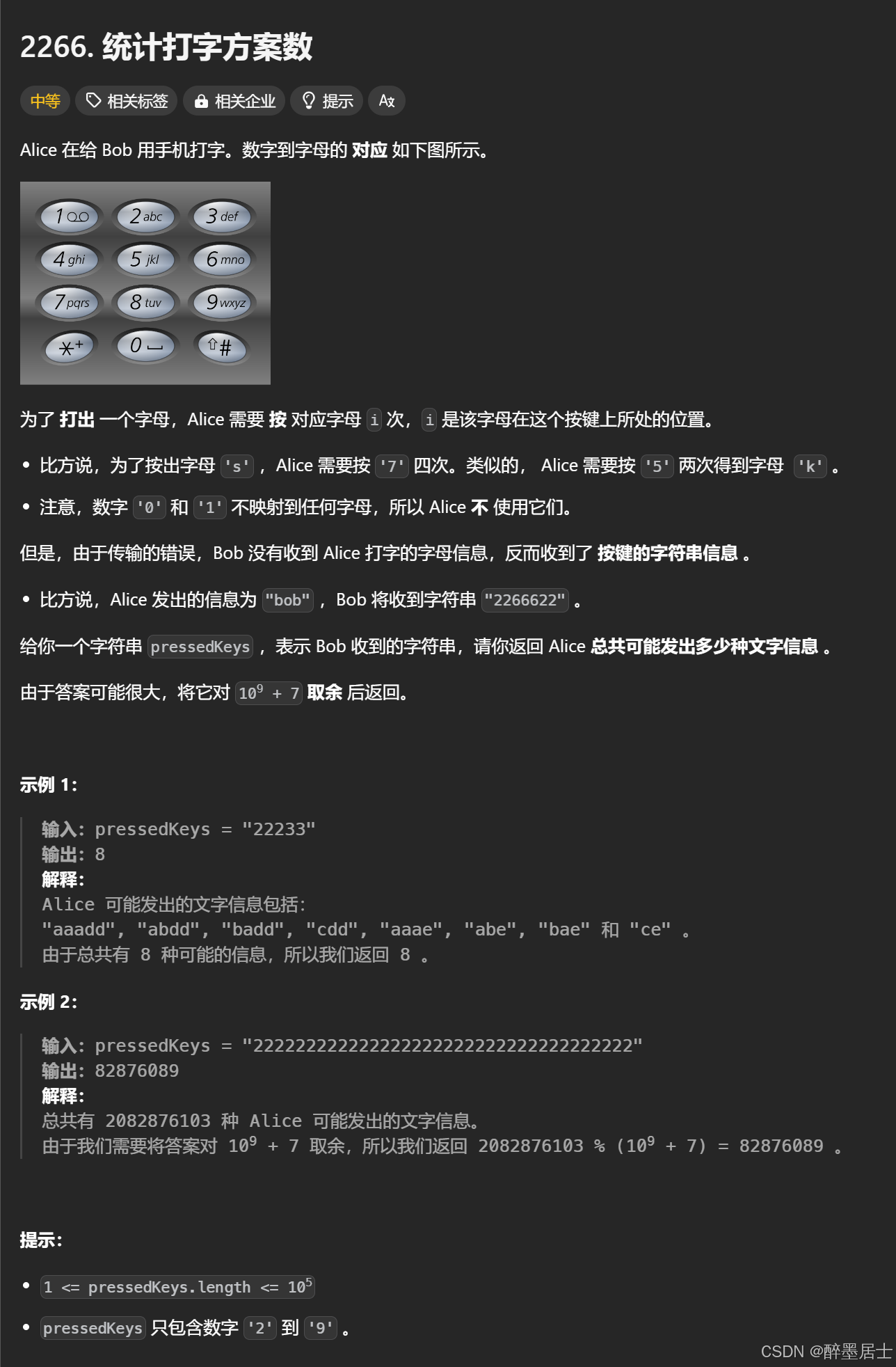

GD32E103 支持多种时钟源,提供不同的频率和应用场景:

-

HSI (High-Speed Internal)

- 内部高速RC振荡器,频率为 8MHz。

- 默认的系统启动时钟源,启动速度快。

-

HSE (High-Speed External)

- 外部高速晶振(通常为 4~32MHz)。

- 提供精确、稳定的时钟信号,适合对频率精度要求高的场景。

-

LSI (Low-Speed Internal)

- 内部低速RC振荡器,频率为 40kHz。

- 用于低功耗模式或独立的 RTC(实时时钟)功能。

-

LSE (Low-Speed External)

- 外部低速晶振(通常为 32.768kHz)。

- 主要用于 RTC 的时间保持。

-

PLL (Phase-Locked Loop)

- 相位锁定环倍频器,支持输入时钟的多倍频输出。

- 倍频后可生成高达 120MHz 的主系统时钟,适合高速运算场景。

时钟分配与分频

时钟源经过分配和分频器后被用于不同模块:

1. 系统时钟路径

- 系统时钟(CK_SYS)通过多路选择器选择以下来源:

- HSI

- HSE

- PLL 输出

- GD32E103 的系统时钟最高支持 120MHz。

2. 预分频器

系统时钟通过预分频器分配到不同总线和外设:

-

AHB(Advanced High-Performance Bus)

- 主总线,连接 CPU、SRAM、DMA 等核心模块。

- 最大频率:120MHz。

-

APB1(Advanced Peripheral Bus 1)

- 低速外设总线(如 USART、I2C、定时器等)。

- 最大频率:60MHz。

-

APB2(Advanced Peripheral Bus 2)

- 高速外设总线(如 GPIO、SPI 等)。

- 最大频率:120MHz。

3. 外设分频器

部分外设的时钟需要进一步调整:

- 定时器

- 可直接使用倍频后的 PLL 时钟。

- ADC 分频器

- 降低时钟频率以满足 ADC 的 40MHz 输入限制。

特殊用途的时钟

-

USB 时钟

- USB 模块需要精确的 48MHz 时钟。

- 由 PLL 倍频输出的专用通道生成,确保符合 USB 协议。

-

RTC 时钟

- RTC 可选择 LSE、LSI 或 HSE 的低频分频信号作为时钟源。

- 支持低功耗时间保持功能。

时钟配置举例:生成 120MHz 系统时钟

以下是实现 120MHz 系统时钟的一般步骤:

-

选择 HSE 作为输入时钟

- 假设外部晶振频率为 8MHz。

- 配置 PLLPRESEL = 1(选择 HSE)。

- 配置 PREVDIVSEL = 1(无分频,直接进入 PLL)。

-

设置 PLL 倍频系数

- 设置 PLLMF = 15。

- PLL 输出频率为:

[

8 , \text{MHz} \times 15 = 120 , \text{MHz}

]

-

配置系统时钟选择器

- 将系统时钟选择器设置为 10,选择 PLL 输出作为系统时钟。

动态切换时钟源

GD32E103 支持在运行时通过控制信号动态切换时钟源:

- 00:HSI

- 01:HSE

- 10:PLL

例如,当外部晶振失效时,系统可自动切换到内部 HSI,保障时钟连续性。

总结

GD32E103 的时钟树结构设计灵活,能满足多种应用场景:

- 高速运算: 通过 PLL 提供高达 120MHz 的系统主频。

- 低功耗模式: 支持低速 RC 振荡器 (LSI) 和低速晶振 (LSE)。

- 外设优化: AHB、APB1、APB2 总线分频器实现不同频率的精确匹配。

理解时钟树结构和时钟配置方式是优化系统性能和功耗的关键。

![[Redis#0] iredis: linux上redis超好用的环境配置](https://i-blog.csdnimg.cn/direct/46f84d92c4b84d8d8c60c9d8c147d84d.png)

![[Unity Demo]从零开始制作空洞骑士Hollow Knight第二十二集:制作游戏的对话系统](https://i-blog.csdnimg.cn/direct/898fc97f5a984c5e93d5b4aa8dd07fdc.png)