FIFO使用中需要注意的若干问题

文章目录

- FIFO使用中需要注意的若干问题

- 前言

- 场景1:包数据FIFO设计之冗余法

- 场景2、FIFO数据传输之流控

- 总结

前言

场景1:包数据FIFO设计之冗余法

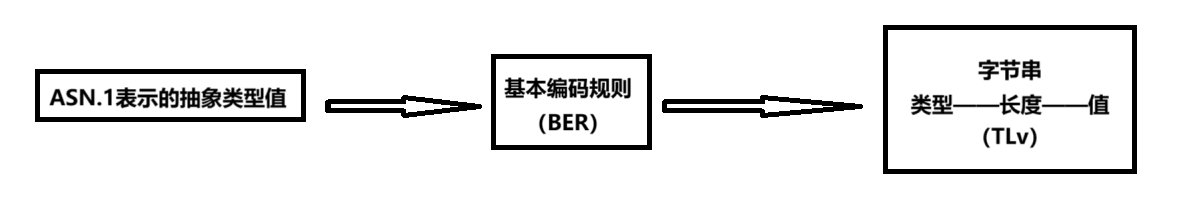

场景:类似图像、文字等码流数据是不需要重复被访问的,因此使用FIFO进行缓存(如果需要被存储,一般不会放在FPGA内部)。此时,FIFO的数据消失性对设计没有影响。但是对于fifo来说,如果时钟频率提高,需要满足建立和保持时间,那么就需要对fifo接口进行缓存,以截断前、后组合逻辑布线延迟和FIFO接口时序之间的相互影响。写时序因为数据和写使能是同步输入给FIFO的,所以没有影响,但是,读时序,读出数据就会延迟3个时钟周期,如下图所示

- FIFO数据消失性:读了数据就没有了,或者理解为指针指向变了,数据虽然有,但是下次读取的时候,数据其实是读不到的。

FIFO数据有两种,定长读取,非定长读取。

**对于数据包来说,会有影响。**对于一般数据来说,无所谓,非空即读就行,但是数据包是按照包进行处理的。

不定长有两种:

- 有数据包长度的字节:表示数据长度的位置在第3个字节,读完发现总字节数为5,此时,读出数据因为是延迟了3个时钟周期的,所以,rd_en没有及时撤销,导致多读数据(FIFO数据消失性),下一次读的数据包,就会不完整。

- 固定字节模式:这种也会发生数据消失,因为不知道数据结尾标志什么时候来,导致多读数据

冗余法:以固定包模式为例

如包数据为 0x11,0x22,…0x33

在数据包尾部增加无效的三个数据(最好不和固定字节模式不同)如在尾部增加后的包如下:

0x11,0x22,…0x33,0x55,0x55,0x55

当读到结束字节0x33时,关闭读使能rd,那么就刚好能规避下一包的数据消失。

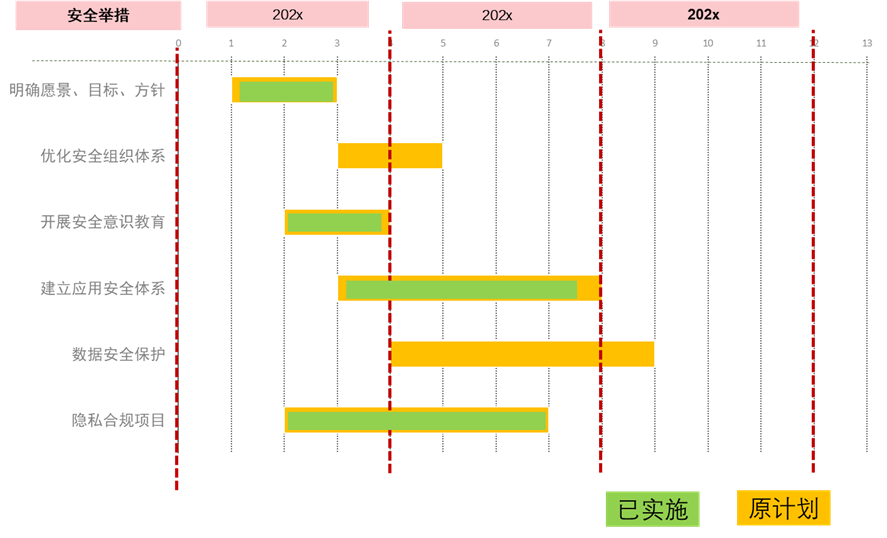

场景2、FIFO数据传输之流控

常见的流控机制分为带内流控和带外流控。带外流控流控比较简单,就是需要一根额外的信号线来表示流控信息,如c2b_ready ,1表示可以发送数据,0表示不可以发送数据.如果取名为fc(flow control),则0表示可以发送数据,1表示停止发送数据。带内流控机制中,流控信息是通过数据通路传输的,没有额外的流控信号线。带内流控在接口模块非常常见,例如是以太MAC的pause帧和PCIe的信用量机制

fifo内的数据量达到或超过cfg_afull_value时,将满信号afull从0跳变成1,即fc信号从0跳变1。上游发送模块感知到fc为1时,则停止发送数据,有可能是1~2周期就停止,有可能是一个整包发送完才停止,根据代码实现才能判断。在fc跳变成1后,fifo需要能够缓存路径上的data以及上游发送模块停止发流之前发出的所有data。这就是fifo的流控机制。

- 在感知到full时,有两种数据其实还在路上,一个是在路上打拍的数据。另一个是,产生full之后,full还有打拍,上游感知到full并停止发wr_en,这之间的数据。

数据data和有效信号vld从模块A产生,经过N拍延时,输入到FIFO,FIFO产生将满信号afull,经过M拍延时反馈到模块A,假设模块A接收到afull=1时,立即停止发送数据。假设FIFO深度为fifo_depth,每拍为一个时钟周期

则,我们考虑以下问题:

- 为了保证FIFO不发生溢出,将满阈值afull_value至少应该设置成多少?

- 为了充分发挥FIFO的性能,FIFO深度depth应该为多少?

FIFO将满阈值如何设置:

1) 当FIFO中的数据为cfg_afull_value时,产生afull=1,

2) Afull=1经过M拍到达模块A,此时FIFO中应该有(cfg_afull_value+M)个数据。

3) Afull=1到达模块A时,模块A立即停止发送数据,此时电路中还存在N拍数据将陆续送到FIFO中,所以最后FIFO中应该为(cfg_afull_value+M+N)个数据,

4) 为了保证数据不会溢出,所以应该满足公式fifo_depth>= cfg_afull_value+M+N,因此,将满阈值应该至多为depth_fifo-(M+N)

FIFO深度depth应该为多少:

若fifo_depth过小,afull有效之后,fifo中存储的数据将很快被下游数据读取,而新的数据又无法及时到达FIFO,因此会造成流水气泡,影响电路性能。

假设M=5 ,N=10,假设fifo_depth=20,则cfg_afull_value=5(这里数据量刚好满足fifo_depth= cfg_afull_value+M+N), 所以在T时刻,fifo中存了5个数据后afull=1会有效,在之后的15个周期内会陆续存入15个数据。假设下游模块B每个周期读取FIFO中的一个数据,因为当FIFO内的数据data_cnt小于5时,afull才会无效(为0),因此在T+15和T+30的之间没写数据(T+15和T+30因为FULL传递需要15个clk),下游电路B只能读5个数据,因此会造成数据断流,影响电路性能。

为保证电路性能,在T+15到T+30这个时间段内应该有15个数据可读,因此cfg_afull_value应该不小于15(M+N)。所以FIFO深度应该不小于2*(M+N)

总结

后续不断更新中…

![[免费]SpringBoot+Vue毕业设计论文管理系统【论文+源码+SQL脚本】](https://i-blog.csdnimg.cn/direct/6e930f3dde3c4f2bb9cf4501c8642e1c.jpeg)