免责声明:本文所提供的信息和内容仅供参考。作者对本文内容的准确性、完整性、及时性或适用性不作任何明示或暗示的保证。在任何情况下,作者不对因使用本文内容而导致的任何直接或间接损失承担责任,包括但不限于数据丢失、业务中断或其他经济损失。

读者在使用本文信息时,应自行验证其准确性和适用性,并对其使用结果负责。本文内容不构成专业技术咨询或建议,具体的技术实现和应用应根据实际情况和需要进行详细分析和验证。

本文所涉及的任何商标、版权或其他知识产权均属于其各自的所有者。若本文中引用了第三方的资料或信息,引用仅为学术交流目的,不构成对第三方内容的认可或保证。

若有任何疑问或需进一步信息,请联系本文作者或相关专业人士。

目录

前言

一、Overview

二、Feature Summary

1.AXI4兼容:符合AXI4接口标准。

2.可选的独立Scatter/Gather DMA支持:

3.可选的直接寄存器模式:

4.数据宽度支持:

5.可选的数据重对齐引擎:

6.可选的AXI控制和状态流:

7.可选的微模式:

三、Register Space

1.Endianess

2.Scatter / Gather Mode Register Address Map

3.Direct Register Mode Register Address Map

4.Register Access Type Description

5.MM2S_DMACR (MM2S DMA Control Register – Offset 00h)

6.MM2S_DMASR (MM2S DMA Status Register – Offset 04h)

7.MM2S_CURDESC (MM2S DMA Current Descriptor Pointer Register - Offset 08h)

8.MM2S_CURDES_MSB (MM2S DMA Current Descriptor Pointer Register -Offset 0Ch)

9.MM2S_TAILDESC (MM2S DMA Tail Descriptor Pointer Register - Offset 10h)

10.MM2S_TAILDESC_MSB (MM2S DMA Tail Descriptor Pointer Register – Offset 14h)

11.MM2S_SA (MM2S DMA Source Address Register – Offset 18h)

12.MM2S_SA_MSB (MM2S DMA Source Address Register – Offset 1Ch)

13.MM2S_LENGTH (MM2S DMA Transfer Length Register — Offset 28h)

14.S2MM_DMACR (S2MM DMA Control Register – Offset 30h)

15.S2MM_DMASR (S2MM DMA Status Register – Offset 34h)

16.S2MM_CURDESC (S2MM DMA Current Descriptor Pointer Register – Offset 38h)

17.S2MM_CURDESC_MSB (S2MM DMA Current Descriptor Pointer Register – Offset 3Ch)

18.S2MM_TAILDESC (S2MM DMA Tail Descriptor Pointer Register – Offset 40h)

19.S2MM_DA (S2MM DMA Destination Address Register – Offset 48h)

20.S2MM_DA_MSB (S2MM DMA Destination Address Register – Offset 4Ch)

21.S2MM_LENGTH (S2MM DMA Buffer Length Register – Offset 58h)

四、Descriptor Management

1. 描述符链的设置与使用

2. DMA传输状态和完成的判断

3. 缓冲区管理与重新分配

4. 尾指针模式的工作方式

5. 描述符管理由软件控制

五、MM2S Descriptor Settings and AXI Control Stream

六、AXI Control Stream

七、S2MM Descriptor Settings and AXI Status Stream

八、AXI Status Stream

九、AXI DMA Multichannel Operation

1.MM2S

1. MM2S 的工作机制

2. 数据包传输的一致性

3. 避免死锁

4. TX 描述符的控制和状态

5. 传输完成的判断

2.S2MM

1. TDEST 信号的作用

2. 描述符链的设置

3. 数据传输的控制

4. 描述符链的管理

5. TDEST, TID, TUSER 信号

3.2-D Transfers

1. 2D 内存访问模式

2. 控制字段:HSIZE, VSIZE, STRIDE

3. 子块传输

4. 对齐要求

5. 每次传输的详细描述

6. 数据读取过程

7. 读取的示例

8. AXI4-Stream 传输

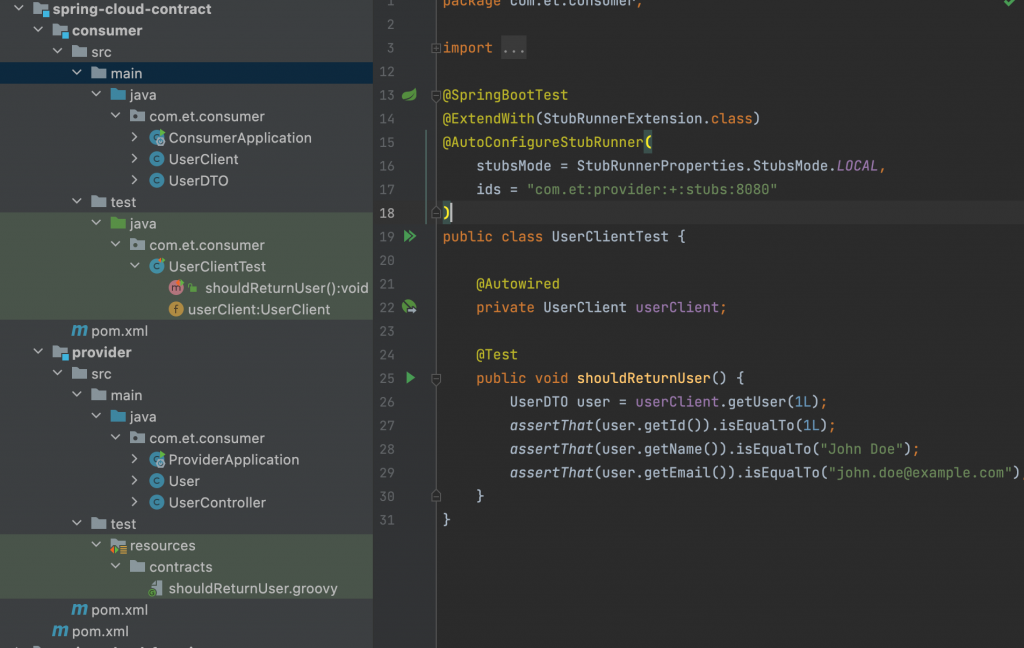

前言

AXI DMA在内存和AXI4-Stream目标外设之间提供高带宽直接内存访问。

一、Overview

AXI直接内存访问(AXI DMA) IP核在AXI4内存映射和AXI4- stream IP接口之间提供高带宽直接内存访问。在基于处理器的系统中,其可选的分散收集功能还可以从中央处理单元(CPU)中卸载数据移动任务。初始化、状态和管理寄存器是通过一个AXI4-Lite从属接口访问的。核心的功能组成如图1-1所示。

-

数据通道:

- MM2S:通过AXI4 Read Master进行数据从系统内存到流目标的传输。

- S2MM:通过AXI4 Write Master进行数据从流目标到系统内存的传输。

-

多通道支持:AXI DMA支持最多16个独立通道,能在MM2S和S2MM路径上以scatter/gather模式进行数据传输。

-

独立操作:MM2S和S2MM通道可以独立工作,允许更灵活的数据管理。

-

功能特性:

- 地址边界保护:在非Micro DMA模式下,提供4 KB的地址边界保护。

- 自动突发映射:能够优化数据传输以利用AXI4-Stream总线的带宽。

- 字节级数据重对齐:可以从任意字节偏移位置开始进行内存读写。

-

控制流与状态流:

- MM2S通道支持AXI控制流,用于将用户应用数据发送到目标IP。

- S2MM通道提供AXI状态流,用于从目标IP接收用户应用数据。

-

可选的Scatter/Gather引擎:该引擎通过AXI4 Scatter Gather Read/Write Master接口从系统内存中获取和更新缓冲区描述符。

二、Feature Summary

1.AXI4兼容:符合AXI4接口标准。

2.可选的独立Scatter/Gather DMA支持:

- 减轻CPU的DMA管理负担。

- 允许从主要数据总线独立获取和更新传输描述符。

- 描述符可以放置在与数据缓冲区分开的任意内存映射位置,例如可以放在块RAM中。

- 提供可选的循环操作模式。

3.可选的直接寄存器模式:

- 如果不使用Scatter/Gather引擎,可以启用该模式,虽然性能较低,但对FPGA资源的占用更少。

- 在此模式下,通过设置源地址(MM2S)或目的地址(S2MM)以及在长度寄存器中指定字节计数来发起传输。

4.数据宽度支持:

- 主AXI4数据宽度支持:32, 64, 128, 256, 512和1,024位。

- 主AXI4-Stream数据宽度支持:8, 16, 32, 64, 128, 256, 512和1,024位。

5.可选的数据重对齐引擎:

- 支持最多512位的流数据宽度。

- 允许在主内存映射和流数据路径上以字节(8位)级别进行数据重对齐。

6.可选的AXI控制和状态流:

- 提供MM2S通道的控制流和S2MM通道的状态流,以减少高带宽数据路径上的低带宽控制和状态流量。

7.可选的微模式:

- AXI DMA可以配置为交付低占用、低性能的IP,以处理小数据包。

三、Register Space

1.Endianess

所有寄存器都是Little Endian格式,如图2-1所示。

2.Scatter / Gather Mode Register Address Map

3.Direct Register Mode Register Address Map

4.Register Access Type Description

5.MM2S_DMACR (MM2S DMA Control Register – Offset 00h)

6.MM2S_DMASR (MM2S DMA Status Register – Offset 04h)

7.MM2S_CURDESC (MM2S DMA Current Descriptor Pointer Register - Offset

08h)

8.MM2S_CURDES_MSB (MM2S DMA Current Descriptor Pointer Register -

Offset 0Ch)

注:这个寄存器为流DMA分散收集描述符管理的内存映射提供当前描述符指针的上32位。这只适用于地址空间大于32位的情况。

9.MM2S_TAILDESC (MM2S DMA Tail Descriptor Pointer Register - Offset 10h)

10.MM2S_TAILDESC_MSB (MM2S DMA Tail Descriptor Pointer Register – Offset

14h)

11.MM2S_SA (MM2S DMA Source Address Register – Offset 18h)

这个寄存器为从内存映射到流DMA传输读取系统内存提供源地址。

12.MM2S_SA_MSB (MM2S DMA Source Address Register – Offset 1Ch)

这个寄存器提供源地址的上32位,用于读取系统内存,用于内存映射到流DMA传输。只有当DMA配置的地址空间大于32时才适用。

13.MM2S_LENGTH (MM2S DMA Transfer Length Register — Offset 28h)

这个寄存器提供要从系统内存中读取并传输到MM2S AXI4-Stream的字节数。

14.S2MM_DMACR (S2MM DMA Control Register – Offset 30h)

15.S2MM_DMASR (S2MM DMA Status Register – Offset 34h)

16.S2MM_CURDESC (S2MM DMA Current Descriptor Pointer Register – Offset

38h)

这个寄存器为流到内存映射DMA分散收集描述符管理提供当前描述符指针。

17.S2MM_CURDESC_MSB (S2MM DMA Current Descriptor Pointer Register –

Offset 3Ch)

这个寄存器为流到内存映射DMA分散收集描述符管理提供当前描述符指针的上32位。只有在为大于32位的地址空间配置DMA时才使用。

18.S2MM_TAILDESC (S2MM DMA Tail Descriptor Pointer Register – Offset 40h)

这个寄存器为流到内存映射DMA分散收集描述符管理提供尾部描述符指针。

19.S2MM_DA (S2MM DMA Destination Address Register – Offset 48h)

这个寄存器提供目标地址,用于写入系统内存,以便从流到内存映射到DMA传输。

20.S2MM_DA_MSB (S2MM DMA Destination Address Register – Offset 4Ch)

这个寄存器提供了目标地址的上32位,用于写入系统内存,以便从流到内存映射到DMA传输。仅当为大于32的地址空间配置DMA时使用。

21.S2MM_LENGTH (S2MM DMA Buffer Length Register – Offset 58h)

该寄存器以字节为单位提供缓冲区的长度,以便将数据从流写入内存映射DMA传输。

四、Descriptor Management

1. 描述符链的设置与使用

- 在开始DMA操作之前,软件应用程序必须先设置一个描述符链(descriptor chain)。描述符链是一个数据结构,其中包含了关于每个DMA传输的元数据(例如数据缓冲区地址、数据长度、传输状态等)。

- 当AXI DMA开始处理描述符时,它会依次获取、处理并更新每个描述符。硬件(AXI DMA)通过分析描述符,知道该传输的状态,从而能够管理DMA操作和数据传输。

2. DMA传输状态和完成的判断

- 软件可以通过读取描述符的状态来判断DMA传输的进度和完成情况。软件会根据描述符的完成位(Complete bit)来判断哪些描述符已经处理完,哪些还没有。

- 如果DMA传输在接收(S2MM,Stream to Memory-Mapped)通道上完成,软件可以通过描述符获取接收到的数据和其他信息。

3. 缓冲区管理与重新分配

- 软件应用程序处理每个与已完成的描述符关联的缓冲区数据,并重新分配描述符,以供AXI DMA继续使用。

- 为了避免软件和硬件之间相互干扰,采用了尾指针模式(Tail Pointer Mode)。这个尾指针是由软件初始化的,它指向描述符链的末尾,这成为硬件的“暂停点”。

4. 尾指针模式的工作方式

- 当AXI DMA硬件开始运行时,它会按照描述符链的顺序获取和处理每个描述符,直到遇到尾指针为止。这个尾指针标志着硬件处理的结束,硬件会在此暂停。

- 这时,软件可以处理和重新分配那些完成位(Complete bit)被设置为1的描述符。这些描述符代表着已经完成的数据传输,软件可以更新这些描述符并为硬件提供新的描述符。

- 软件通过写入TAILDESC寄存器来启动或继续硬件的描述符处理。当硬件在尾指针处暂停时,写入TAILDESC寄存器将使硬件继续处理描述符。如果硬件没有暂停在尾指针位置,写入TAILDESC寄存器对硬件没有影响,硬件会继续处理描述符,直到达到新的尾指针位置。

5. 描述符管理由软件控制

- 需要特别注意的是,AXI DMA硬件本身并不管理描述符。描述符的管理、更新和重新分配完全由软件负责。

五、MM2S Descriptor Settings and AXI Control Stream

-

SOF=1 和 EOF=1:

SOF=1表示这是一个数据包的开始,意味着这个描述符代表数据包的起始点。EOF=1表示这是数据包的结束,意味着这个描述符是数据包的最后部分。

-

AXI Control Stream:

- 这指的是通过AXI接口传输的数据流。AXI DMA引擎通过AXI控制流和用户应用程序进行交互。

-

描述符的作用:

- 描述符中的SOF=1标志着数据包的开始,并且会重置“DRE”(可能是指“Data Read Enable”或类似的控制信号)以确保MM2S(Memory to Stream)方向上的数据读取状态。

- 如果启用了Status/Control Stream,与这个描述符相关的用户应用字段也会出现在AXI控制流中。

-

描述符中的SOF=1和EOF=1之间的字段:

- 从一个SOF=1的描述符开始,到EOF=1的描述符结束之间的所有用户应用字段将被AXI DMA引擎忽略。这些字段不会被DMA引擎处理,只会作为标识符存在。

-

Status/Control Stream是否启用:

- 如果启用了Status/Control Stream,用户应用字段会通过AXI控制流传输。

- 如果Status/Control Stream没有启用,SG Fetch Engine(传输引擎)不会抓取(fetch)这些用户应用字段。

六、AXI Control Stream

七、S2MM Descriptor Settings and AXI Status Stream

描述符RXSOF/RXEOF设置和AXI状态流之间的关系如图2-38所示。RXSOF=1的描述符描述包含接收包的第一部分的缓冲区。RXEOF=1的描述符描述了包含接收包最后一部分的缓冲区。

为了正确操作,软件必须指定足够的缓冲区空间(描述符链中每个描述符的缓冲区长度的总和)大于或等于接收到的最大大小的数据包。

每个接收缓冲区有一个关联的描述符(descriptor),这个描述符包含一个字段 Transferred Bytes,用来存储实际接收到并存储的数据字节数。这表示每个数据缓冲区的描述符会更新,记录接收到的数据字节数;软件可以通过遍历描述符链来计算接收到的总字节数。RXSOF(接收起始帧)和 RXEOF(接收结束帧)表示描述符链的起始和结束位置。软件通过遍历这些描述符,并累加每个描述符中的 Transferred Bytes 字段来获得接收到的总字节数;对于某些应用程序,可能会在状态流中提供总长度(比如数据流的总字节数)。在这种情况下,描述符中的某个用户定义的位置会存储这个总长度值,且这个描述符的 RXEOF 字段会被设置为 1,表示它是描述符链的最后一个。

八、AXI Status Stream

-

AXI 状态流:这个状态流用于传输目标设备的状态信息到用户应用程序的数据字段。数据通过 Scatter Gather descriptor 中的字段传递。Scatter Gather 是一种内存描述符机制,用于处理不连续的数据传输,允许数据包被分散到不同的内存位置。

-

与 S2MM 数据流关联:S2MM(Stream-to-Memory-Mapped)数据流是从外部设备(比如传感器、DMA 控制器等)到内存的传输通道。状态数据与 S2MM 主数据流(primary data stream)关联。也就是说,状态流提供的信息描述了 S2MM 数据流的状态。

-

状态包更新应用程序字段:在图 2-39(文档中的某个图)中,状态包会更新 Scatter Gather descriptor 中的 "应用程序字段"(app fields)。特别是当 RXEOF = 1(表示接收数据流的结束)时,状态包描述了该数据包的最后状态。

-

状态流的位置:通常,状态流应该在 S2MM 数据流的开始部分传输。状态流提供的信息会提前让应用程序知道数据流的状态。

-

Use RxLength In Status Stream 选项:如果 Use RxLength In Status Stream 被禁用,那么状态流可以在 S2MM 数据流的任何时刻传输。这表示状态流并不要求一定在开始时发送,而是可以在整个数据传输过程中随时传送。

-

EOF 更新:只有在整个状态流接收完之后,才会更新 End of Frame (EOF) 描述符(Buffer Descriptor, BD)。EOF 是一个标志,用来指示一个帧数据的结束。更新的条件是整个状态流完成接收。

九、AXI DMA Multichannel Operation

1.MM2S

1. MM2S 的工作机制

- MM2S 是将数据从内存传输到流接口(通常是流输出,例如外设或总线)的过程,类似于正常的 AXI DMA 操作。

- 当软件编程 MM2S_CURDESC 和 MM2S_TAILDESC 时,AXI DMA 会获取一系列的描述符,并逐一处理,直到达到尾描述符。

- MM2S_CURDESC 是当前处理的描述符,MM2S_TAILDESC 是链的末尾描述符,它们标识了 DMA 将要处理的一系列数据包。

2. 数据包传输的一致性

- 在 AXI DMA 中,TDEST、TID 和 TUSER 字段应该在整个数据包的传输过程中保持不变。

- TDEST:目标 ID

- TID:传输标识符

- TUSER:用户定义的标志

- 也就是说,对于通过一个逻辑通道(由 TDEST、TID、TUSER 定义的)传输的数据包,它必须在开始传输后完成整个数据包的传输才能继续处理下一个包。

- 如果存在多个通道的数据传输,它们可以是交错的,但一旦启动,数据传输必须运行至完成,之后才能进行下一个数据包的传输。

3. 避免死锁

- 由于每个数据包传输必须完成,避免了交叉执行的问题,但是这也带来了死锁的风险。因此,需要确保数据包传输的顺序和状态保持一致。

- AXI DMA 本身不会对 TDEST、TID、TUSER 字段不一致的情况产生错误信号。也就是说,如果这些字段没有遵循上述的假设,系统不会主动报告错误,而是由软件来维护一致性,避免死锁。

4. TX 描述符的控制和状态

- TX 描述符 在多通道模式下包含控制和状态字段。

- 在数据传输完成后,TX 描述符 不会自动更新传输的字节数。换句话说,描述符本身不会告诉你传输了多少字节。这需要通过其他方式(如寄存器)来确认。

- 错误信息会被捕获并记录在寄存器中,同时记录失败描述符的当前指针。这帮助诊断数据传输过程中出现的错误。

5. 传输完成的判断

- 可以通过轮询 MM2S_DMASR 寄存器中的 IDLE 位,或者通过启用中断(在 MM2S_DMACR 中配置)来确认传输链是否已完成。

- MM2S_DMASR:DMA 状态寄存器,用于表示 DMA 的当前状态。

- MM2S_DMACR:DMA 控制寄存器,用于控制 DMA 的启动、停止等操作。

2.S2MM

1. TDEST 信号的作用

- TDEST 是流数据传输中的一个信号,它由输入流采样得到。TDEST 值用于 DMA 控制器 来读取对应的 S2MM_CURDESC 和 S2MM_TAILDESC 描述符,并将它们传递给 Scatter Gather (SG) 模块。

- S2MM_CURDESC 是当前处理的描述符,S2MM_TAILDESC 是描述符链的尾部描述符。

- TDEST 值确定了应该使用哪个描述符链(也就是说,选择哪个描述符链进行数据传输)。

2. 描述符链的设置

- 在数据包到达 S2MM 通道 之前,Buffer Descriptor 链应该已经设置完毕。也就是说,描述符链必须在数据包到来之前完成配置。

- Current Descriptor 和 Tail Descriptor 寄存器需要在数据包到达之前就已经编程好。

- 这保证了在数据流到达时,AXI DMA 已经知道如何处理数据包,避免了延迟。

3. 数据传输的控制

- AXI DMA 在接收到数据流之前,会通过 deasserting tready(即取消准备信号)来保持流数据不被读取,直到相应的描述符被提取并准备好。只有当描述符链中的当前描述符被取出并准备好时,数据传输才会开始。

- 数据开始传输后,AXI DMA 将从 Buffer Address 开始写入数据,直到接收到流端的 tlast 信号(表示数据包结束)。

4. 描述符链的管理

- 对于特定的通道,当数据传输完成后,当前描述符寄存器 会加载下一个描述符的地址,以确保下一数据包能够继续被正确地服务。这是为了确保数据包的顺序和正确性。

- Tail Descriptor 的管理非常重要。需要确保在描述符链的尾部正确设置 Tail Descriptor,否则可能会导致 Current Descriptor 跳跃,导致传输过程错误。

5. TDEST, TID, TUSER 信号

- TDEST、TID 和 TUSER 信号会从流数据中捕获,并在 AXI DMA 中内部存储。

- 这些信号的值在数据包的传输过程中不会发生变化,即它们在整个数据包传输过程中应该是保持一致的。

- 当数据传输完成后,这些值会在每个描述符中进行更新,连同其他的状态位一起更新。

3.2-D Transfers

1. 2D 内存访问模式

- AXI DMA 支持 2D 内存访问模式,这意味着数据可以按照二维数组的方式组织,并通过 AXI4-Stream 通道高效传输。

- 这种方式特别适用于需要按照行(row)和列(column)结构访问和传输的应用场景,比如图像处理、视频流等。

2. 控制字段:HSIZE, VSIZE, STRIDE

- 数据传输的 2D 访问模式由描述符中的三个字段来控制:

- HSIZE:每行传输的字节数,指定从一个子块的起始地址到下一个子块(或行)的字节数。这就是每一行的宽度。

- VSIZE:指定列的大小,即每次传输的数据块在垂直方向上的尺寸(通常表示为行数)。

- STRIDE:描述从一个子块(或行)到下一个子块(或行)之间的地址偏移量。每次读取或写入后,传输的起始地址会增加 STRIDE 个字节。

3. 子块传输

- 对于 2D 传输,AXI DMA 会根据 HSIZE、VSIZE 和 STRIDE 字段来划分数据块进行传输。具体来说:

- 每次传输会有 VSIZE 次传输,每次传输的数据块大小为 HSIZE 字节。

- 每次传输的起始地址会根据 STRIDE 字段的值发生变化,即每个子块的起始地址相对于上一个子块的地址偏移了 STRIDE 个字节。

- 初始的起始地址是传输包的 BaseAddr(即数据包的基础地址)。

4. 对齐要求

- 为了确保数据传输的稳定性,HSIZE、VSIZE 和 STRIDE 必须是字节对齐的。如果这些字段的值没有对齐,可能会导致不可预期的行为,例如数据丢失、传输错误等。

5. 每次传输的详细描述

- 每次读取(MM2S)或写入(S2MM)操作会进行 VSIZE 次数据传输,每次传输的数据量为 HSIZE 字节。

- 这意味着,对于每一行数据,AXI DMA 会按照 HSIZE 字节的大小将数据分批传输,直到这一行的所有数据都被传输完毕。

- 然后,起始地址会根据 STRIDE 的值进行偏移,转到下一行数据继续传输,直到整个二维数组的传输完成。

6. 数据读取过程

- 读取操作从 Buffer Address 开始,按照 VSIZE 次读取,每次读取的数据大小为 HSIZE 字节。

- Buffer Address 是数据传输的起始地址。

- VSIZE 是数据传输的垂直维度,表示需要读取的行数。

- HSIZE 是每次读取的数据量(即每一行的字节数)。

- Stride 是从一行到下一行的地址偏移量,控制读取过程中行与行之间的间隔。

7. 读取的示例

假设:

- Buffer Address = 08:缓冲区的起始地址是 08。

- VSIZE = 06:需要读取 6 行数据。

- HSIZE = 256 bytes:每行的数据量为 256 字节。

- Stride = 512 bytes:每行之间的偏移量为 512 字节。

根据这个配置,数据读取的顺序如下:

- 第 1 行:从 Buffer Address = 08 开始,读取 256 字节。

- 第 2 行:开始地址为 Buffer Address + Stride = 08 + 512 = 520,继续读取 256 字节。

- 第 3 行:开始地址为 520 + 512 = 1,032,继续读取 256 字节。

- 第 4 行:开始地址为 1,032 + 512 = 1,544,继续读取 256 字节。

- 以此类推,直到读取完 VSIZE 行(本例中为 6 行)。

8. AXI4-Stream 传输

- 上述读取的所有数据将在 AXI4-Stream 接口的 m_axis_mm2s 上作为一个连续的包进行传输。

- tlast 信号在最后一个数据传输(即最后一个数据拍打)时被断言,表示传输的结束。

![[Docker#8] 容器配置 | Mysql | Redis | C++ | 资源控制 | 命令对比](https://img-blog.csdnimg.cn/img_convert/e355315bf2279c1428ceebd01a1edf6f.png)

![[产品管理-76]:延续是创新与颠覆式创新的比较](https://i-blog.csdnimg.cn/direct/5bc61d739e2b44a2a070b19b46bc71e1.png)