本文摘录至微信公众号 搞搞芯意思

-

为何用sharebus?

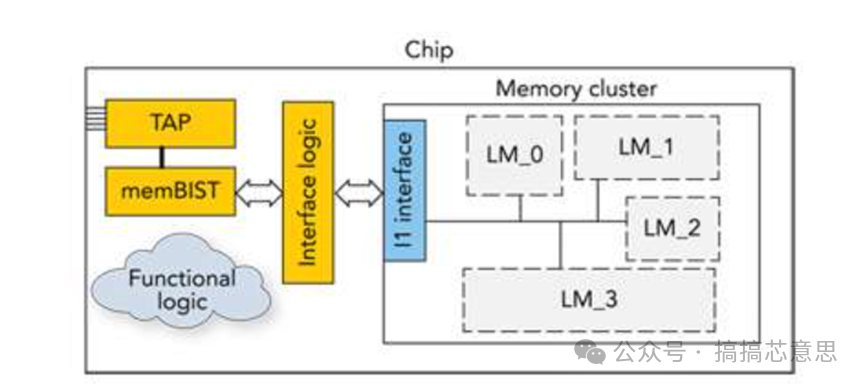

CPU/NPU/GPU等关键模块对性能要求很高,对功耗、时序、面积敏感,是整个芯片设计瓶颈。常规mbist设计插入的额外电路会对function时序收敛带来负面影响,而且会造成布线拥堵,给芯片性能和pd设计带来挑战。sharebus方案将controller放在关键模块外面,尽可能插入在非关键路径,通过interface复用功能bus总线实现对memory读写,用极其少的mbist电路实现对整个模块的测试。保障测试质量,减少走线资源,同时降低对function时序的影响。

2. 何谓sharebus?

下图是一种sharebus设计示意图,memory cluster是关键模块,内部时序紧张,而interface的外侧路径则为非关键路径,时序较为放松,margin比较大。在interface之外非关键路径插入mbist controller和tap控制器,复用cluster内部总线对memory进行读写测试,这种设计对整个系统性能影响较小,降低布线难度。

3. sharebus group规划原则

-

物理位置近放一个group;

-

时钟频点相同放一个group;

-

不稳定memory放一个groupÿ