一、实验目的

l.验证移位寄存器的逻辑功能;

2.掌握集成电路4位双向移位寄存器的使用方法;

3.学会应用移位寄存器实现数据的串行、并行转换和构成环形计数器。

二、实验原理

l.移位寄存器的特点

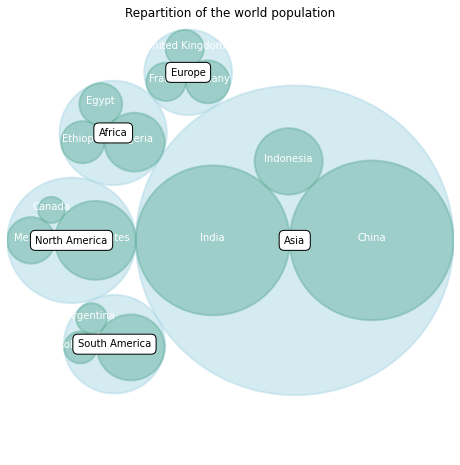

寄存器中所存的数据在CP脉冲作用下能依次左移或右移。有些集成移位寄存器同时设有左移或右移控制端,可根据左移或右移信号实现双向移位的要求。根据移位寄存器存取信息方式的不同分为串入串出、串入并出、并入串出、并入并出这4种形式。

本实验选用的4位双向通用移位寄存器CD40194或74LS194,两者功能和引脚相同,可互换使用。逻辑符号及引脚排列如图47-1所示。

其中,D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端:DIR为右移串行输入端,DIL为左移串行输入端;S1、S0为操作模式控制端;Rd 为异步(亦称为无条件)清零端;CP为时钟脉冲输入端。

CD40194有5种不同操作模式:即数据在D3、D2、D1、D0端并行送入寄存、右移(数据由Q0→Q3移动)、左移(数据由Q3→Q0移动)、保持及清零。

S1、S0和¯Rd端的控制作用如表47-1所示。

2.移位寄存器的用途

移位寄存器除了可以作为寄存器外,通过适当的连接,还可以成为移位寄存器型计数器、顺序脉冲发生器、串行累加器等,还可用作数据转换,即把串行数据转换为并行数据、并行数据转换为串行数据等。本实验研究移位寄存器如何成为环形计数器和数据的串、并行转换。其他用途自行参考有关资料。

(1)环形计数器

环形计数器如图47-2所示,是把移位寄存器的输出反馈到它的串行输入端,利用循环移位实现计数。把输出端Q3与右移输入端DIR相连,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲CP的作用下,Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表47-2所示。显然它是利用4个有效状态表示计数结果,这种类型的计数器通常称为环形计数器。图47-2所示电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。如果将输出端Q0与左移串行输入端DIL相连接,即可左移循环移位。

(2)实现数据串行、并行输入输出相互转换

①串行输入/并行输出转换电路

串行输入/并行输出转换是指串行输入的数据,经转换电路后并行输出。图47-3所示是由CD40194(74LS194)4位双向移位寄存器组成的7位串行输入/并行输出转换电路。

电路中S0端接高电平l,S1受Q7控制,两片寄存器连接成串行输入右移工作模式。Q7是转换结束标志。当Q7=l时。S1为0,使之成为S1S0=0l的串入右移工作方式,当Q7=0时,S1=1,有S1S0=11,则串行送数结束,标志着串行输入的数据已转换成并行输出了。其中所使用的非门可用74LS04(见实验43)或CD4069(见实验62)。

串入/并出转换具体过程如下: 转换前,¯Rd加低电平,使1、2两片寄存器的内容清零,此时S1S0=11,寄存器执行并行输入工作方式。当第一个CP脉冲到来后,寄存器的输出状态Q0~Q7为01111111,与此同时S1S0变为01,转换电路变为执行串入右移工作方式,串行输入数据由1片的DIR端加入。随着CP脉冲的加入,输出状态的变化可列成表47-3所示。

由表47-3可知,右移操作七次后,Q7变为0,S1S0又变为11,说明串行输入结束。这时,串行输入的数码已转换成了并行输出。

当再来一个CP脉冲时,电路又重新执行一次并行输入,为第二组串行数码转换作好了准备。

②并行输入/串行输出转换器

并行输入/串行输出转换器是指并行输入的数码经转换电路之后,换成串行输出。

图47-4所示是用两片CD40194(74LS194)组成的7位并行输入/串行输出转换电路,它比图47-3所示电路多了两个与非门G1和G2,电路工作方式同样为右移。

寄存器清零后,加一个转换启动信号(负脉冲或低电平)。此时,由于方式控制S1S0为11,转换电路执行并行输入操作。当第一个CP脉冲到来后,Q0Q1Q2Q3Q4Q5Q6Q7的状态为0DlD2D3D4D5D6D7,并行输入数码存入寄存器。从而使得G1输出为1,G2输出为0,结果S1S0变为01,转换电路随着CP脉冲的加入,开始执行右移串行输出,随着CP脉冲的依次加入,输出状态依次右移,待右移操作7次后,Q0~Q6的状态都为高电平1,与非门G1输出为低电平,G2门输出为高电平,S1S0又变为11,表示并/串行转换结束,且为第二次并行输入创造了条件。转换过程如表47-4所示。

图47-4中的G1为8输入与非门,可使用CD4068或74LS30,相关资料见本实验附录。

中规模集成移位寄存器,其位数往往以4位居多,

当需要的位数多于4位时,可把几片移位寄存器用级连的方法来扩展位数。

三、实验设备与器材

l.+5V直流电源

2.单次脉冲源

3.逻辑电平开关

4、逻辑电平显示器

5.CD40194×2(或74LS194)、CD4011(74LS00)(见实验37/38)、CD4068(74LS30)(见本实验附录)

四、实验步骤、过程和记录(数据、图表、计算等)

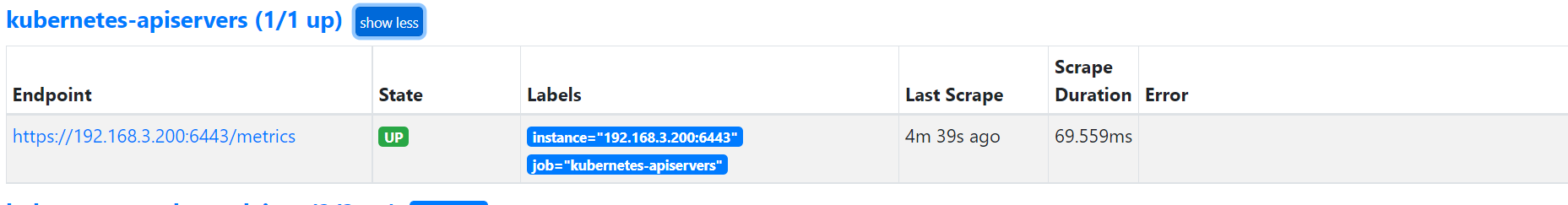

1.测试CD40194(或74LS194)的逻辑功能

按图47-5所示接线,¯Rd、S1、S0、DIL、DIR、D0、D1、D2、D3分别接至逻辑开关;Q0、Q1、Q2、Q3分别接逻辑电平显示器。CP端接单次脉冲源。按表47-5所规定的输入状态,逐项进行测试。

(1)清零:置¯Rd=0,其它输入为任意态,这时寄存器输出Q0Q1Q2Q3应均为0。清零后,置¯Rd =l。

(2)置数:令¯Rd=S1=S0=l,送入任意4位二进制数,如D0D1D2D3=1101,加单次脉冲至CP端,观察CP=0、CP由0→1、CP由1→0三种情况下寄存器输出状态的变化,观察寄存器输出状态变化是否发生在CP脉冲的上升沿。

(3)右移:清零后,令¯Rd =1、S1S0=01,由右移输入端DIR送入二进制数码,如0100,由CP端连续加4个脉冲,观察输出情况并记录。

(4)左移:先清0或预置,再令¯Rd =1,S1=1,S0=0。由左移输入端DIL送入二进制数码如1111,连续加4个CP脉冲,观察输出端情况并记录过程。

(5)保持:寄存器预置任意4位二进制数码,如1101,令¯Rd=1,S1=S0=0,加CP脉冲,观察寄存器输出状态并记录。

2.环形计数器

自拟实验线路,用并行置数法预置寄存器为某数据(如0100),然后进行右移循环,观察寄存器输出端状态的变化,再进行左移循环,并把过程记入表47-6中。

3.实现数据的串、并行转换

(1)串行输入、并行输出

把两块CD40194接成如图47-3所示,就成为右移串入、并出寄存器,实验时串入数据自定。自行改接线路用左移串入方式实现并行输出,自拟表格并记录过程。

D1=1,D2=0,D3=1,D4=0,D5=1,D6=0,D7=1

![适合初学者的[JAVA]: 基础面试题](https://i-blog.csdnimg.cn/direct/b431de8f7cc547e4a64ae674ea2c0826.png)