系列文章目录

1.元件基础

2.电路设计

3.PCB设计

4.元件焊接

5.板子调试

6.程序设计

7.算法学习

8.编写exe

9.检测标准

10.项目举例

11.职业规划

文章目录

- 一、硬件查看是否连接错误

- 二、软件查看芯片包,更新到最新版本

- 三、Debug下载模式选择

- 四、芯片大小选择

- 后记

keil5程序编译没错误魔术棒可以识别芯片但是就是下载报错

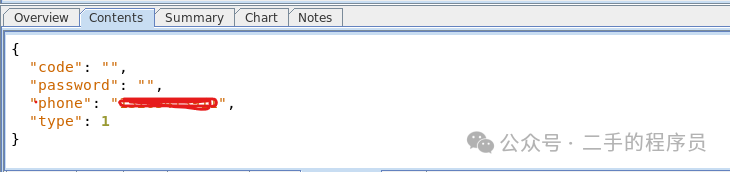

一、硬件查看是否连接错误

如下图就是错误的

二、软件查看芯片包,更新到最新版本

更新软件包

三、Debug下载模式选择

我用的是st-link,选择SWD(大家选择自己的下载),Debug菜单中,Reset菜单选项(Autodetect/HWreset/sysresetReq/Vectreset)默认是AutoDetect,改成SysResetReq即可。

细心的工程师会发现在单片机的用户手册中没有关于Cortex-M0+ SYSRESETREQ 软件复位是如何来实现的相关介绍,这是为什么呢?因为Cortex-M0+ SYSRESETREQ 软件复位是ARM内核中自带的功能,不是厂家来定义的,大多数的用户手册介绍的内容都是厂家自己搭配的外设模块的使用。关于内核的介绍大家可以ARM的官网下载相关的文档,也可以看也《ARM+Cortex-M0权威指南》这本书。在《ARM+Cortex-M0权威指南》中可以找到关于 SYSRESETREQ软件复位的介绍如下:

四、芯片大小选择

SWD模式下,Debug菜单中,主要是芯片大小选错。Flash->Configure Falsh Tools配置窗口,切换到“Utilities"页,按“Setting"按钮进入“Flash download setup"配置窗口,在“Flash download setup"配置窗口点击“Add”按钮,在“Add Flash Programming Algorlthm"窗口,根据你实际使用的芯片选择,若是STM32F103VBT6,应先择"STM32L1xx Med+ 256kB Flash"。

后记

ARMCortex-M3采用哈佛结构,并选择了适合于微控制器应用的三级流水线,但增加了分支预测功能。

现代处理器大多采用指令预取和流水线技术,以提高处理器的指令执行速度。流水线处理器在正常执行指令时,如果碰到分支(跳转)指令,由于指令执行的顺序可能会发生变化,指令预取队列和流水线中的部分指令就可能作废,而需要从新的地址重新取指、执行,这样就会使流水线“断流”,处理器性能因此而受到影响。特别是现代C语言程序,经编译器优化生成的目标代码中,分支指令所占的比例可达10-20%,对流水线处理器的影响会的更大。为此,现代高性能流水线处理器中一般都加入了分支预测部件,就是在处理器从存储器预取指令时,当遇到分支(跳转)指令时,能自动预测跳转是否会发生,再从预测的方向进行取指,从而提供给流水线连续的指令流,流水线就可以不断地执行有效指令,保证了其性能的发挥。

ARMCortex-M3内核的预取部件具有分支预测功能,可以预取分支目标地址的指令,使分支延迟减少到一个时钟周期。

针对业界对ARM处理器中断响应的问题,Cortex-M3首次在内核上集成了嵌套向量中断控制器(NVIC)。Cortex-M3的中断延迟只有12个时钟周期(ARM7需要24-42个周期);Cortex-M3还使用尾链技术,使得背靠背(back-to-back)中断的响应只需要6个时钟周期(ARM7需要大于30个周期)。Cortex-M3采用了基于栈的异常模式,使得芯片初始化的封装更为简单。

Cortex-M3加入了类似于8位处理器的内核低功耗模式,支持3种功耗管理模式:通过一条指令立即睡眠;异常/中断退出时睡眠;深度睡眠。使整个芯片的功耗控制更为有效。