1 PWM 简介

2 F28335的ePWM介绍

2.1 时基模块TB

(1)时基模块的功能

(2)时基模块的关键信号和寄存器

给出时基模块内部结构图来了解里面的关键信号和寄存器,时基模块内部结构图如下所示:

(3)计算ePWM 周期和频率

1、向上-向下计数模式(先递增后递减)

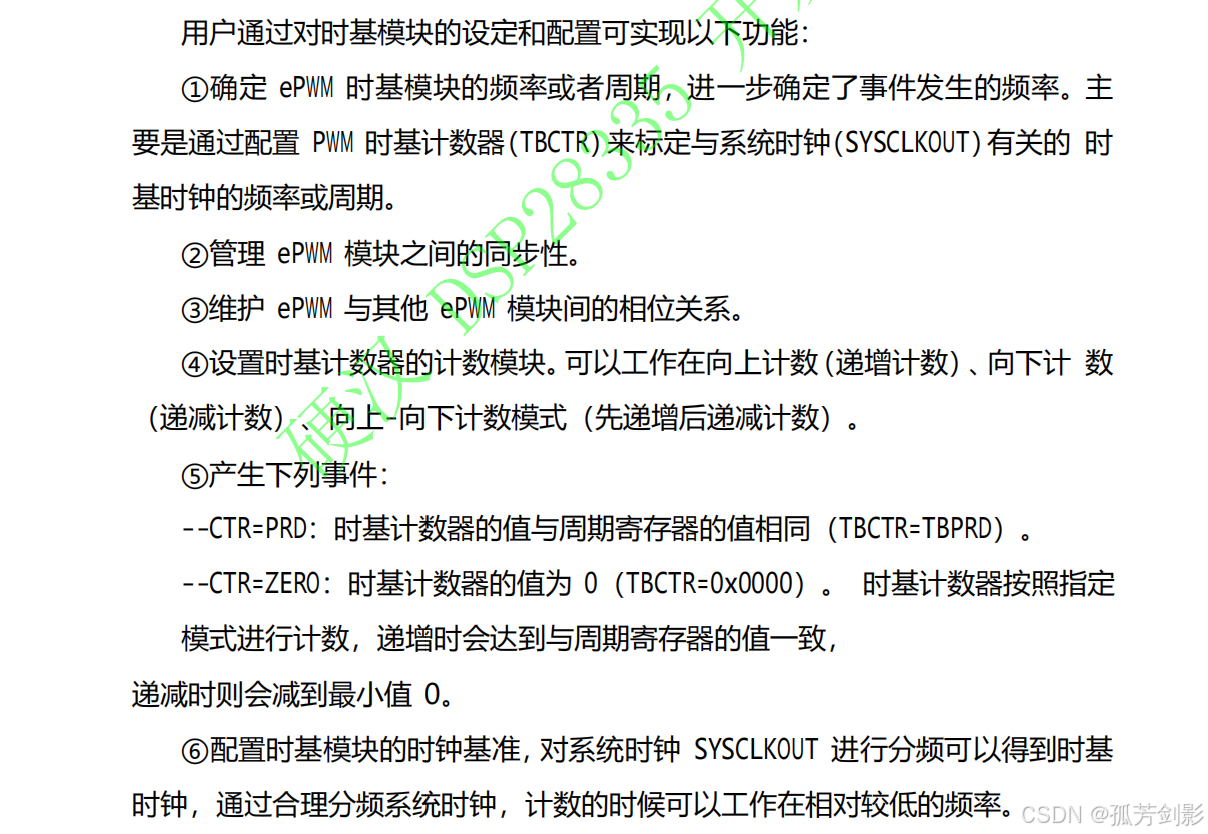

2、向上计数模式(递增)

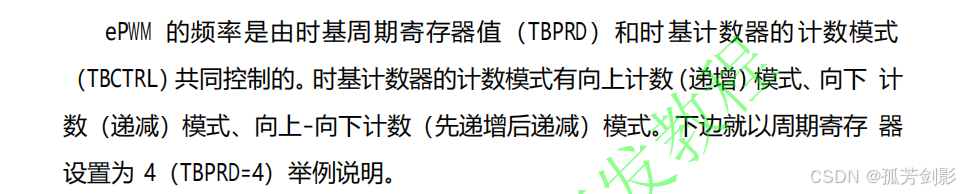

3、向下计数模式(递减)

(4)影子寄存器

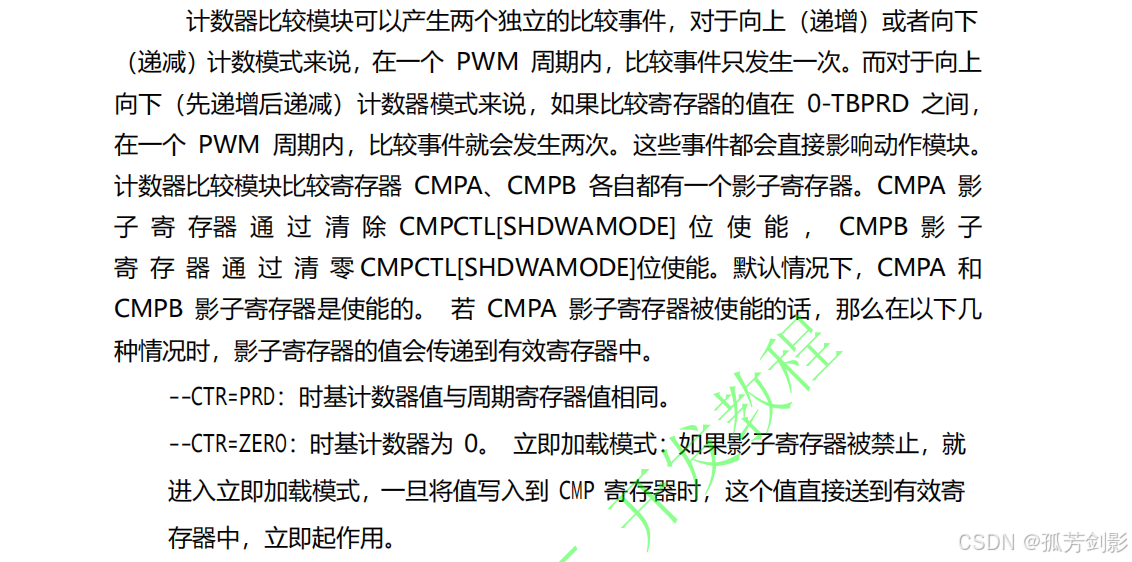

2.2 计数比较模块CC

(1)计数器比较模块 CC 的功能

(2)计数器比较模块 CC 的关键信号与寄存器

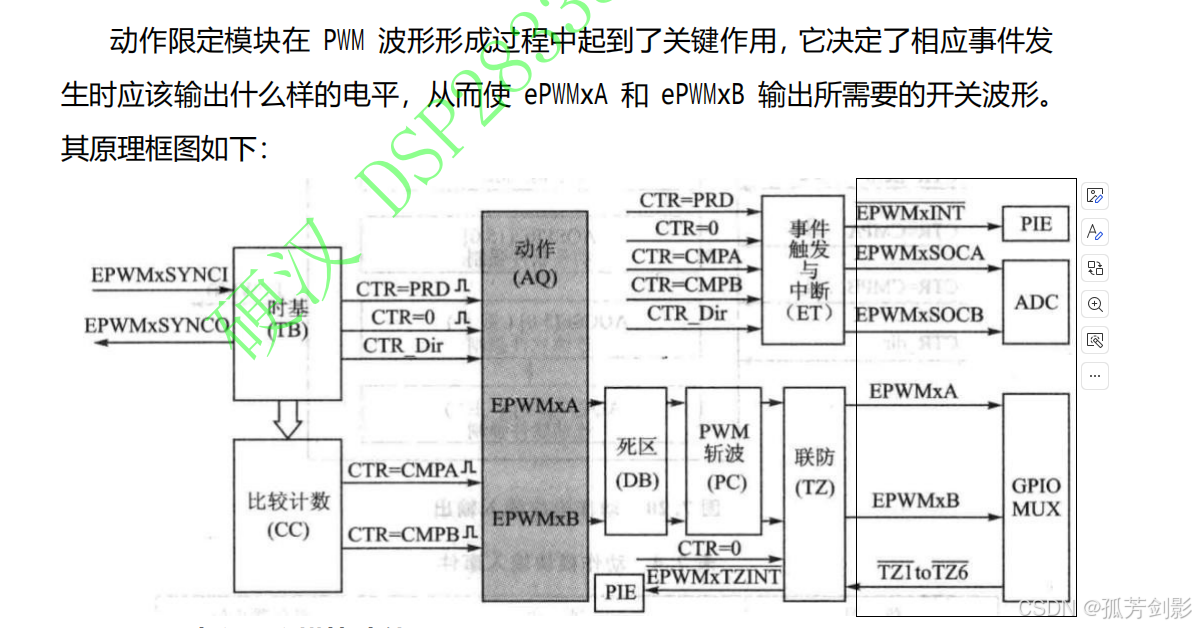

2.3 动作限定模块AQ

(1)动作限定模块功能

(2)动作限定模块关键信号与寄存器

(3) 动作限定模块事件优先级

最高同样是软件强制,最低是计数器等于周期寄存器的值匹配事件。

(4)动作限定模块一般配置条件下的输出波形

注意:

①PWM 周期=(TBPRD+1)*T(TBCLK)

②CMPA 决定 ePWMxA 的占空比,CMPB 决定 ePWMxB 占空比。

下面是该输出波形相关配置代码:

EPwm6Regs.TBPRD = tbprd;//设定 PWM 周期为 tbprd+1 个 TBCLK 时钟周期

EPwm6Regs.CMPA.half.CMPA = 350;//比较器 A 的值为 350

EPwm6Regs.CMPB = 200;//比较器 B 的值为 200

EPwm6Regs.TBPHS.half.TBPHS = 0;//相位寄存器清零

EPwm6Regs.TBCTR = 0x0000;//时基计数器清零

EPwm6Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;//设定为增计数模式

EPwm6Regs.TBCTL.bit.PHSEN = TB_DISABLE;//禁止相位控制

EPwm6Regs.TBCTL.bit.PRDLD = TB_SHADOW;//TBPRD 寄存器采用影子寄存器模式

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE;//禁止同步信号

EPwm6Regs.TBCTL.bit.HSPCLKDIV=TB_DIV1;//设定 TBCLK=SYSCLK 时基时钟=系统时钟

EPwm6Regs.TBCTL.bit.CLKDIV=TB_DIV1;

EPwm6Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;//设定 CMPA 为影子寄存器 模式

EPwm6Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm6Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;//在 CTR=Zero 时装载

EPwm6Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm6Regs.AQCTLA.bit.ZRO = AQ_SET;//CTR=ZERO 时,将 ePWM6A 置高

EPwm6Regs.AQCTLA.bit.CAU = AQ_CLEAR;//CTR=CAU 时,将 ePWM6A 置低

EPwm6Regs.AQCTLB.bit.ZRO = AQ_SET;//CTR=ZERO 时,将 ePWM6B 置高

EPwm6Regs.AQCTLB.bit.CBU = AQ_CLEAR;//CTR=CAU 时,将 ePWM6B 置低

EPwm6Regs.CMPA.half.CMPA = Duty1A;//调整 ePWM6A 的占空比

EPwm6Regs.CMPB = Duty1B;//调整 ePWM6B 的占空比

![[数据集][目标检测]辣椒缺陷检测数据集VOC+YOLO格式695张5类别](https://i-blog.csdnimg.cn/direct/fe807c92e6a6466facf5814713ed790d.png)

![[Python学习日记-30] Python中数据类型与文件操作的补充(Bytes 类型、字符编码的转换、深浅 Copy)](https://i-blog.csdnimg.cn/direct/c61c4f5463204867977d5df8528101a2.png)

![Killing LeetCode [416] 分割等和子集](https://i-blog.csdnimg.cn/direct/e71ed447fa1447fa9bff022587b8bd84.png)