本文配置JESD204B PHY的参数,分析其示例工程,并且对该IP进行仿真,由于该IP只是物理层,并没有上层协议,因此与GTX/H其实没有太大区别。

1、配置IP

如下图所示,在IP Catalog中搜索JESD204B的PHY,双击进入配置界面。

该IP只有两个配置界面,主要配置参数都在“Configuration”界面,如下图所示。

1. Physical Resources:用于设置收发器数量,能够设置的最大数值与芯片包含的高速收发器个数有关;因为Zynq7030只有4路高速收发器,因此此处最大只能设置为4。本文设置两路GTXE2实现的高速收发器。

2. Line Rate Switching:线速率设置,该IP可以设置固定的线速率和可变线速率。设置为固定线速率后可以关闭axi_lite配置接口,使用可变线速率时,必须使用axi_lite去改变线速率,同时需要设置最小和最大线速率。

本文采用可变线速率,最小线速率为3.125Gb/s,最大线速率为6.25Gb/s,如下图所示。

3、Transmitter:发送通道参数设置,因为7系列FPGA只能使用JESD204B协议,协议类选和编码方式均不能进行更改。

可以设置该通道初始线速率,线速率数值必须处于2处设置的动态线速率范围内,后续在工程运行的过程中,可以通过修改前文提到的分频系数,对线速率进行修改。

还可以设置参考时钟频率以及PLL的类型,此处线速率比较小,选择CPLL即可。

由于该IP包含多个通道,因此还需要选择其中一个通道作为主通道,默认即可。

4、Receiver:接收通道的参数设置,由于高速Serdes是全双工的,接收通道和发送通道可以独立工作,且QPLL和CPLL的输出时钟在发送通道和接收通道的PMA中均可进行不同的D分频,因此同一个收发器的接收通道和发送通道其实也能支持不同的线速率。

5、配置DRP时钟,设为100MHz即可,该时钟信号可以来源于任何bank。

6、axi_lite配置时钟,如果2处选用静态线速率,则此处可以屏蔽axi_lite配置接口,如果2处选用动态线速率,则此处的axi_lite接口必须使用,时钟频率设置为100MHz,与DRP使用同一时钟信号即可。

7、调试端口信号,勾选后可以将收发器的一些调试信号输出,一般不会使用。

然后在“Shared Logic”界面配置共享逻辑的位置,将共享逻辑放在内核外部或者内部都行。本文先将共享逻辑放在示例工程中,后面在正式使用时,很可能将共享逻辑放在内核中。

点击OK生成IP即可,该IP配置其实比较简单,编码协议这些都是固定的,比GTX/H都简单很多。

2、分析示例工程

鼠标选中前面生成的IP,然后右键点击“Open IP Example Design…”打开示例工程,如下图所示。

然后需要指定示例工程存放路径,如下所示,可以保持默认。

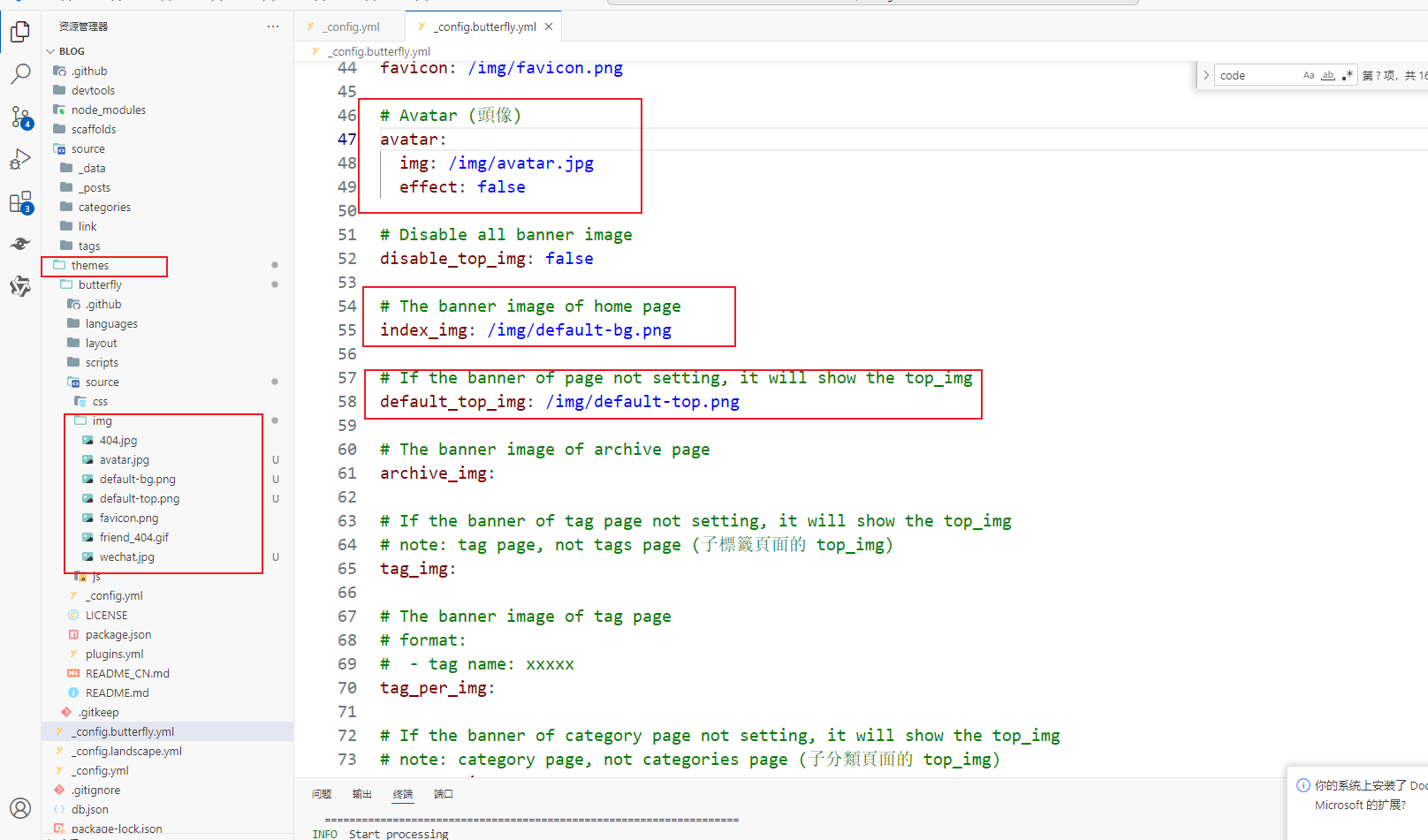

拿到示例工程之后,直接打开工程的RTL视图,查看工程内各个模块的信号流向,确定各个模块大致功能,如下图所示。

与多数高速IP一样,示例工程都包含时钟处理模块、测试数据生成模块、接收数据检测模块、JESD204B顶层模块,如下图所示。

时钟处理模块通过使用IBUFDS将差分时钟输入信号转换为单端时钟信号,其中高速收发器的参考时钟信号需要使用IBUFDS_GTE2进行转换,如下图所示。

打开JESD204B PHY顶层模块的RTL视图,如下所示,包含GT_COMMON和JESD204B PHY的IP。

如果你将JESD204B PHY的RTL一层一层打开,最终会看见下图所示的界面,包含两个GT收发器,因此该IP就是在GTX/H的基础上封装得到的,将很多信号封装在AXI配置接口之中了。

JESD204B PHY的IP内部还有一个AXI的配置模块,该模块相当于把底层的多路GT收发器的一些DRP配置参数、端口配置参数转换成了一个axi_lite接口,使得用户可以通过一个axi_lite接口配置多路收发器内部寄存器参数。

示例工程分析到此结束,其实并不需要去看代码,根据信号流向和模块名去判断其大致功能。然后通过仿真查看关键信号的时序即可,不需要去看测试数据生成模块和数据检测模块的代码。

3、示例工程仿真

添加JESD204B顶层模块的信号,然后运行工程的仿真,得到如下所示结果。在取消复位后,会通过axi_lite接口配置IP内部的一些寄存器。

将上述axi_lite写时序放大,如下图所示,包含对两个通道回环模块的设置,最终均设置为正常工作模式,没有使用回环模式。

注意在配置通道参数时,需要先配置地址为0x24的寄存器,然后才能配置对应通道的寄存器参数,否则后续所有参数都是对当前设置的通道进行配置的,这也是有的人配置线速率后,为什么只有一个通道线速率改变的原因。

地址为0x41c的寄存器用户高速收发器的回环模式的设置,但是该寄存器数值为7并没有对应的回环模式,上述仿真最后也将回环模式设置为正常模式,所以没有影响。

地址为0x1c的寄存器用于设置超时值,这个的作用不是很了解,后续遇到再说具体含义吧,手册中的描述如下所示。

示例工程只对上述三个寄存器进行了设置,用户想要配置其余寄存器,根据这个时序和手册的寄存器描述进行配置即可。

复位不会清除配置寄存器的数据,因此要在复位完成之前对寄存器进行配置才会有用,配置完寄存器一段时间后完成复位,接收端需要先完成数据对齐,复位才会完成。

由于本项目接收端和发送端都没有使用QPLL,因此上图中QPLL并没有锁定,不影响功能。

之后查看两个通道发送数据和接收的数据,如下图所示,接收和发送的数据一致,其余前文GTX的8B10B编码模式的端口时序一致,不再赘述。

仿真到此结束,后续上板测试需要将顶层axi_lite接口注释掉,并且将一些时钟信号进行更改。因此拿到后续提供的工程代码,是不能用来进行仿真的,自己生成示例工程进行仿真即可。

4、上板测试

由于开发板并没有提供示例工程这些端口,需要把端口信号简化,如下所示,将axi_lite接口注释,时钟默认配置即可。然后将用户时钟信号和DRP时钟还有复位信号都注释掉。添加了光纤失能信号sfp_disable。

将axi_lite接口的复位信号取反替换之前的另一个复位信号,如下所示。

由于时钟相关的信号需要进行一些更改,因此直接注释掉之前的时钟处理模块,如下图所示。

使用下面这段代码替换上述模块,高速BANK的差分参考时钟频率为156.25MHz,经过IBUFDS_GTE2转换为单端时钟cpll_refclk。而用户端口时钟rx/tx_coreclk等于线速率3.125G/40=78.125Mhz,刚好是cpll_refclk的二分频,按理说可以直接从IBUFDS_GTE2的二分频端口输出,但是在布局布线的时候出错了,因此只能将cpll_refclk通过BUFG输入锁相环后进行分频。

同时将光纤失能信号赋值为低电平。

锁相环输入配置为156.25MHz,即cpll_refclk的时钟频率。

然后将锁相环的输出频率设置为78.125MHz,如下图所示,取消锁相环的复位信号和锁定指示信号。

并且加入一个ILA观测两路收发器的输入信号和输出信号,还有复位完成指示信号和接收端对齐信号的状态,如下所示,ILA深度设置为2048。

将JESD204B PHY的顶层模块的axi_lite接口信号注释,并且做无效处理,然后用axi_lite的复位取代之前的复位。

代码更改到此结束,之后综合工程,然后根据光纤接口的原理图分配工程引脚。其中高速收发器相关差分信号,axi_lite的时钟和复位信号不能分配错误,其余状态输出信号可以随意分配,不用关心。

生成比特流之后,使用光纤短接两个光口,如下图所示,然后烧入比特流文件。

将接收端复位完成作为ILA触发条件,然后按下开发板的复位按键,即可抓取对应波形数据。

触发结果如下所示,在接收端复位完成后一段时间就成功对齐了。

2路发送通道的时序如下图所示。

2路接收通道的时序如下所示,与上图发送通道起始发送的数据一致,证明两路收发器的均正常工作。

到此,本文通过示例工程验证了该IP寄存器的配置方式,以及正常工作的接口时序,与GTX/H 8B10B接口时序基本一致。

可以在公众号后台回复“JESD204B PHY示例工程”(不包含引号)获取修改后的示例工程。

![[半导体检测-6]:为什么晶圆缺陷检测精度越高,所需要的光源的波长越短?](https://i-blog.csdnimg.cn/direct/4d70863f7de3440ba3577c96f4441528.png)