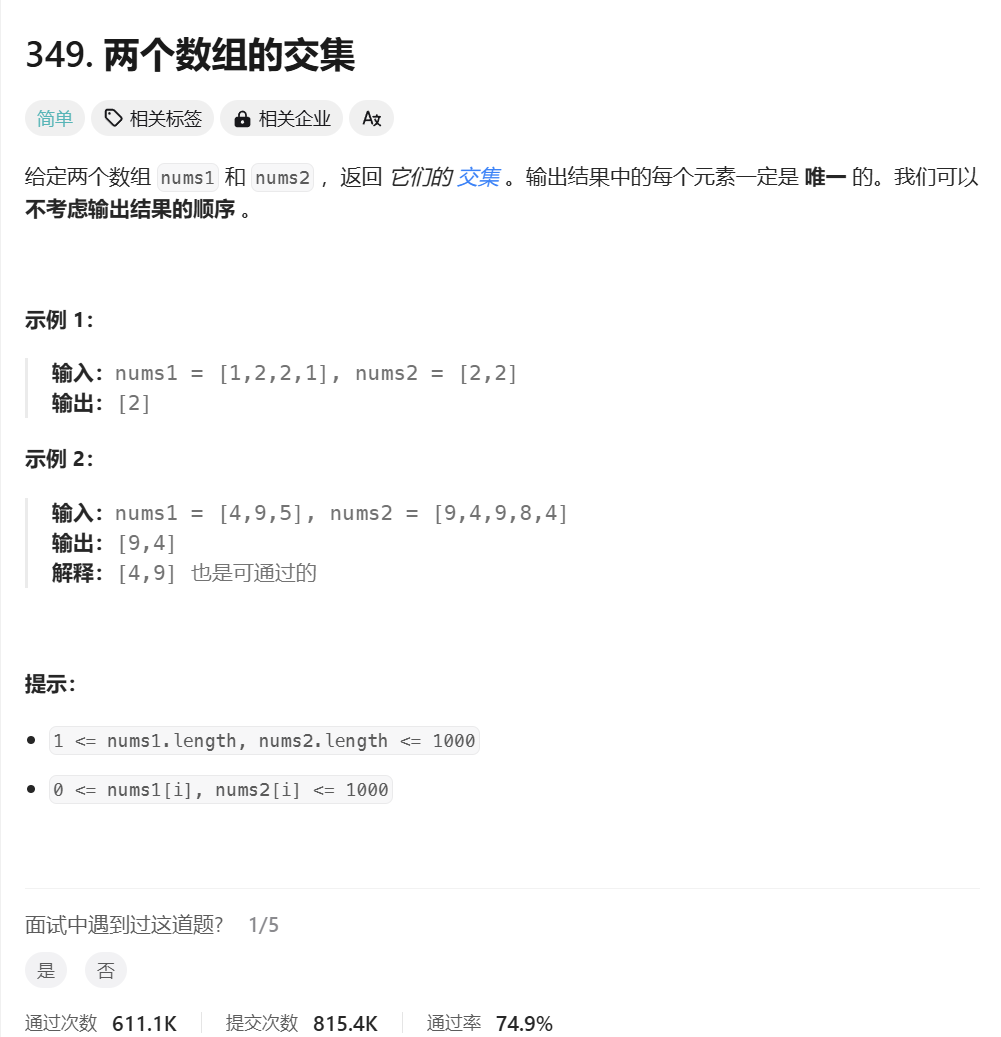

结论:

ARM :To mark these lines, each line of the cache has an associated dirty bit (or bits)

所以这个依赖硬件实现,可能只刷出dirty bytes of cache line to memory.有的硬件只有一个dirty bit,所以会刷出整条cache line

x86没有找到官方文档,所以猜测应该也是类似的。

https://developer.arm.com/documentation/den0013/d/Caches/Cache-architecture/A-real-life-example#:~:text=The%20cache%20line%20length%20is%20eight%20words%20%2832,index%20a%20line%20within%20a%20way%20%28bits%20%5B12%3A5%5D%29.

A real-life example

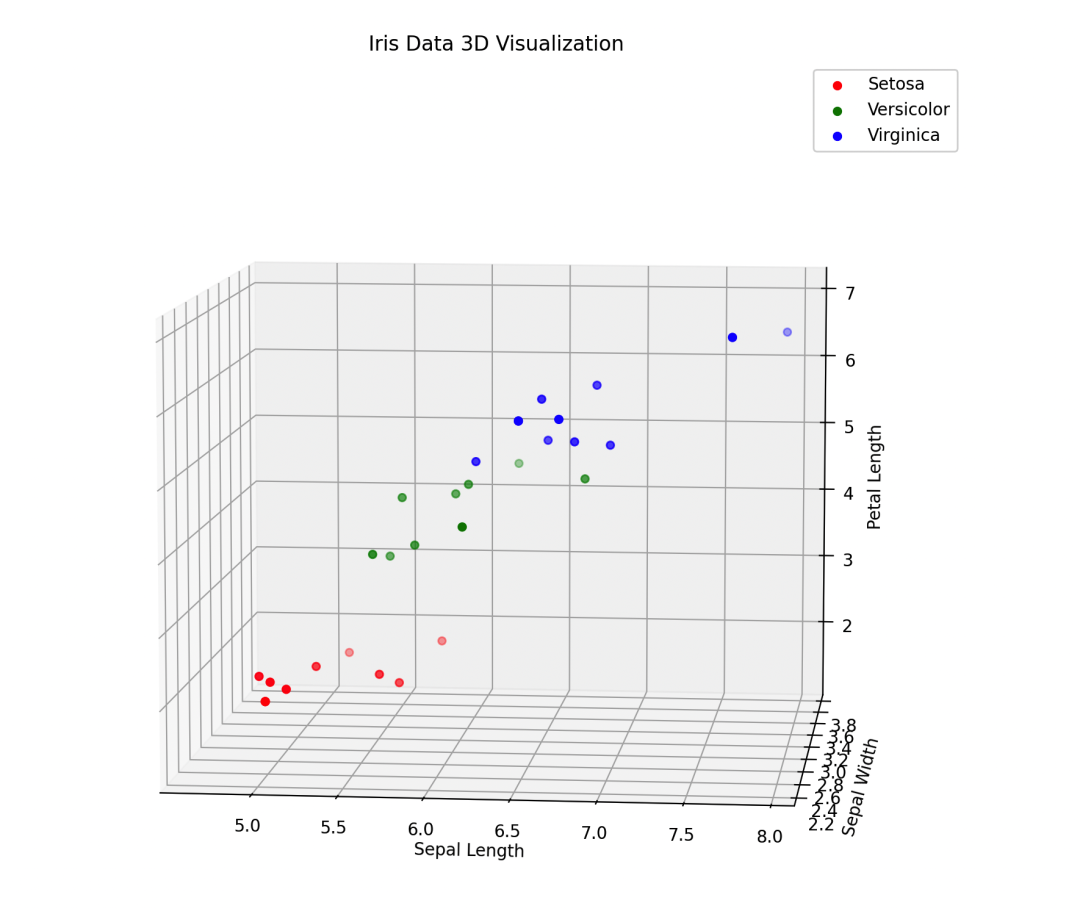

Before going on to look at write buffers, let's consider an example that is more realistic than those shown in the previous two diagrams. Figure 8.7 is a 4-way set associative 32KB data cache, with an 8-word cache line length. This kind of cache structure can be found on the Cortex-A7 or Cortex-A9 processors.

The cache line length is eight words (32 bytes) and you have 4-ways. 32KB divided by 4 (the number of ways), divided by 32 (the number of bytes in each line) gives you a figure of 256 lines in each way. This means that you require eight bits to index a line within a way (bits [12:5]). Here, you must use bits [4:2] of the address to select from the eight words within the line, though the number of bits which are required to index into the line depends on whether you are accessing a word, halfword, or byte. The remaining bits [31:13] in this case will be used as a tag.

Figure 8.7. A 32KB 4-way set associative cache

Documentation – Arm Developer

Invalidating and cleaning cache memory

Cleaning and invalidation can be required when the contents of external memory have been changed and you want to remove stale data from the cache. It can also be required after MMU related activity such as changing access permissions, cache policies, or virtual to physical address mappings.

The word flush is often used in descriptions of clean and invalidate operations. ARM generally uses only the terms clean and invalidate.

-

Invalidation of a cache or cache line means to clear it of data. This is done by clearing the valid bit of one or more cache lines. The cache must always be invalidated after reset as its contents will be undefined. If the cache contains dirty data, it is generally incorrect to invalidate it. Any updated data in the cache from writes to write-back cacheable regions would be lost by simple invalidation.

-

Cleaning a cache or cache line means writing the contents of dirty cache lines out to main memory and clearing the dirty bit(s) in the cache line. This makes the contents of the cache line and main memory coherent with each other. This is only applicable for data caches in which a write-back policy is used. Cache invalidate, and cache clean operations can be performed by cache set, or way, or by virtual address.

https://developer.arm.com/documentation/den0013/d/Caches/Cache-policies/Write-policy#:~:text=The%20cache%20line%20holds%20newer%20data,%20and

-

Write-back. In this case, writes are performed only to the cache, and not to main memory. This means that cache lines and main memory can contain different data. The cache line holds newer data, and main memory contains older data (said to be stale). To mark these lines, each line of the cache has an associated dirty bit (or bits). When a write happens that updates the cache, but not main memory, the dirty bit is set. If the cache later evicts a cache line whose dirty bit is set (a dirty line), it writes the line out to main memory. Using a write-back cache policy can significantly reduce traffic to slow external memory and therefore improve performance and save power. However, if there are other agents in the system that can access memory at the same time as the core, you must consider coherency issues. These are described in Cache coherency.