摘要

基础模型的核心理念是“更多即不同”,这一理念在计算机视觉和自然语言处理领域取得了惊人的成功。然而,变压器模型的优化挑战和固有复杂性呼唤一种向简化转变的范式。在本研究中,引入了 VanillaNet,一种拥抱设计优雅的神经网络架构。通过避免高深度、快捷方式和复杂操作如自注意,VanillaNet 设计简洁而功能强大。每一层都精心设计为紧凑和简洁,训练后修剪非线性激活函数以恢复原始架构。VanillaNet 克服了固有的复杂性挑战,非常适合资源受限的环境。其易于理解和高度简化的架构为高效部署开辟了新可能。广泛的实验表明,VanillaNet 在性能上与著名的深度神经网络和视觉变压器相当,展示了极简主义在深度学习中的力量。VanillaNet 的这一愿景之旅具有重新定义基础模型格局和挑战现状的巨大潜力,为优雅和高效的模型设计开辟了新路径。

模型细节:

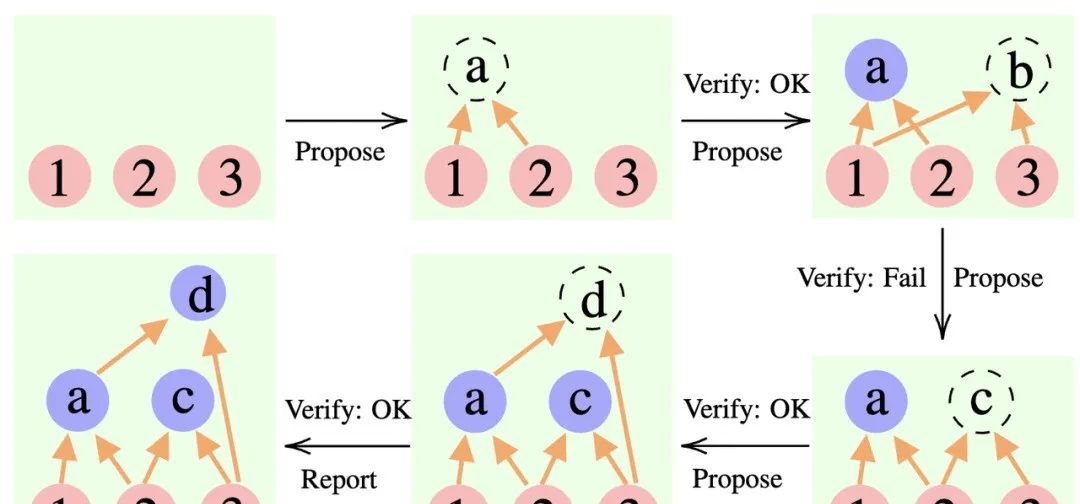

VanillaNet-6 模型的架构,仅由 6 个卷积层组成,非常容易在任何现代硬件上使用。输入特征的大小在每个阶段都被下采样,而通道数则加倍,这借鉴了经典神经网络如 AlexNet 和 VGGNet 的设计。结构如下图所示:

该结构通过避免深度、高度复杂的操作(如自注意力机制)和快捷连接,实现了设计上的简洁优雅。以下是 VanillaNet 的不同版本的架构细节:

- stem: 初始卷积层,使用 4×4 的卷积核,输出通道数为 512,步幅为 4。

- stage1: 第一阶段,特征图大小为 56×56,包括一个 1×1 的卷积层,输出通道数为 1024,之后接一个 2×2 的最大池化层。

- stage2: 第二阶段,特征图大小为 28×28,包括一个 1×1 的卷积层,输出通道数为 2048,之后接一个 2×2 的最大池化层。

- stage3: 第三阶段,特征图大小为 14×14,包括一个或多个 1×1 的卷积层,输出通道数为 4096,之后接一个 2×2 的最大池化层。层数根据不同版本的 VanillaNet 变化(如 VanillaNet-7 有 1 层,VanillaNet-8 有 2 层,以此类推)。

- stage4: 第四阶段,特征图大小为 7×7,包括一个 1×1 的卷积层,输出通道数为 4096。

classifier: 分类器部分,首先是一个 7×7 的平均池化层,然后是一个 1×1 的卷积层,输出通道数为 1000(对应 ImageNet 的 1000 个分类)。 - 上表中列出了不同版本的 VanillaNet 的详细架构。对于 VanillaNet-13-1.5×,所有卷积层的通道数乘以 1.5。对于 VanillaNet-13-1.5׆,在 stage2、stage3 和 stage4 采用了自适应池化,特征图大小分别调整为 40×40、20×20 和 10×10。

官网表显示了使用不同网络在ImageNet数据集上的分类结果。列出了参数数量、FLOPs、深度、GPU 延迟和准确性以进行比较。在过去的几十年里,研究人员专注于在 ARM/CPU 上最小化 FLOPs 或延迟&