DDR=Double Data Rate双倍速率,DDR SDRAM=双倍速率同步动态随机存储器,人们习惯称为DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的缩写,即同步动态随机存取存储器。而DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。

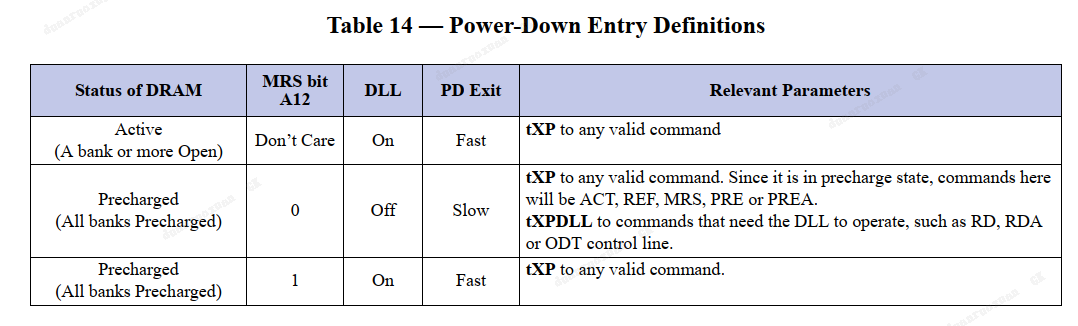

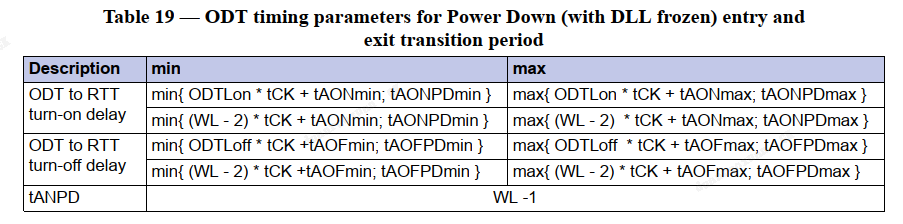

时序参数在文档的表68

1.DDR管脚

| 信号 | 类型 | 描述 |

| CK, CK#(#:取反) | input | 时钟:CK和CK#是不同时钟输入。所有的地址和控制输入信号都在CK的上升沿和CK#的下降沿(CK下降CK#上升不行!)的交叉处采样 |

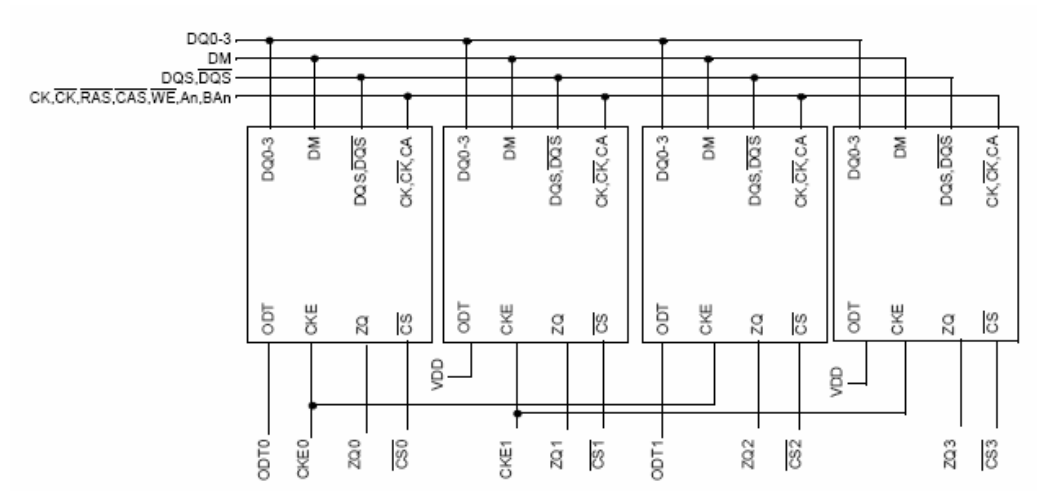

| CKE, (CKE0), (CKE1) | input | 时钟使能,高有效。拉低提供PRECHARGE POWER-DOWN和自刷新操作(all bank idle),或 Active Power-Down (bank中任意行active)。对于自刷新退出,CKE是异步的。VREFCA和VREFDQ在上电和初始化顺序中稳定后,在所有操作(包括Self-Refresh)中都需要维护。CKE必须在整个读写访问过程中保持高位。 输入缓冲器,不包括CK, ck#, ODT和CKE,在断电期间被禁用。在自我刷新期间禁用输入缓冲区(不包括CKE)。 |

| CS#, (CS0#), (CS1#), (CS2#), (CS3#) | input | 片选信号:当CS#注册为HIGH时,所有命令都被屏蔽。#CS提供额外的rank选择。CS#是指令码的一部分。 片选,低电平有效,选中memory颗粒,选中不同的颗粒的化,比如选中4个颗粒,至少需要四个片选信号,一个rank往往对应多个颗粒,也就是选中多片,而一般一个cs信号只对应一片。 |

| ODT, (ODT0), (ODT1) | input | 片上端接:ODT为高使能DDR3 SDRAM内部的终端电阻? 当使能时,对于x4/x8配置,ODT仅应用于每个DQ、DQS、DQS#和DM/TDQS、NU/TDQS#(当TDQS通过MR1中的模式寄存器A11=1使能时)信号。对于x16配置,ODT应用于每个DQ、DQSU、dqsu#、DQSL、DQSL#、DMU和DML信号。如果MR1和MR2被编程为禁用RTT,那么ODT引脚将被忽略 |

| RAS#. CAS#. WE# | input | 输入命令:RAS#、CAS#和WE#(以及CS#)定义输入的命令。 RAS:行地址选通脉冲 CAS:列地址选通脉冲 |

| DM, (DMU), (DML) | input | 输入数据掩码:DM是用于写入数据的输入掩码信号。当DM被屏蔽时,输入数据被屏蔽在写入访问期间,采样的高电平与该输入数据一致。DM在两者上都进行了采样DQS的边缘。对于x8设备,DM或TDQS/TDQS#的功能由模式寄存器启用MR1中的A11设置。 |

| BA0 - BA2 | input | bank输入地址:BA0-BA2定义使能、读取、写入或precharge到哪个bank。bank地址还决定了在MRS周期期间要访问哪个模式寄存器。 |

| A0 - A15 | input | 地址输入:为active命令提供行地址,为读写命令提供列地址以从相应bank中选择一个位置。 (A10/APA12/BC#具有附加功能;见下文)。地址输入在模式寄存器配置期间还提供操作码。 |

| A10 / AP | input | pre-charge:在读/写命令期间对A10进行采样,以确定是否读/写操作后,是否应对访问的bank进行autocharge。(高:Autoprecharge;低:no Autoprecharge)。A10在pre-charge命令期间被采样以确pre-charge是适用于一个bank(A10低)还是适用于所有bankpre-charge(A10高)。如果只有一个bank需要pre-charge,bank由BA信号选择。 |

| A12 / BC# | input | 突发终止:在读取和写入命令期间对A12/BC#进行采样,以确定突发终止是否将被执行。(HIGH, 不终止; LOW: 终止) |

| RESET# | input | 低有效异步复位 |

| DQ | inout | 数据输入/输出:双向数据总线。 |

| DQU, DQL, DQS, | inout | 数据选通(strobe):输出读数据,输入写数据。边缘与读取的数据对齐,与写数据居中。对于x16,DQSL对应于DQL0-DQL7上的数据;DQSU对应DQU0-DQU7上的数据。数据选通DQS、DQSL和DQSU与分别提供不同信号DQS#、DQSL#和DQSU#,以提供不同对在读写过程中向系统发送信号。DDR3 SDRAM支持不同数据选通,不支持single-ended。 |

| TDQS, TDQS# | output | 终端数据选通:TDQS/TDQS#仅适用于x8 DRAM。通过启用时 MR1中的模式寄存器A11=1,DRAM将启用相同的termination resistance功能 关于应用于DQS/DQS#的TDQS/TDQS#。当通过模式寄存器A11=0禁用时 MR1、DM/TDQS将提供数据掩码功能并且不使用TDQS#。x4/x16 DRAM 必须通过MR1中的模式寄存器A11=0禁用TDQS功能。 |

bank:存储库的意思,BA地址位宽决定有几个存储库。

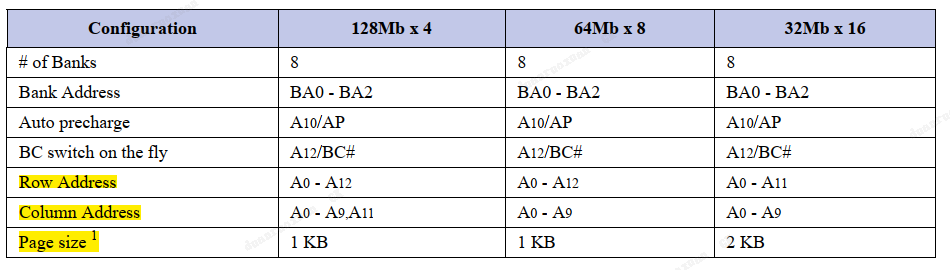

2.DDR3 SRAM地址

以512MB为例:

page size是在寄存ACTIVE命令时从aray传递到内部感测放大器的数据字节数。page size按bank计算,计算如下:

3.功能描述

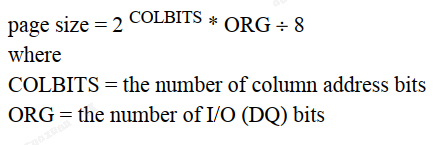

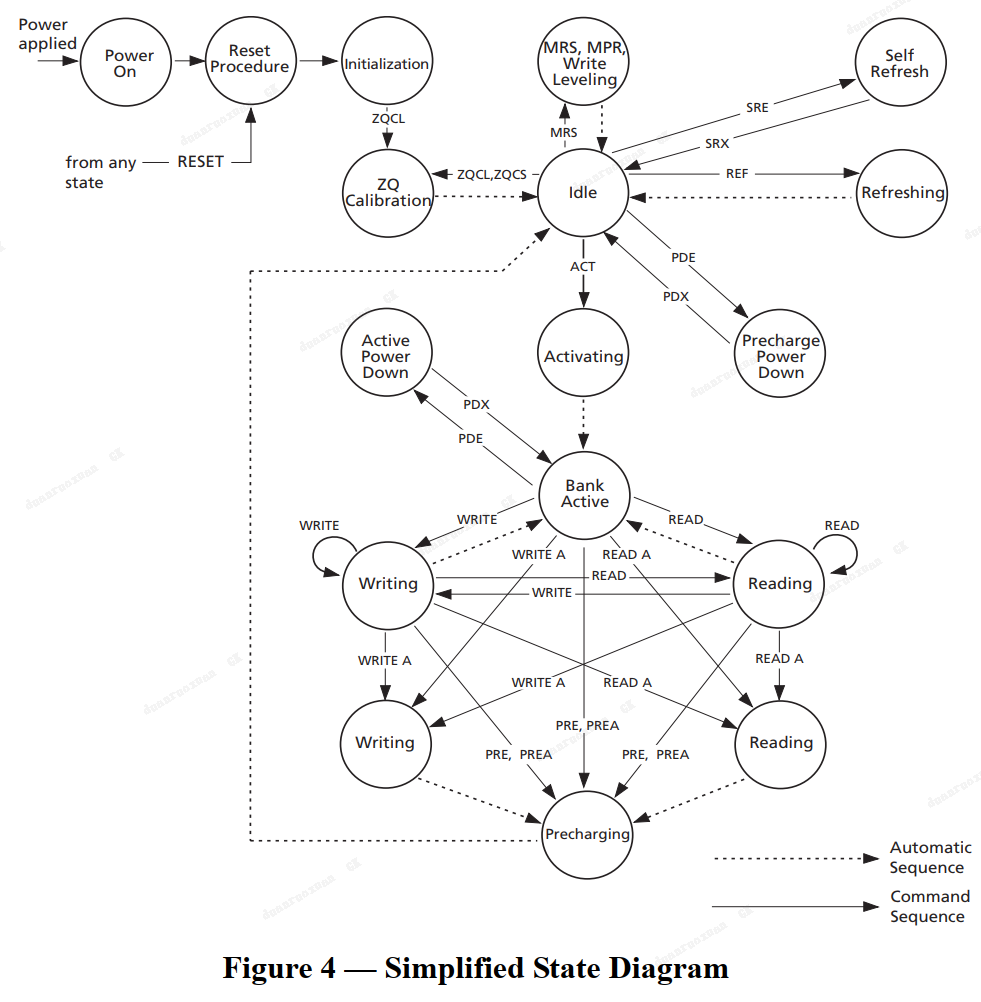

3.1简化状态图

这个简化的状态图旨在提供可能的状态转换和控制它们的命令的概述。需要注意的是,涉及多个bank的情况、启用或禁用ODT以及其他一些事件都没有得到详细记录。

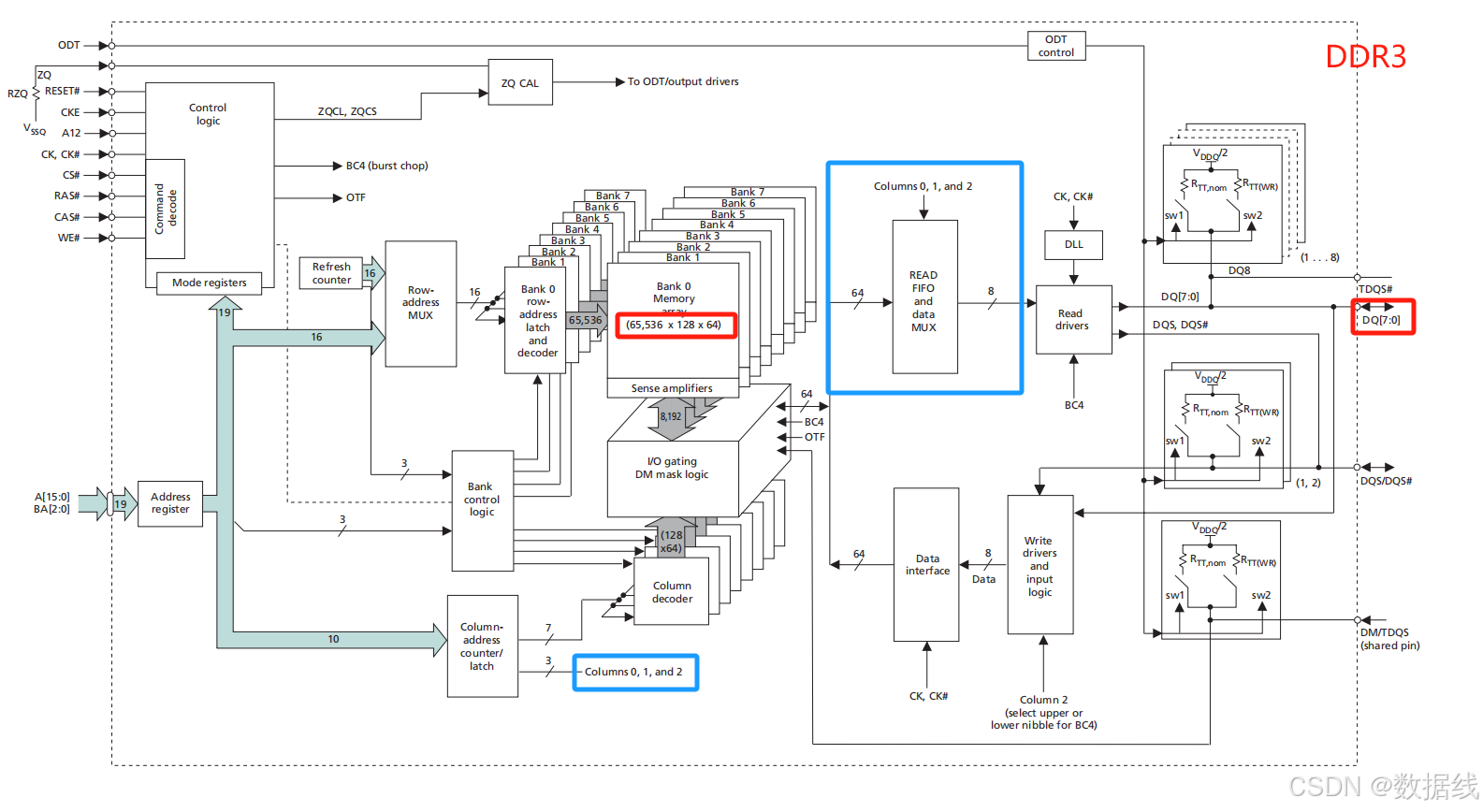

3.2基本功能

DDR3 SDRAM是一种内部配置为八存储体DRAM的高速动态随机存取存储器。DDR3 SDRAM使用8n预取架构来实现高速操作。8n预取架构与一个接口相结合,该接口设计用于在I/O引脚上每个时钟周期传输2words(16bits)数据。DDR3 SDRAM的单次读取或写入操作包括在内部DRAM核心进行一次8n位宽的四时钟数据传输,以及在I/O引脚进行八次相应的n位宽的半时钟周期数据传输。

预取是DDR时代提出的技术,预取的本质上是并串转换,通过并行方式提前取得数据再串行输出。

在DDR3中采用8-bit prefetch或8-n prefetch(n代表芯片位宽),从而使实际数据传输速率为核心频率的8倍。

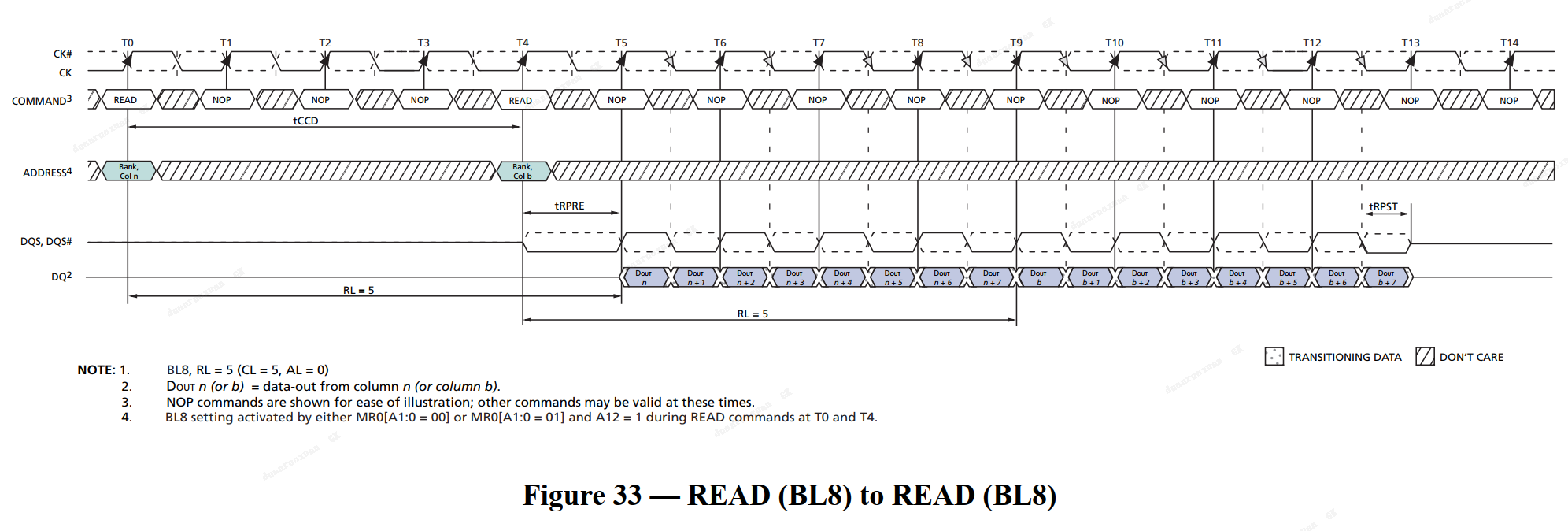

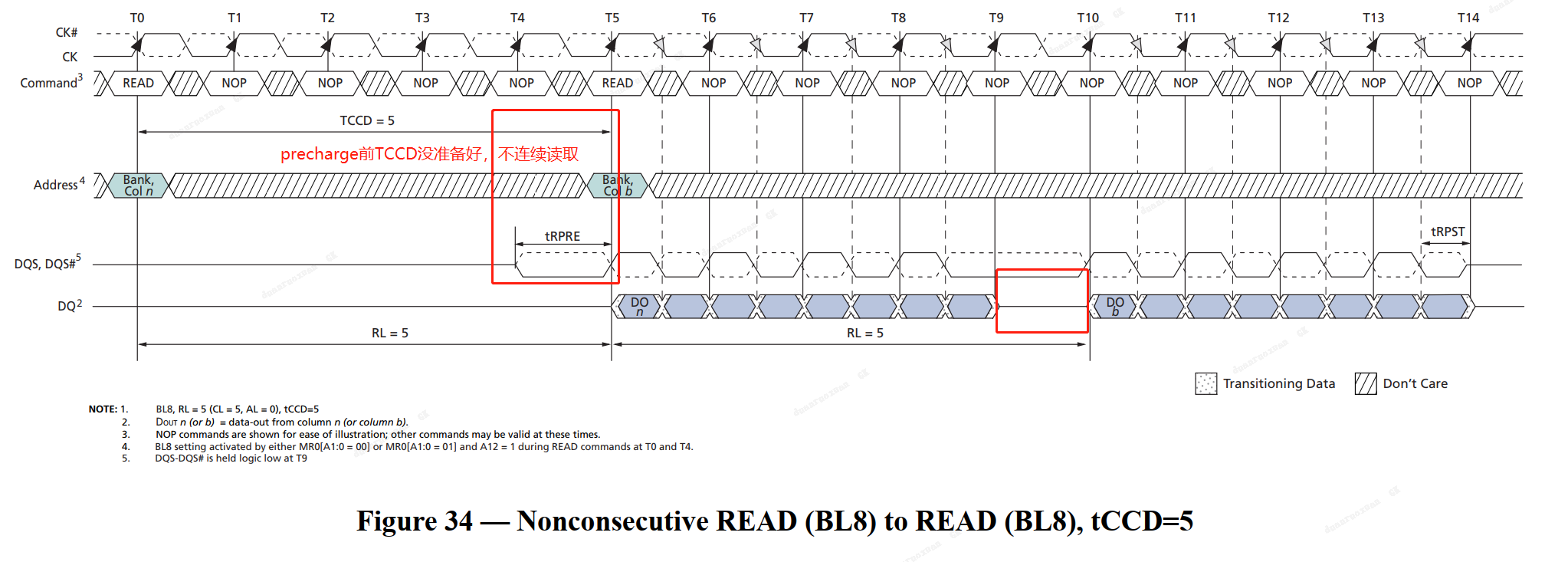

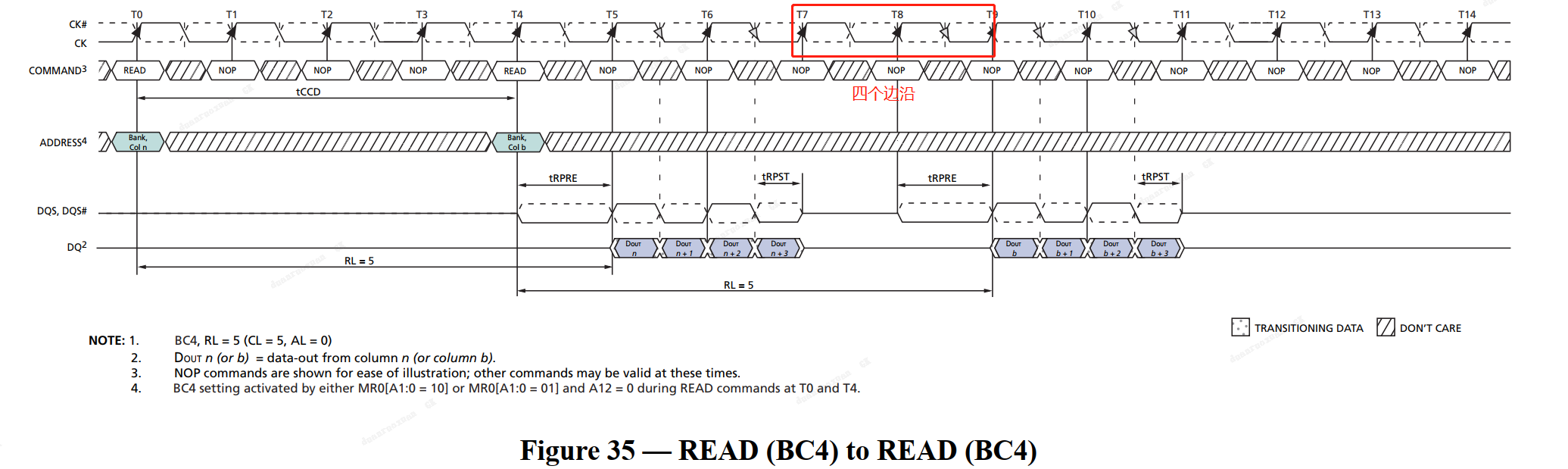

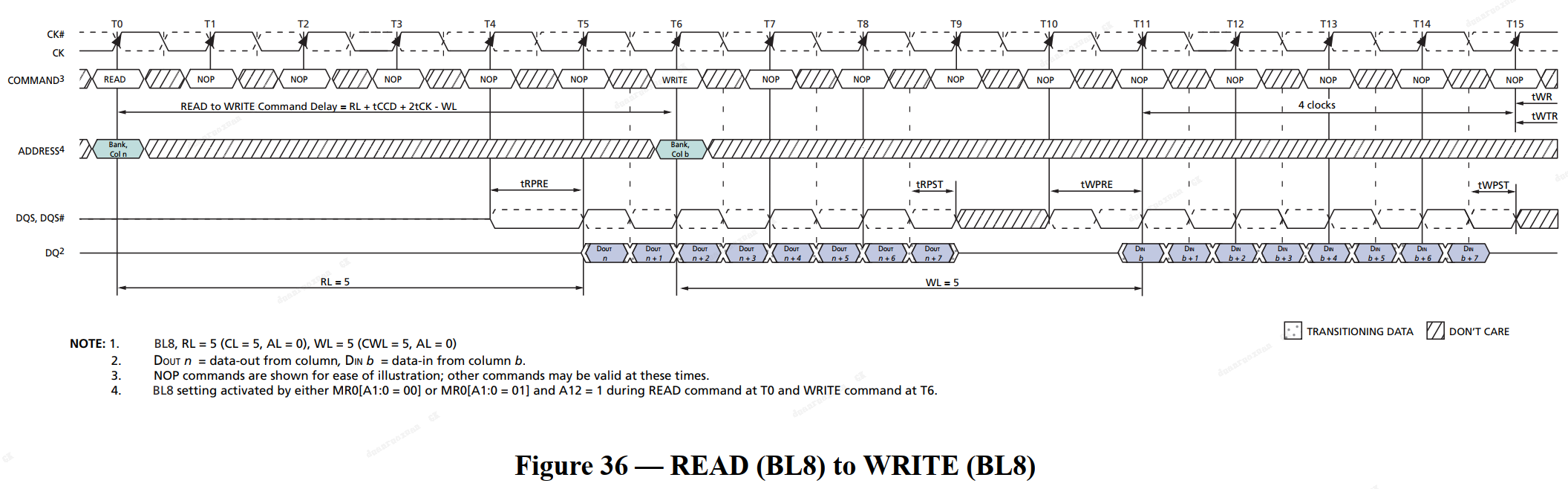

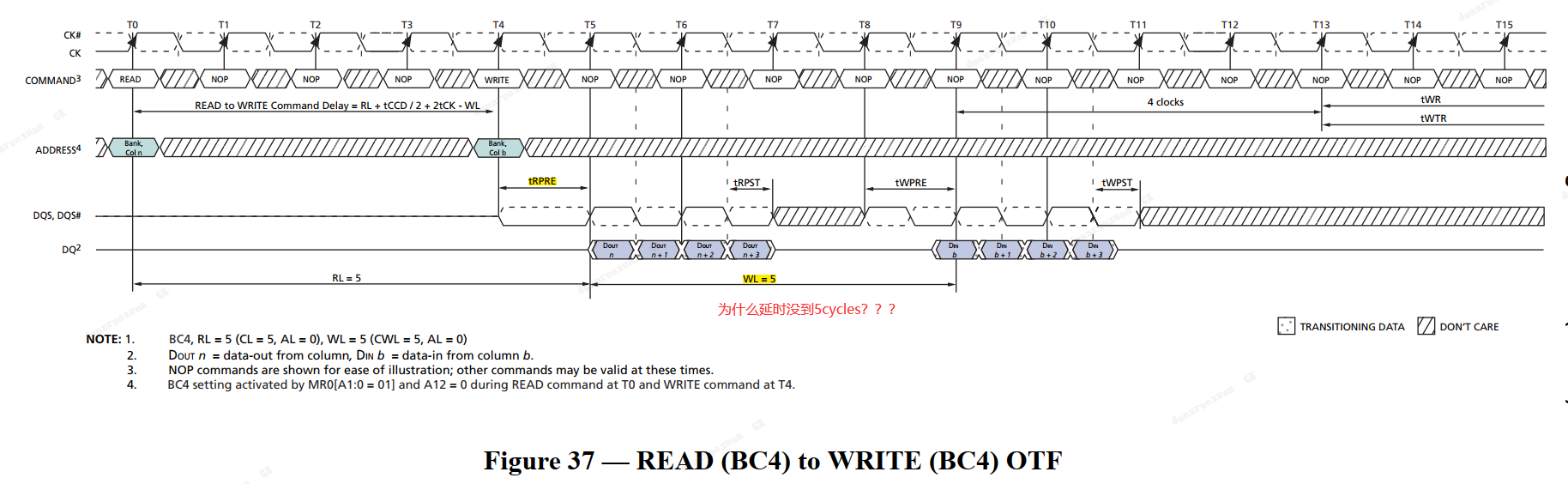

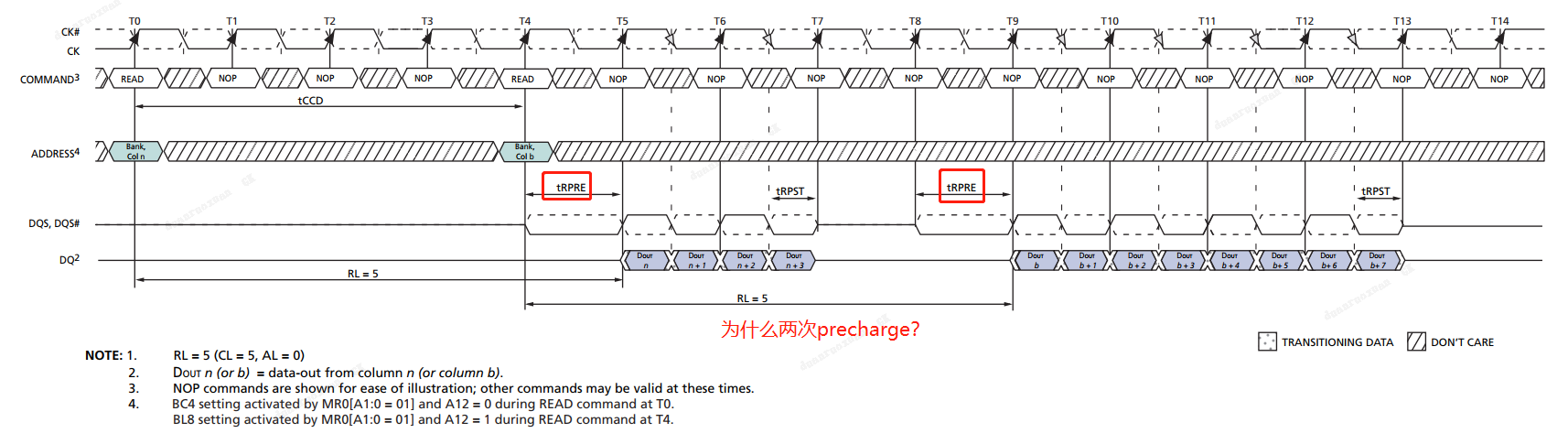

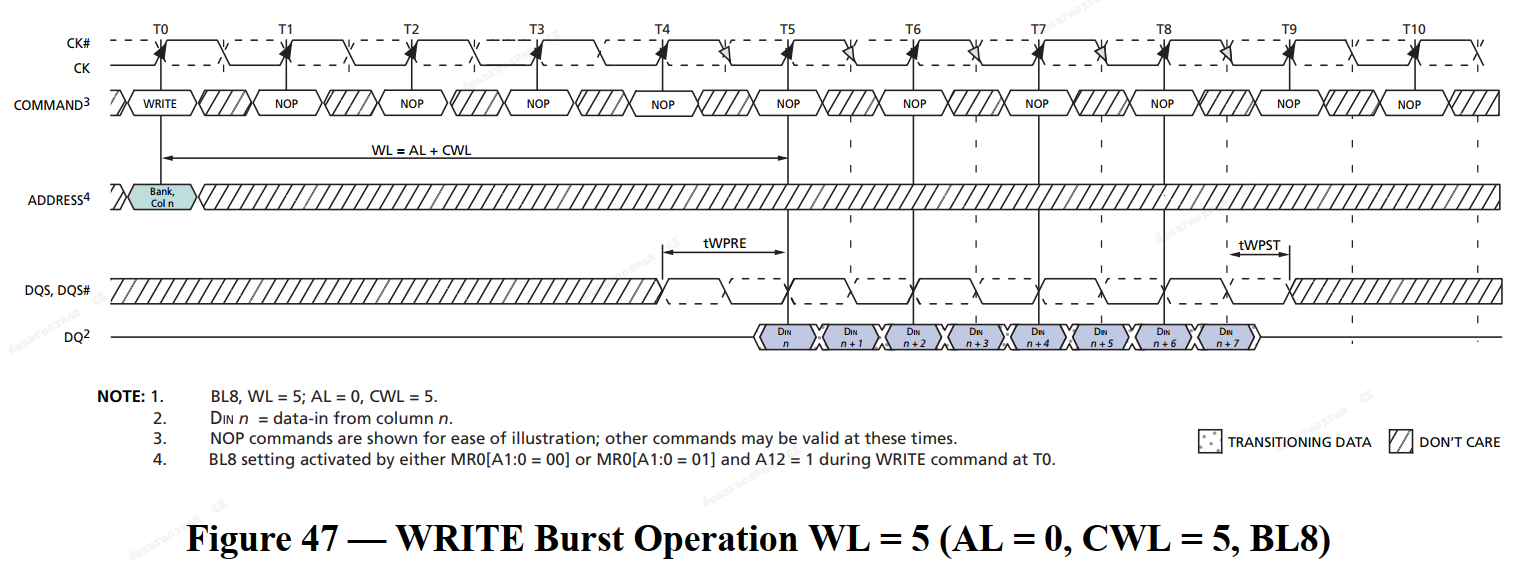

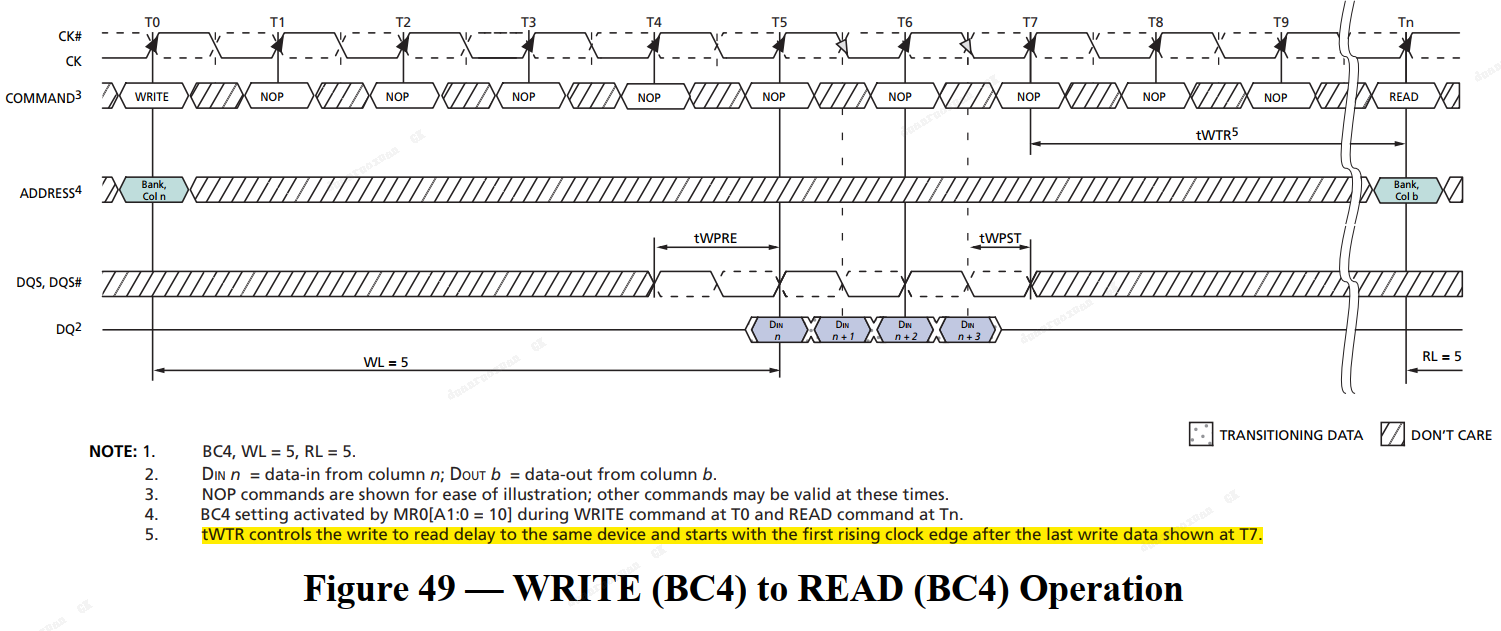

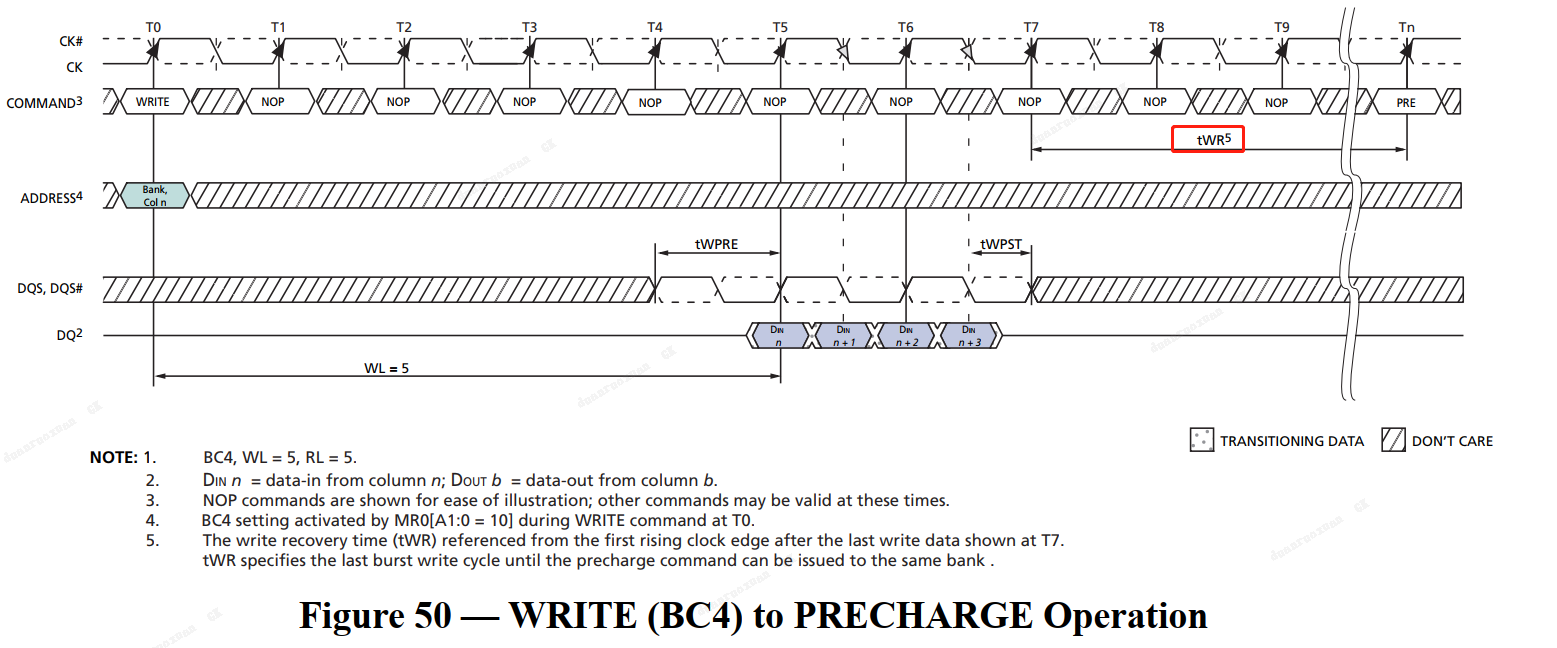

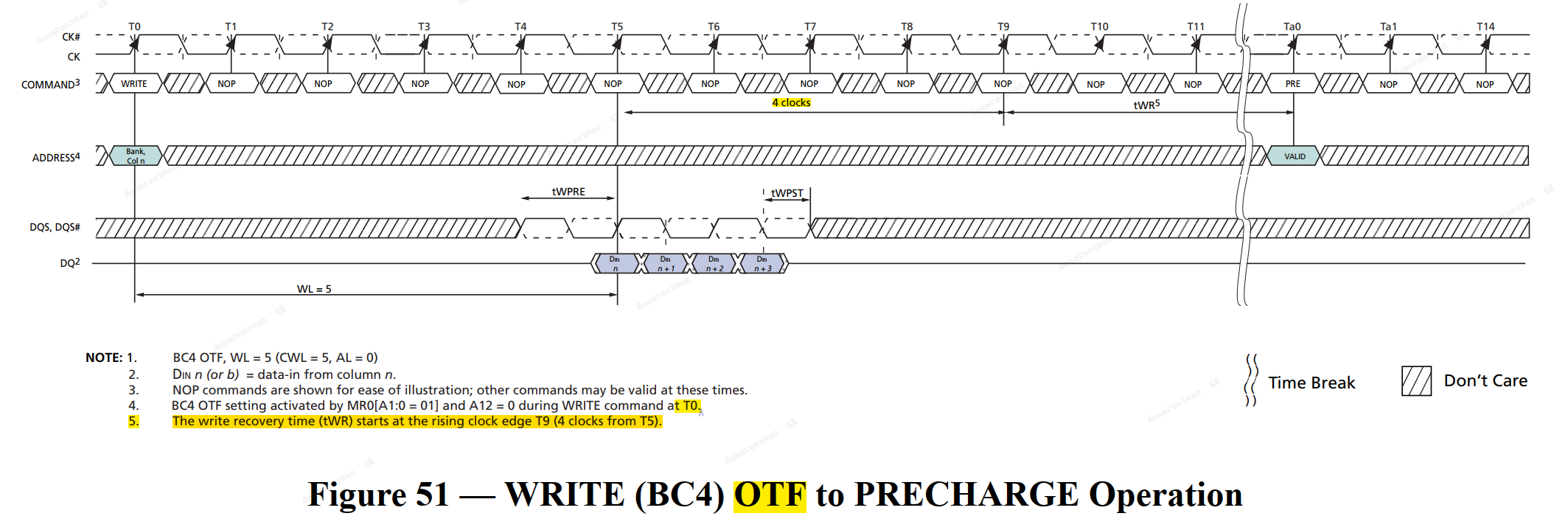

对DDR3 SDRAM的读写操作是以突发方式进行的,从所选位置开始,并以编程序列连续进行BL8或者一个BC4。操作从注册一个激活命令开始,然后是读取或写入命令。与激活命令一起注册的地址位用于选择要激活的bank和行(即在16Gb部件中,x4/8情况下,BG0-BG2和x16情况下,BG0-BG1选择bank组;BA0-BA1选择bank;R0-R17选择行;具体要求请参考第2.7节)。与读取或写入命令一起注册的地址位用于选择突发操作的起始列位置,确定是否发出自动预充电命令(CA10=L),并在模式寄存器中启用时选择BC4动态调节(OTF)、固定BL8模式。在正常操作之前,DDR3 SDRAM必须按预定义的方式上电并进行初始化。以下各节提供了关于设备复位和初始化、寄存器定义、命令描述和设备操作的详细信息。

1.读和写操作是面向burst的,read or write BL=8 或 4 ;

//2.操作先进行激活(ACTIVATE)命令,后进行读写命令;

3.ACTIVATE命令的address bits用于选择要激活的bank 和 row;

4.READ or WRITE命令的address bits用于确定burst操作开始列的位置,决定是否要进行自动预充电(预充电时,需要CA10=L),并且选择BC4/BL8模式(在使能了MR情况下);

5.先于正常操作,DDR3必须按照预定方式上电和初始化;

3.3复位/初始化步骤

3.3.1上电初始化顺序

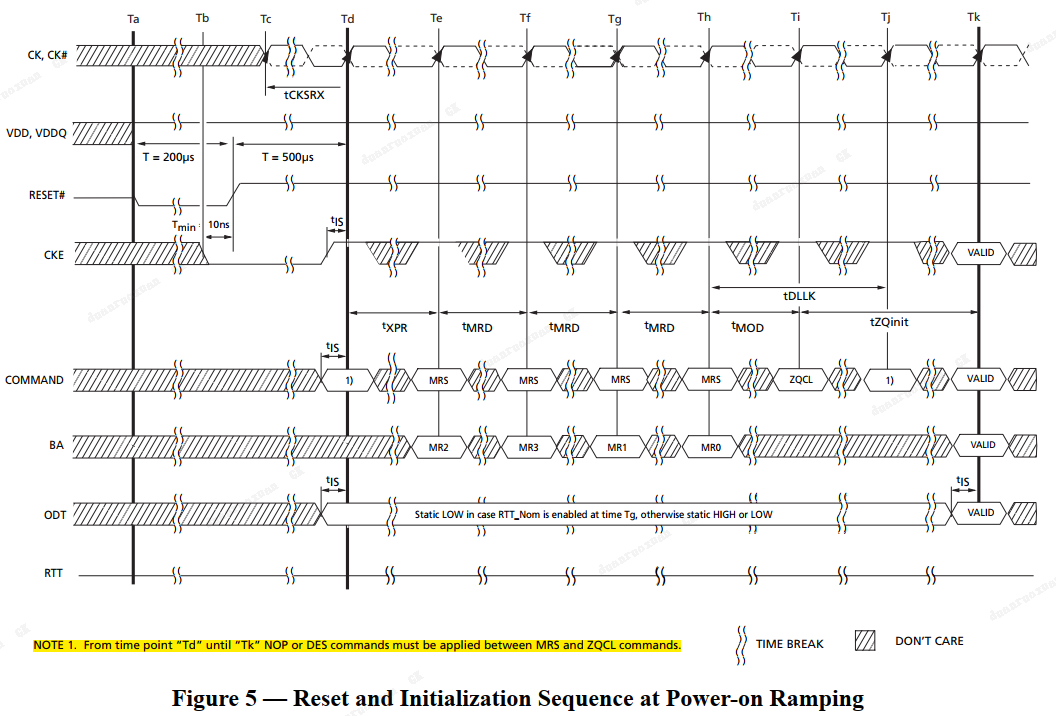

通电和初始化需要以下顺序:

- 接通电源(建议将RESET#保持在0.2 x VDD以下;所有其他输入可能未定义)。RESET#需要在电源稳定的情况下保持至少200 us。在RESET#被取消断言之前的任何时候,CKE都会被拉到“低”(最短时间为10 ns)。300mv至VDDmin之间的电源电压斜坡时间不得超过200ms;在斜坡期间VDD>VDDQ和(VDD-VDDQ)<0.3伏。

- 在RESET#被取消断言后,再等待500 us,直到CKE变为使能状态。在此期间DRAM将开始内部状态初始化;这将独立于外部时钟完成。

- 在CKE激活之前,时钟(CK、CK#)需要启动并稳定至少10 ns或5 tCK(以较大者为准)。由于CKE是一个同步信号,因此必须满足相应的时钟设置时间(tIS)。此外,在CKE激活之前,必须寄存NOP或取消选择命令(具有tIS设置时间)。一旦重置后CKE寄存为“高”,CKE需要连续寄存为“高”,直到初始化序列完成,包括tDLLK和tZQinit到期。

- 只要RESET#被断言,DDR3 SDRAM就会将其ODT保持在高阻抗(Z?)状态。此外,在RESET#取消初始化后,SDRAM将其ODT保持在高阻抗状态,直到CKE被注册为高。ODT输入信号可能处于未定义状态,直到CKE被记录为高电平之前的tIS。当CKE被寄存为高时,ODT输入信号可以静态地保持在低或高。如果要在MR1中启用RTT_NOM,ODT输入信号必须静态保持为低。在所有情况下,ODT输入信号保持静态,直到加电初始化序列完成,包括tDLLK和tZQinit到期

- 在CKE寄存为高后,等待重置CKE退出时间,tXPR(在加载模式寄存器的第一个MRS命令之前)。(tXPR=max(tXS;5 x tCK)

- 发出MRS命令以加载具有所有应用程序设置的MR2。(为了向MR2发出MRS命令,为BA0和BA2提供“低”,为BA1提供“高”。)

- 发出MRS命令以加载具有所有应用程序设置的MR3。(为了向MR3发出MRS命令,为BA2提供“低”,为BA0和BA1提供“高”。)

- 发出MRS命令,在启用所有应用程序设置和DLL的情况下加载MR1。(要发出“DLL启用”命令,请将A0设置为“低”,BA0设置为“高”,BA1–BA2设置为“低等”)。

- 发出MRS命令,加载带有所有应用程序设置和“DLL重置”的MR0。(要发出DLL重置命令,请为A8提供“高”,为BA0-2提供“低”)。

- 发出ZQCL命令以启动ZQ校准。

- 等待tDLLK和tZQinit都完成。

- DDR3 SDRAM现在已准备好正常运行。

Vcc和Vdd是器件的电源端。Vcc是双极器件的正,Vdd多半是单极器件的正。

初始化:做寄存器配置

3.3.2稳定电源下的初始化

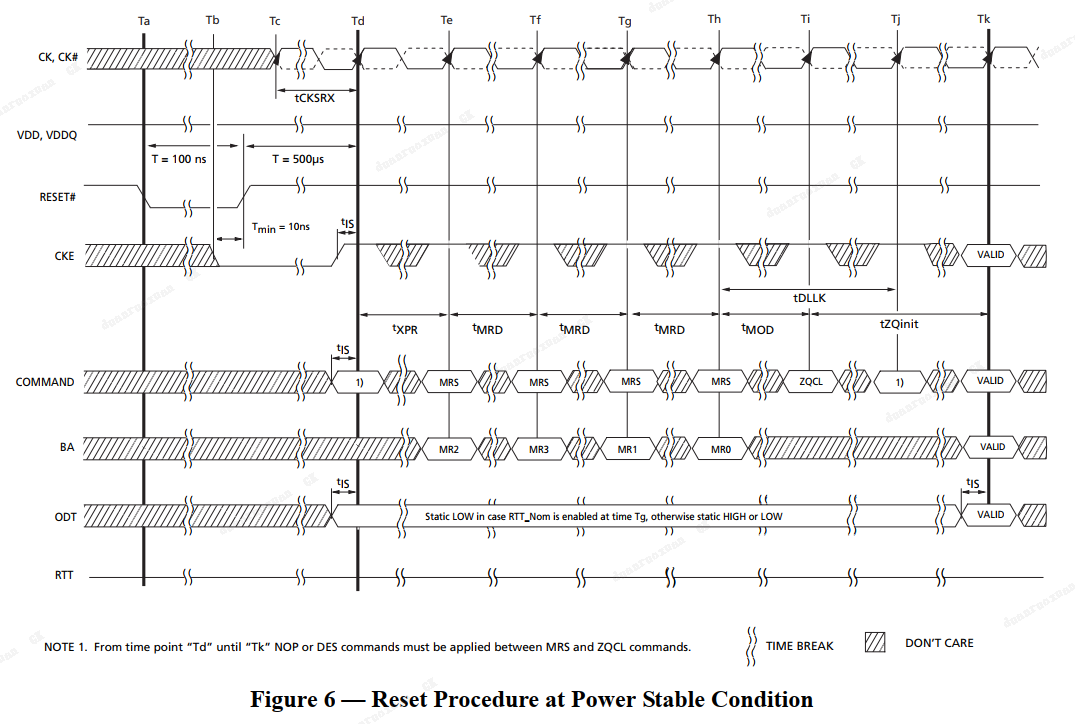

在无电源中断初始化时,重置需要以下顺序。

- 当需要复位时,在0.2*VDD以下断言重置(所有其他输入可能未定义)。RESET需要保持至少100 ns。在复位被取消之前,CKE被拉到“低”(最小时间10 ns)。

- 按上电初始化顺序步骤2至11进行操作。

- 复位完成。

3.4寄存器定义

3.4.1模式寄存器配置

为了使用的灵活性,各种功能、特性和模式都可以在DDR3 SDRAM提供的四个模式寄存器配置,作为用户自定义的变量必须通过模式寄存器(MRS)命令进行配置。由于未定义模式寄存器(MR#)的默认值,因此在通电和/或重置后,模式寄存器的内容必须完全初始化和/或重新初始化,即写入,才能正常运行。此外,在正常操作期间,可以通过重新执行MRS命令来更改模式寄存器的内容。在对模式寄存器进行配置时,即使用户选择仅修改MRS的子域,在发出MRS命令时,所访问的模式寄存器内的所有地址字段都必须重新定义。MRS命令和DLL重置不影响阵列内容,这意味着这些命令可以在通电后随时执行,而不会影响阵列内容。

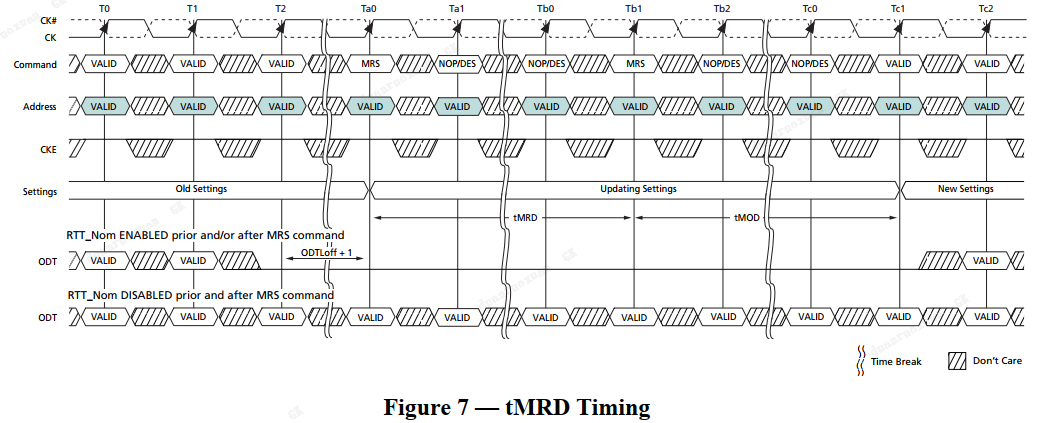

模式寄存器设置命令循环时间tMRD是完成写入操作寄存器所必需的,是图7所示的两个MRS命令之间所需的最短时间。

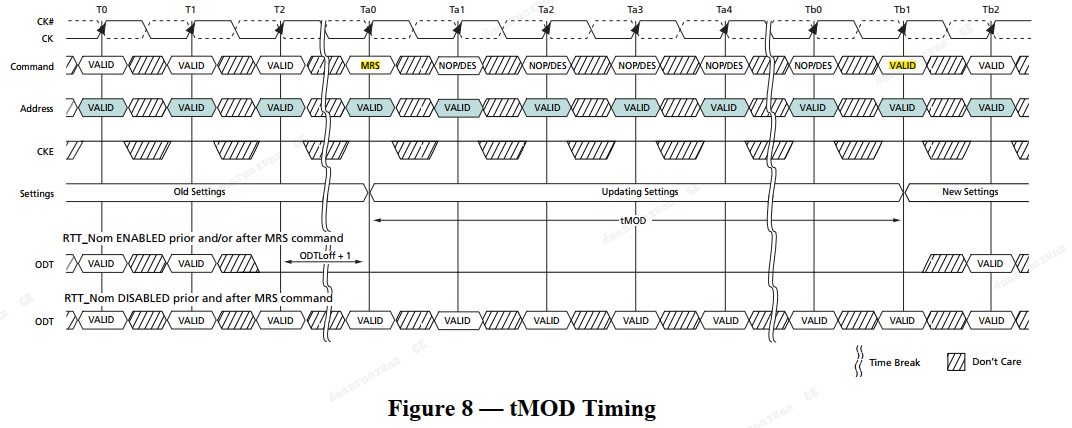

MRS命令到Non-MRS命令延迟tMOD是DRAM更新功能(DLL重置除外)所必需的,是MRS命令到非MRS命令(NOP和DES除外)所需的最短时间,如图8所示。

只要DRAM处于空闲状态,即所有存储体都处于预充状态,满足tRP,所有数据突发都已完成,并且CKE在写入模式寄存器之前为高,在正常操作期间可以使用相同的命令和时序要求来更改模式寄存器的内容。如果在MRS命令之前/或之后在模式寄存器中启用了RTT_NOM功能,则ODT信号必须连续为低,以确保RTT在MRS命令前处于关闭状态。tMOD过后,ODT信号可能会拉高。如果MRS命令前后模式寄存器中的RTT_NOM功能被禁用,则可以在MRS命令之前、期间和之后将ODT信号为低或高。模式寄存器根据功能和/或模式分为不同域。

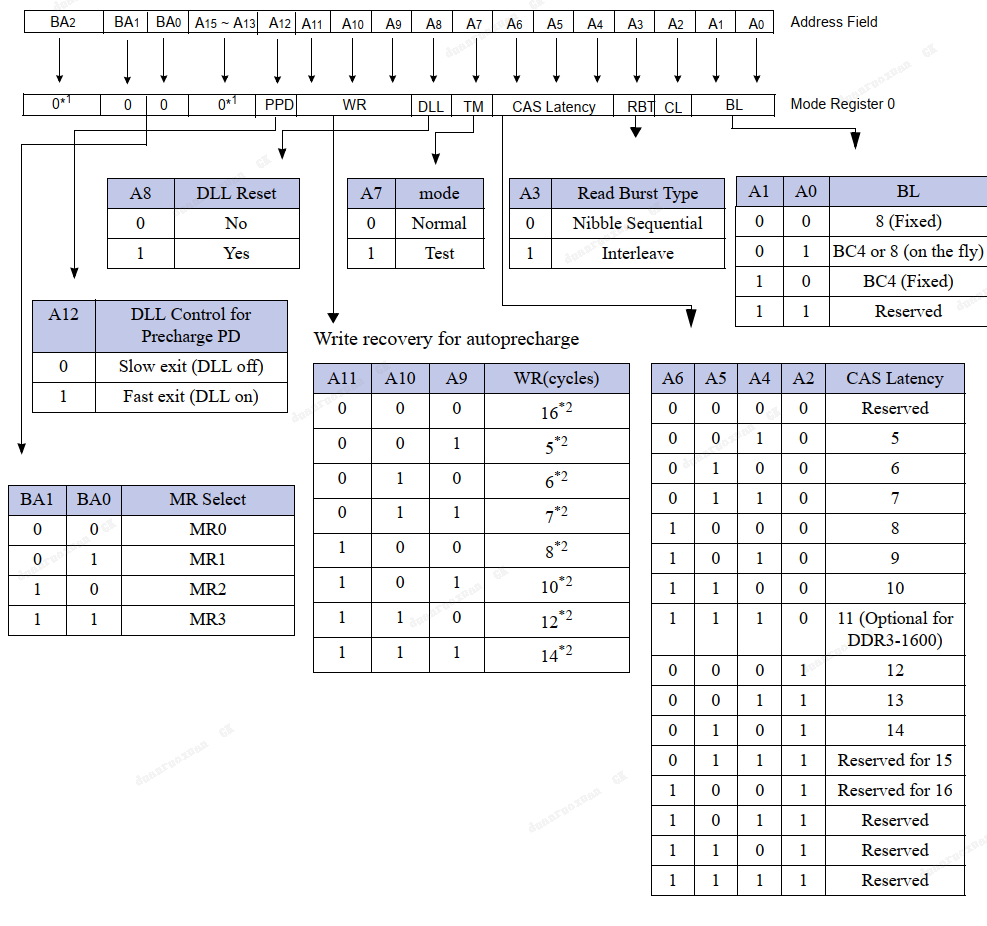

3.4.2模式寄存器MR0

模式寄存器MR0存储用于控制DDR3 SDRAM的各种操作模式的数据。它控制突发长度、读取突发类型、CAS延迟、测试模式、DLL重置、WR和用于预充Power-Down的DLL控制,其中包括各种特定于供应商的选项,以使DDR3 SDRAM适用于各种应用。通过在CS#、RAS#、CAS#、WE#、BA0、BA1和BA2上拉低来写入模式寄存器,同时根据图9控制地址管脚的状态。

BA0、BA1和BA2用于模式寄存器选择,CS#、RAS#、CAS#、WE#拉低进入配置模式。

*1:BA2和A13~A15是RFU,在MRS期间必须配置为0。

*2:WR(自充的写入恢复)最小min时钟周期是通过将tWR(单位为ns)除以tCK(单位为纳秒)并向下取整来计算的。模式寄存器中的WR值必须配置为等于或大于WRmin。配置的WR值与tRP一起用于确定tDAL。

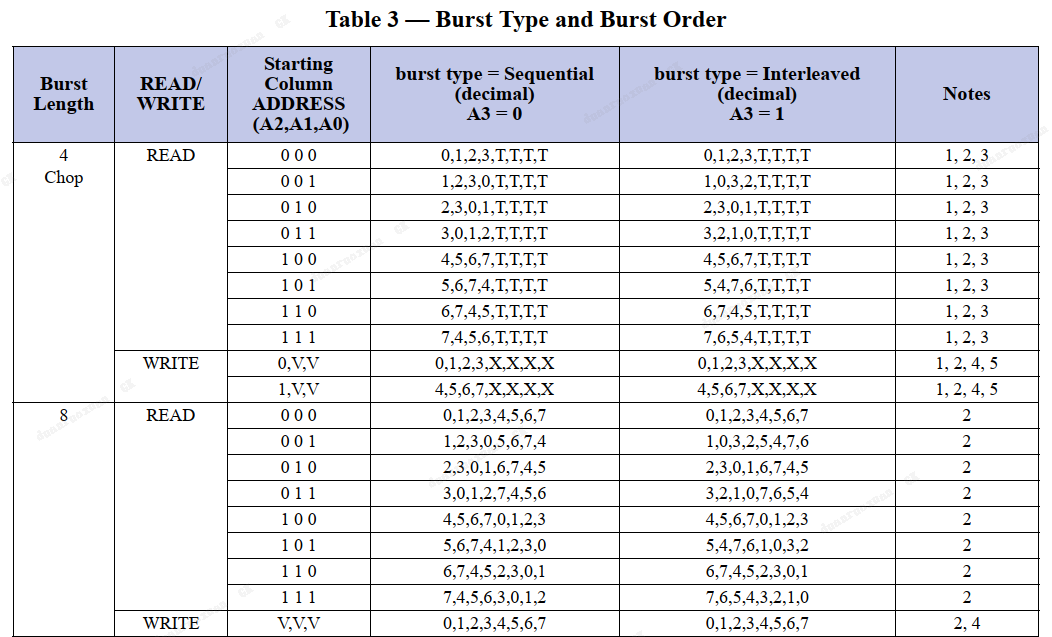

3.4.2.1突发长度、类型和顺序

给定突发内的访问可以被配置为顺序或乱序。如图9所示,通过位A3选择突发类型(乱序、顺序)。如表3所示,突发内的访问顺序由突发长度、突发类型和起始列地址决定。突发长度由比特A0-A1定义。突发长度选项包括固定BC4、固定BL8和“on the fly ”,允许在通过A12/BC#为读取或写入命令的同时选择BC4或BL8。

- 如果MR0设置将突发长度固定为4,则内部写入操作比BL8模式早两个时钟周期开始。这意味着tWR和tWTR的起点将提早两个clock。在通过A12/BC#动态选择突发长度的情况下,内部写入操作在相同的时间点开始,就像突发8写入操作的突发一样。这意味着在动态控制期间,tWR和tWTR的起点不会被提早两个clock。

- 0…7bit数是CA[2:0](啥东西????)的值,它使该位成为突发期间的第一次读取。

- T: 数据和strobe的输出具有高阻态。

- V: 一个有效的逻辑电平(0或1),但相应的缓冲器输入忽略了输入引脚上的电平。

- X: 不在乎

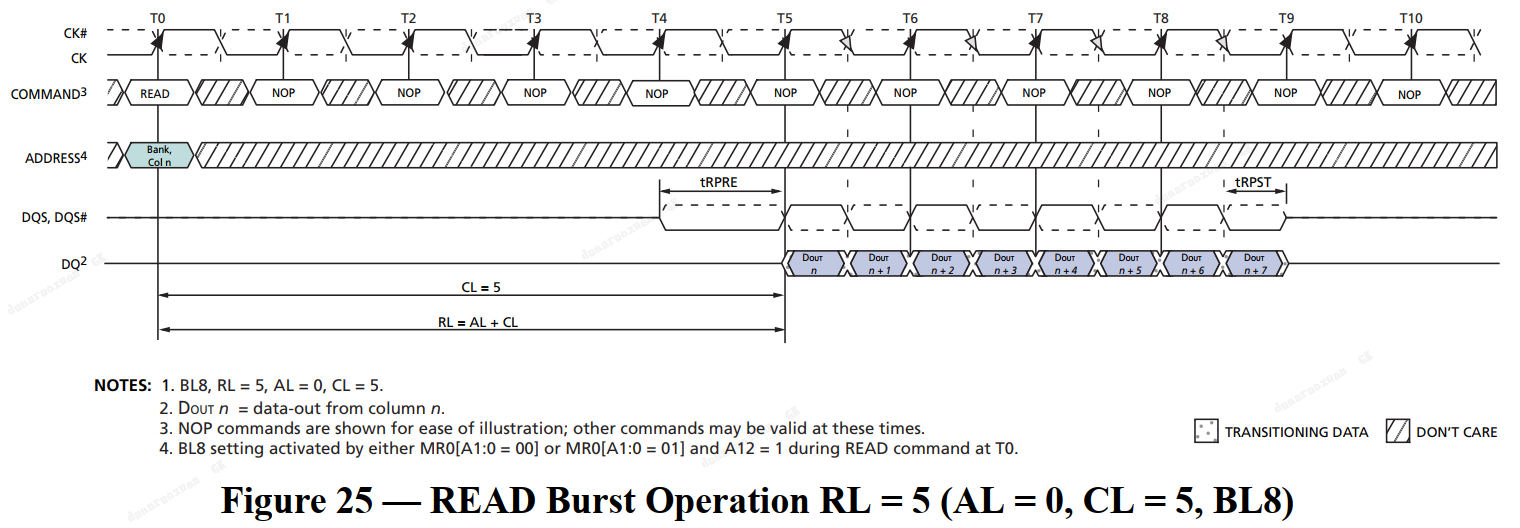

3.4.2.1CAS延迟

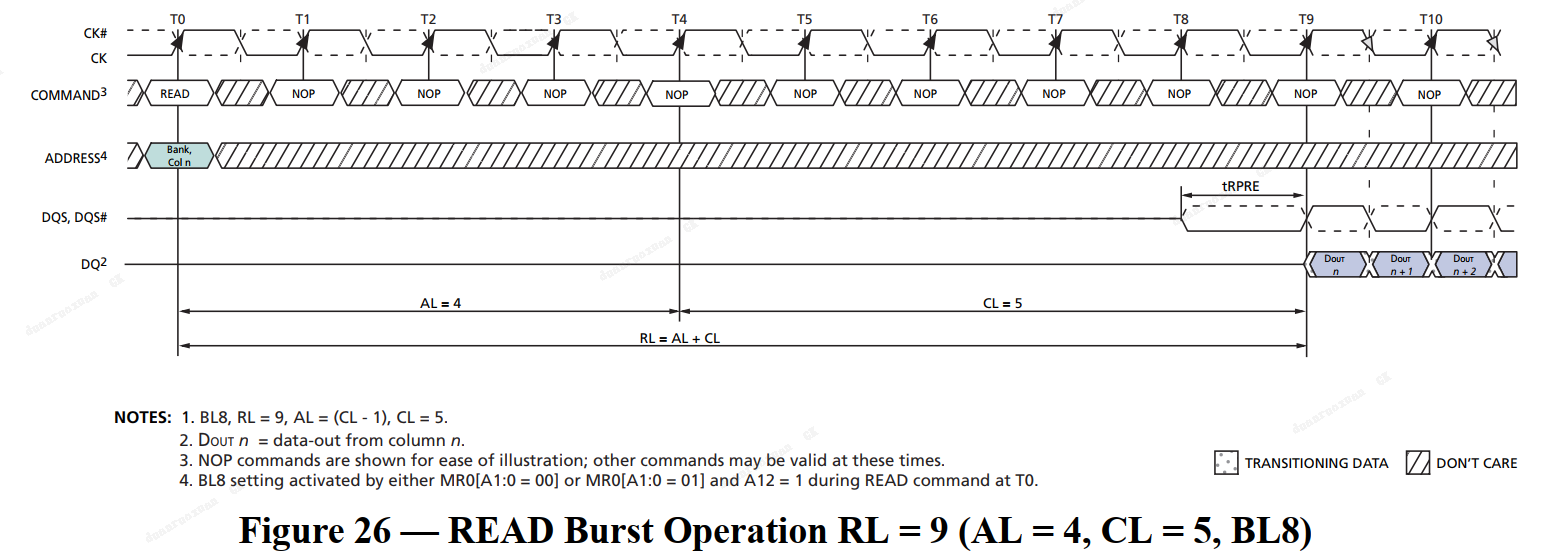

CAS延迟由MR0(位A9-A11)定义,如图9所示。CAS Latency是内部读取命令与第一位有效输出数据之间的延迟(以时钟周期为单位)。DDR3 SDRAM不支持任何半时钟延迟。整体读取延迟(RL)被定义为附加延迟(AL)+CAS延迟(CL);RL=AL+CL。

3.4.2.4DDL 复位

DLL重置位是自清除的,这意味着在发出DLL重置函数后,它将返回到值“0”。启用DLL后,应应用后续的DLL重置。任何时候使用DLL重置功能时,在使用任何需要DLL的功能(即读取命令或ODT同步操作)之前,必须满足tDLLK。

3.4.2.5写恢复

配置WR值MR0(位A9、A10和A11)与tRP一起用于自预充功能,以确定tDAL。时钟周期中的WR(自动预充的写入恢复)最小值是通过将tWR(单位为ns)除以tCK(单位为纳秒)并向下取整来计算的:WRmin[cycles]=(tWR[ns]/tCK[ns])。WR必须配置为等于或大于tWR(min)。

3.4.2.6预充PD DLL

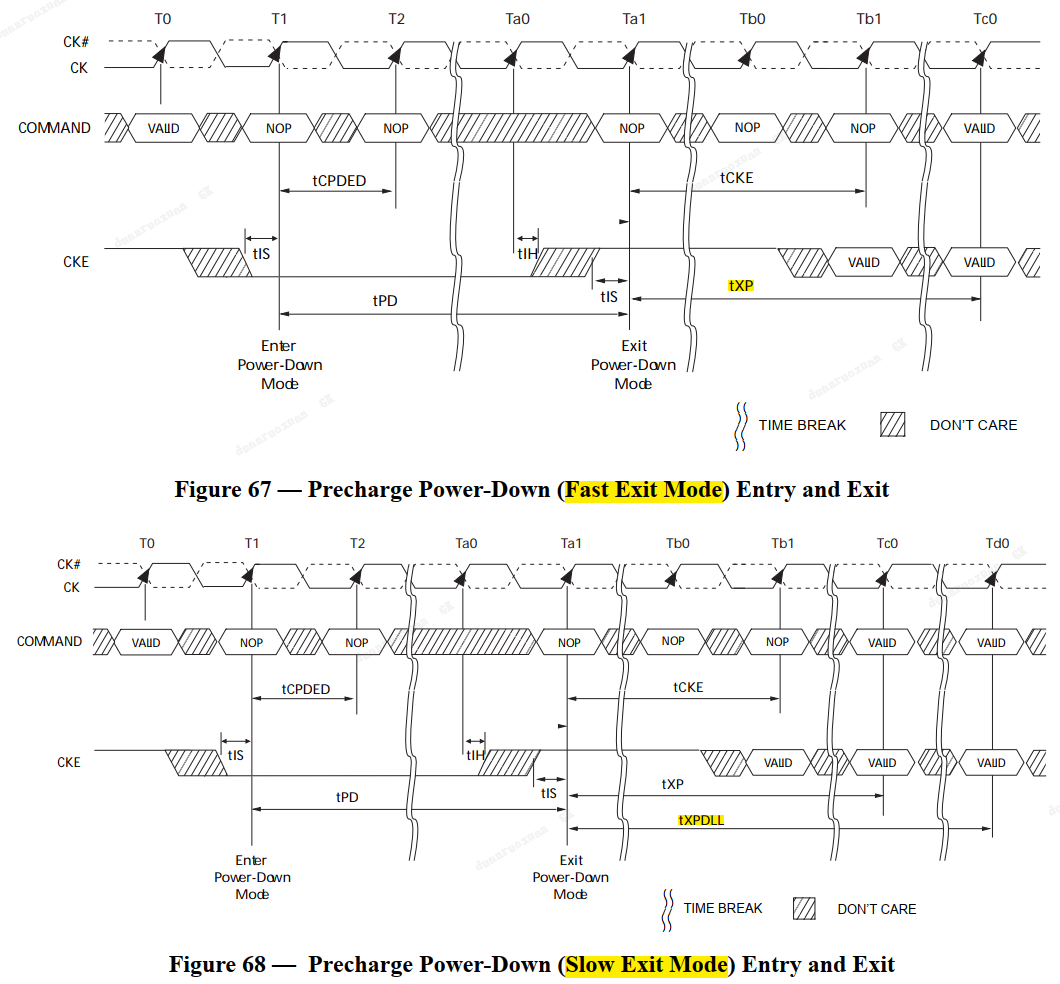

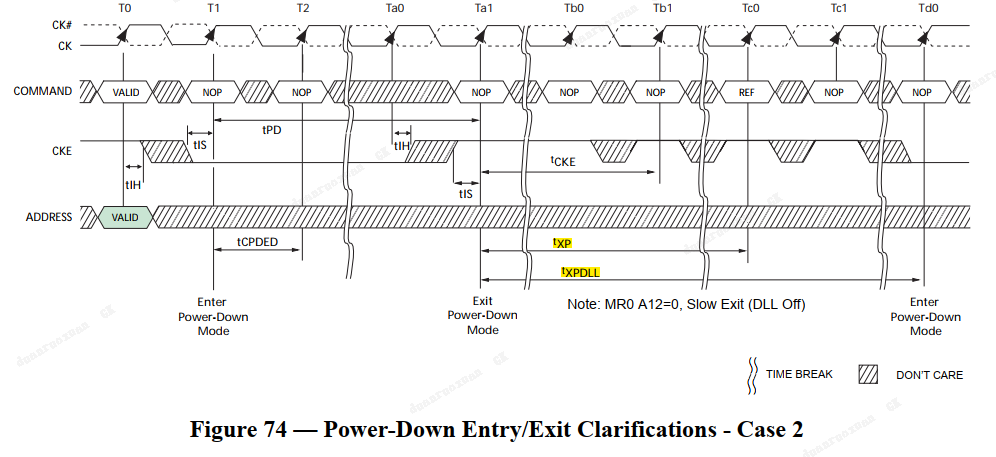

MR0(位A12)用于在预充power-down模式期间选择DLL的使用。当MR0(A12=0)或“slow-exit”时,DLL在进入预充power-down(为了潜在的节能)后被冻结,退出时要求在下一个有效命令之前满足tXPDLL。当MR0(A12=1)或“fast-exit”时,DLL在进入预充power-down后保持不变,退出power-down后需要在下一个有效命令之前满足tXP。

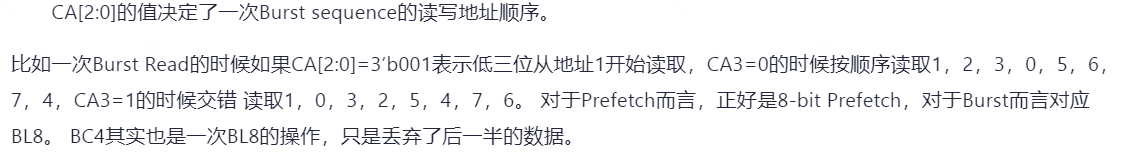

3.4.2模式寄存器MR1

模式寄存器MR1存储用于启用或禁用DLL、输出驱动器强度、Rtt_Nom阻抗、附加延迟、写均衡使能、TDQS使能和Qoff的数据。通过在CS#、RAS#、CAS#、WE#上拉低,在BA0上拉高,在BA1和BA2上拉低来写入模式寄存器1,同时根据图10控制地址引脚的状态。

3.4.3.1预充PD DLL

必须使能DLL才能正常运行。在上电初始化期间以及不使能DLL后恢复正常操作时,都需要使能DLL。

MR1(A0=0),DLL在进入自刷新操作时自动禁用,在退出自刷新操作后自动重新启用。每当启用DLL并随后复位时,tDLLK时钟周期必须发生,然后才能发出读取或同步ODT命令,以便有时间使内部时钟与外部时钟同步。未能等待同步发生可能会导致违反tDQSCK、tAON或tAOF参数。在tDLLK期间,CKE必须持拉高。DDR3 SDRAM不需要DLL进行任何写入操作,除非启用了RTT_WR并且需要DLL进行正确的ODT操作。

在DLL关闭模式下不支持直接ODT功能。在DLL关闭模式期间,必须通过ODT拉低和/或通过模式寄存器设置命令将RTT_Nom位MR1{A9、A6、A2}编程为{0,0,0}来禁用ODT resistors 。

动态ODT功能在DLL关闭模式下不受支持。用户必须使用MRS命令设置Rtt_WR,MR2{A10,A9}={0,0},以从外部禁用动态ODT。

3.4.3.2输出阻抗控制

DDR3 SDRAM设备的输出阻抗由MR1(位A1和A5)选择,如图所示10所示。

3.4.3.3ODT Rtt值

DDR3 SDRAM能够提供两个不同的终止值(Rtt_Nom和Rtt_WR)。名义终止值Rtt_Nom在MR1中编程。可以在MR2中编程单独的值(Rtt_WR),以在写入期间启用ODT时启用唯一的Rtt值。即使禁用Rtt_Nom,也可以在写入期间应用Rtt_WR值。

3.4.3.4附加延时

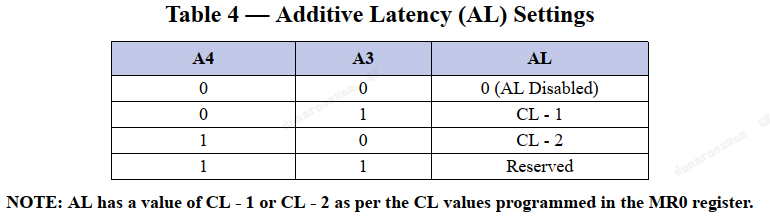

支持加延迟(AL)操作,以使命令和数据总线在DDR3 SDRAM中高效地实现可持续带宽。在这种操作中,DDR3 SDRAM允许在有效命令后立即发出读取或写入命令(有或没有自动预充)。在设备内部发出命令之前,该命令会被保留一段附加延迟(AL)时间。读取延迟(RL)由AL和CAS延迟(CL)寄存器设置之和控制。写入延迟(WL)由AL和CAS写入延迟(CWL)寄存器设置之和控制。AL寄存器选项的摘要如表4所示

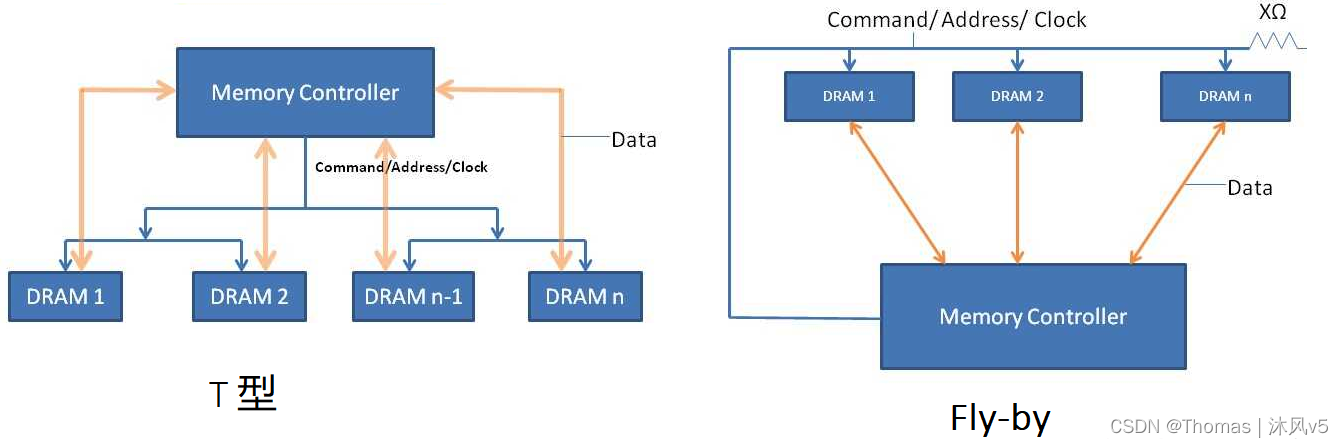

3.4.3.5写均衡

为了更好的信号完整性,DDR3内存模块对命令、地址、控制信号和时钟采用了飞越拓扑。飞越拓扑的优点是减少了短线的数量及其长度,但它也会导致DIMM上每个DRAM的时钟和选通之间的flight time 偏差。这使得控制器难以维护tDQSS、tDSS和tDSH规范。因此,DDR3 SDRAM支持“写均衡”功能,使控制器能够补偿偏斜。

3.4.3.6输出关闭

DDR3 SDRAM输出可以通过MR1(位A12)启用/禁用,如图10所示。当启用此功能时(A12=1),所有输出引脚(DQ、DQs、DQs#等)均与设备断开连接,从而消除了输出driver的任何负载。例如,在测量模块功率时,此功能可能很有用。对于正常工作,A12应设置为“0”。

3.4.3.7TDQS, TDQS#

TDQS(终端数据选通)是X8 DDR3 SDRAM的一个功能,它提供了额外的终端电阻输出,这在某些系统配置中可能很有用。X4或X16配置不支持TDQS。TDQS功能仅在X8 DDR3 SDRAM中可用,对于X4和X16配置,必须通过MR1中的模式寄存器A11=0禁用。

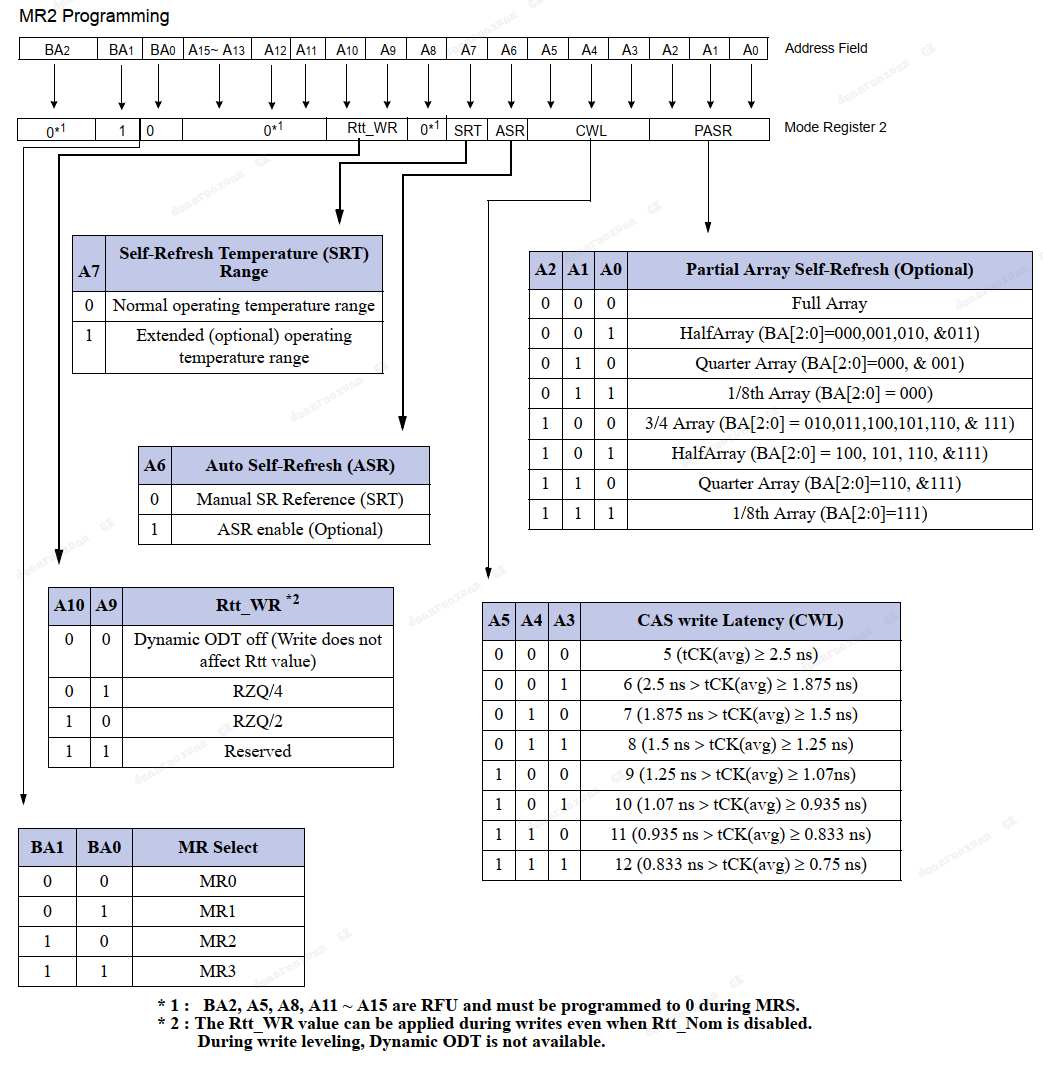

3.4.2模式寄存器MR2

模式寄存器MR2存储用于控制刷新相关特征、Rt_WR阻抗和CAS写入延迟的数据。通过在CS#、RAS#、CAS#、WE#上拉低,在BA1上拉高,在BA0和BA2上拉低来写入模式寄存器2,同时根据下表控制地址管脚的状态:

3.4.4.1部分阵列自刷新(PASR)

DDR3 SDRAM可选:用户应参考DRAM供应商数据表和/或DIMM SPD,以确定DDR3 SDRAM设备是否支持本材料中提到的以下选项或要求。如果启用了PASR(部分阵列自刷新),如果输入自刷新,位于图11所示指定地址范围之外的阵列区(???)域中的数据将丢失。如果满足tREFI条件并且没有发出自刷新命令,则将保持数据完整性。

3.4.4.2CAS写入延迟(CWL)

CAS写入延迟由MR2(位A3-A5)定义,如图11所示。CAS写入延迟是内部写入命令与第一位有效输入数据之间的延迟(以时钟周期为单位)。

3.4.4.3自动自刷新(ASR)和自刷新温度(SRT)

DDR3 SDRAM可选:用户应参考DRAM供应商数据表和/或DIMM SPD,以确定DDR3 SDRAM设备是否支持本材料中提到的以下选项或要求。DDR3 SDRAM必须在所有支持的温度下支持自刷新操作。需要在扩展温度范围内进行自刷新操作的应用程序必须使用可选的ASR功能或适当地配置SRT位。

3.4.4.4动态ODT(Rtt_WR)

DDR3 SDRAM引入了一项新功能“动态ODT”。在某些应用情况下,为了进一步增强数据总线上的信号完整性,希望可以在不发出MRS命令的情况下改变DDR3 SDRAM的终止强度。MR2寄存器位置A9和A10配置动态ODT设置。在写入水平模式下,只有RTT_Nom可用。

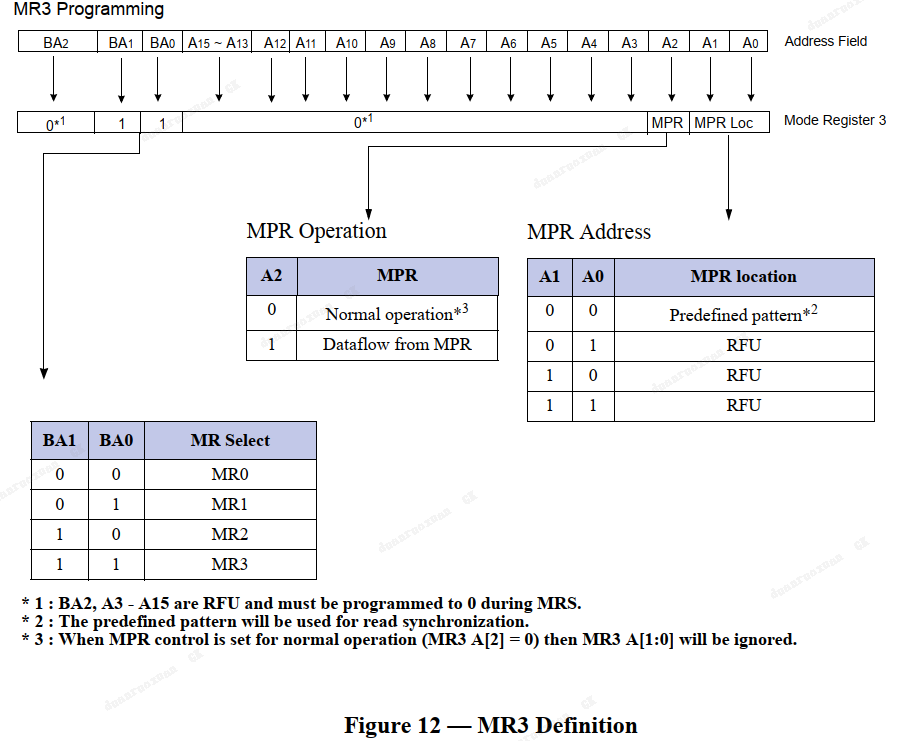

3.4.2模式寄存器MR3

模式寄存器MR3控制多用途寄存器(?)。模式寄存器3通过在CS#、RAS#、CAS#、WE#上拉低、在BA1和BA0上拉高以及在BA2上拉低而写入,同时根据下表控制地址管脚的状态。

3.4.5.1多用途寄存器(MPR)

多用途寄存器(MPR)功能用于读取预定义的系统定时校准位序列。要启用MPR,必须向位A2=1的MR3寄存器发出MODE寄存器集(MRS)命令。在发出MRS命令之前,所有bank必须处于空闲状态(所有bank均已预充且tRP已满足)。一旦启用MPR,任何后续的RD或RDA命令都将被重定向到多用途寄存器。当启用MPR时,只允许RD或RDA命令,直到在禁用MPR的情况下发出后续MRS命令(MR3位A2=0)。在MPR启用模式期间,不允许使用power-down模式、自刷新和任何其他非RD/RDA命令。

4.DDR3 SDRAM命令描述与操作

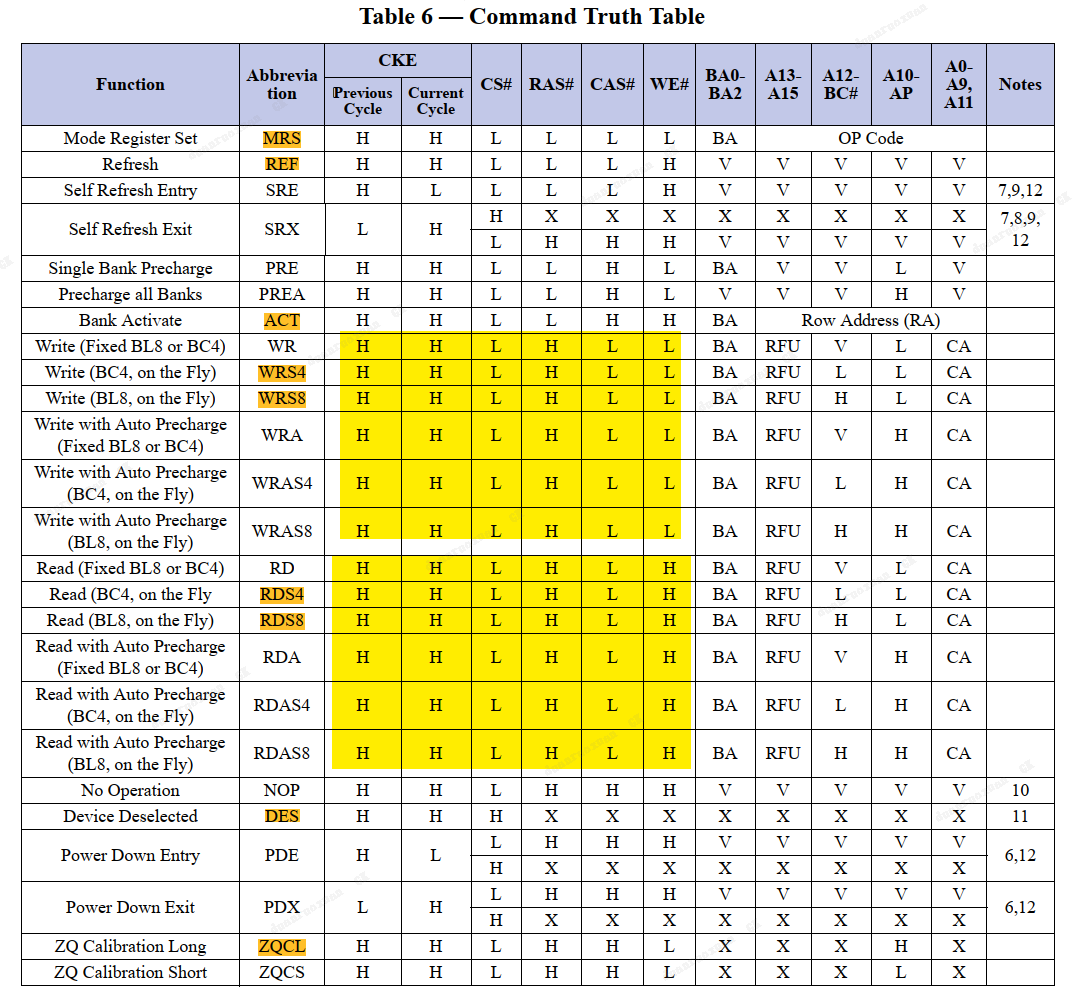

4.1命令真值表

[BA=Bank Address, RA=Row Address, CA=Column Address, BC#=Burst Chop, X=Don’t Care,V=Valid]

- 所有DDR3 SDRAM命令由时钟上升沿的CS#、RAS#、CAS#、WE#和CKE的状态定义。

- 突发读取或写入不能终止或中断,固定/飞行BL模式将由MR0定义

- 低功耗模式不执行任何刷新操作

- ODT的状态不影响此表中描述的状态。ODT功能在自刷新期间不可用。

- 当DDR3 SDRAM处于空闲或等待状态时,应使用No Operation命令。无操作命令(NOP)的目的是防止DDR3 SDRAM在操作之间注册任何不需要的命令。No Operation命令不会终止仍在执行的先前操作,例如突发读写周期。

- 取消选择命令执行与无操作命令相同的功能。

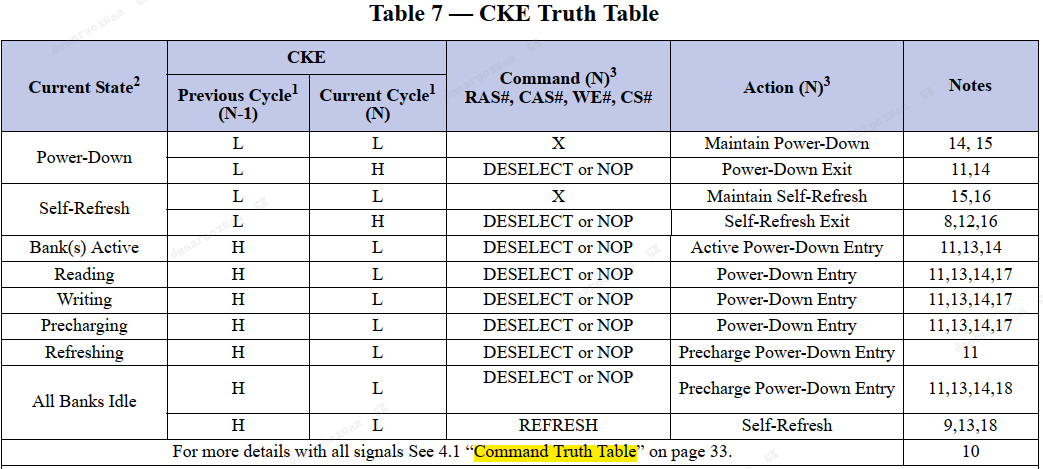

4.2CKE真值表

仅当满足tMRD和tMOD时,才允许CKE低

Ø 仅当满足tMRD和tMOD时,才允许CKE低。

Ø当前状态被定义为DDR3 SDRAM在时钟边沿N之前的状态。

ØCOMMAND(N)是在时钟边沿N处注册的命令,此处不包括ODT。

Ø除非本文档中另有明确说明,否则所有未显示的状态和序列都是非法的或保留的。

Ø自刷新模式只能从所有银行bank状态进入。

Ø断电进入和退出的有效命令仅为NOP和DESELECT。

Ø自刷新退出的有效命令仅为NOP和DESELECT。

4.3无操作(NOP)命令

无操作(NOP)命令用于指示所选的DDR3 SDRAM执行NOP(CS#LOW和RAS#、CAS#和WE#HIGH)。这可以防止在空闲或等待状态下寄存不需要的命令。正在进行的操作不受影响。

4.4取消选择(DES)命令

取消选择功能(CS#HIGH)可防止DDR3SDRAM执行新命令。DDR3 SDRAM被有效取消选择。正在进行的操作不受影响

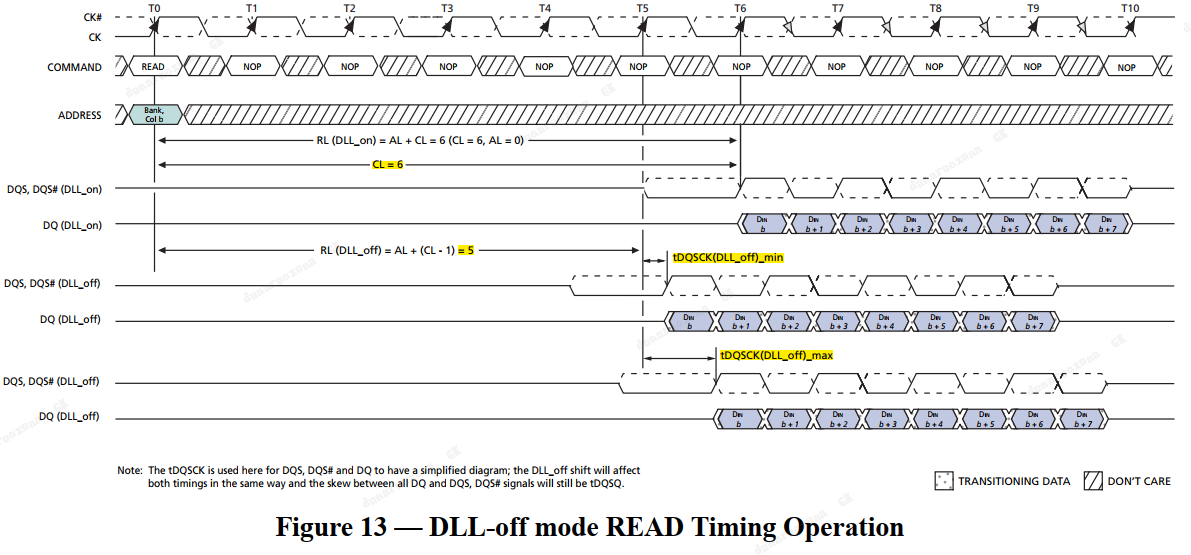

4.5DLL关闭模式

通过将MR1位A0设置为“1”进入DDR3 DLL关闭模式;这将禁用DLL以进行后续操作,直到A0位设置回“0”。用于DLL控制的MR1 A0位可以在初始化期间或以后切换。

下面列出的DLL关闭模式操作是DDR3的可选功能。DLL关闭模式的最大时钟频率由参数tCKDLL_off指定。除了需要满足刷新间隔tREFI外,没有最小频率限制。

由于延迟计数器和定时限制,MR0中仅支持一个CAS延迟(CL)值,MR2中仅支持一个CAS写入延迟(CWL)值。DLL关闭模式仅需要支持CL=6和CWL=6的设置。

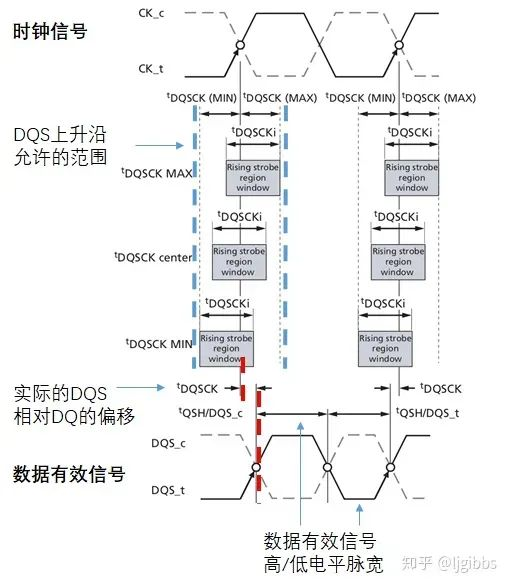

DLL关闭模式将影响读取数据时钟(read命令处?)与数据选通的关系(tDQSCK),但不会影响数据选通与数据的关系(tDQSQ,tQH)。需要特别注意将读取数据与控制器时域对齐。

与DLL开启模式相比,其中tDQSCK从读取命令后的上升时钟沿(AL+CL)周期开始,DLL关闭模式tDQSCK在读取命令后(AL+CL-1)周期开始。另一个区别是,与tCK相比,tDQSCK可能不小(甚至可能大于tCK),tDQSCKmin和tDQSCKmax之间的差异明显大于DLL开启模式下的差异。tDQSCK(DLL_off)值因供应商而异。

DLL关闭模式READ操作的时序关系如下图所示(CL=6,BL=8):

tCK:时钟周期(tclock)

4.6DLL开关步骤

通过将MR1位A0设置为“1”进入DDR3 DLL关闭模式;这将禁用DLL以进行后续操作,直到A0位设置回“0”。

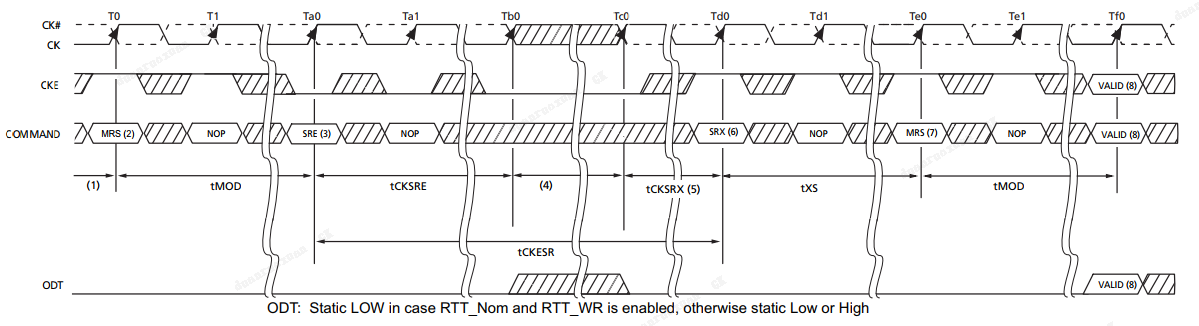

4.6.1DLL“打开”到DLL“关闭”的过程

要从DLL“打开”切换到DLL“关闭”,需要在自刷新期间更改频率,如以下过程所述:

- 从空闲状态开始(在MRS到MR1之前,所有bank都已预充,所有时序都已完成,DRAM ODT电阻和RTT(?)必须处于高阻态,以禁用DLL。)

- 将MR1位A0设置为“1”以禁用DLL

- 等待tMOD

- 进入自刷新模式;等待直到满足(tCKSRE)。

- 改变频率

- 等待DRAM输入端至少(tCKSRX)有稳定的时钟。

- 从自刷新退出命令开始,CKE必须连续为高,直到满足任何MRS命令的所有tMOD时序。此外,如果在进入自刷新模式时在模式寄存器中启用了任何ODT功能,则ODT信号必须连续为低,直到满足任何MRS命令的所有tMOD时序。如果在进入自刷新模式时,模式寄存器中的两个ODT功能都被禁用,则ODT信号可以为低或高。

- 等待tXS,然后用适当的值设置模式寄存器(特别是可能需要更新CL、CWL和WR。tXS后也可能发出ZQCL命令)

- 等待tMOD,然后DRAM准备好执行下一个命令。

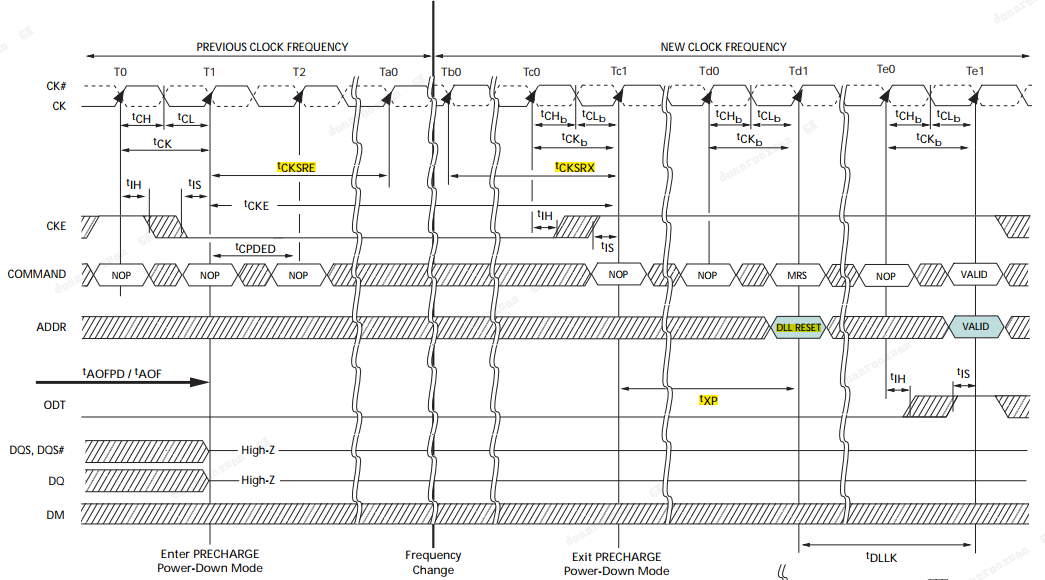

4.7输入时钟频率变化

一旦DDR3 SDRAM初始化,DDR3 SDRAM要求时钟在几乎所有正常操作状态下都是“稳定的”。这意味着,一旦时钟频率被设置并处于“稳定状态”,时钟周期就不允许偏离,除非时钟抖动和SSC(扩频时钟)规范允许。

在两种情况下,输入时钟频率可以从一个稳定的时钟频率更改为另一个稳定时钟频率:(1)自刷新模式和(2)预充断电模式。在这两种模式之外,更改时钟频率是违法的

对于第一种情况,一旦DDR3 SDRAM成功地进入自刷新模式并且满足tCKSRE,时钟的状态就会变为无所谓。一旦不在乎,只要新的时钟频率在tCKSRX之前稳定,就可以更改时钟频率。当仅为了更改时钟频率而进入和退出自刷新模式时,仍必须满足自刷新进入和退出规范。DDR3 SDRAM输入时钟频率仅允许在为指定的最小和最大工作频率内变化。任何低于最低工作频率的频率变化都需要使用DLL-on-mode->DLL_off模式转换顺序。

第二种情况是DDR3 SDRAM处于预充断电模式(快速退出模式或慢速退出模式)。如果在进入预充断电模式之前在模式寄存器中启用了RTT_NOM功能,则ODT信号必须连续为低,以确保RTT处于关闭状态。如果在进入预充断电模式之前,模式寄存器中的RTT_NOM功能被禁用,RTT将保持关闭状态。在这种情况下,ODT信号可以被为低或高。在CKE变低后,时钟频率可能发生变化之前,必须保持至少最小的tCKSRE。在输入时钟频率变化期间,ODT和CKE必须保持在稳定的低电平。一旦输入时钟频率改变,在退出预充断电之前,必须向DRAM tCKSRX提供稳定的新时钟;在退出预充断电且tXP到期后,必须通过MRS重置DLL。根据新的时钟频率,可能需要发出额外的MRS命令,以适当地设置WR、CL和CWL,同时CKE持续为高。在DLL重新锁定期间,ODT必须保持低电平,CKE必须保持高电平。在DLL锁定时间之后,DRAM准备好以新的时钟频率运行。

4.8Write Leveling

为了更好的信号完整性,DDR3内存模块对命令、地址、控制信号和时钟采用fly-by拓扑。fly-by拓扑从减少布线长度方面有好处,但它也会导致DIMM上每个DRAM的clock和strobe之间的时间偏差。这使得控制器难以维护tDQSS、tDSS和tDSH规范。因此,DDR3 SDRAM支持“write leveling”功能,允许控制器补偿skew。

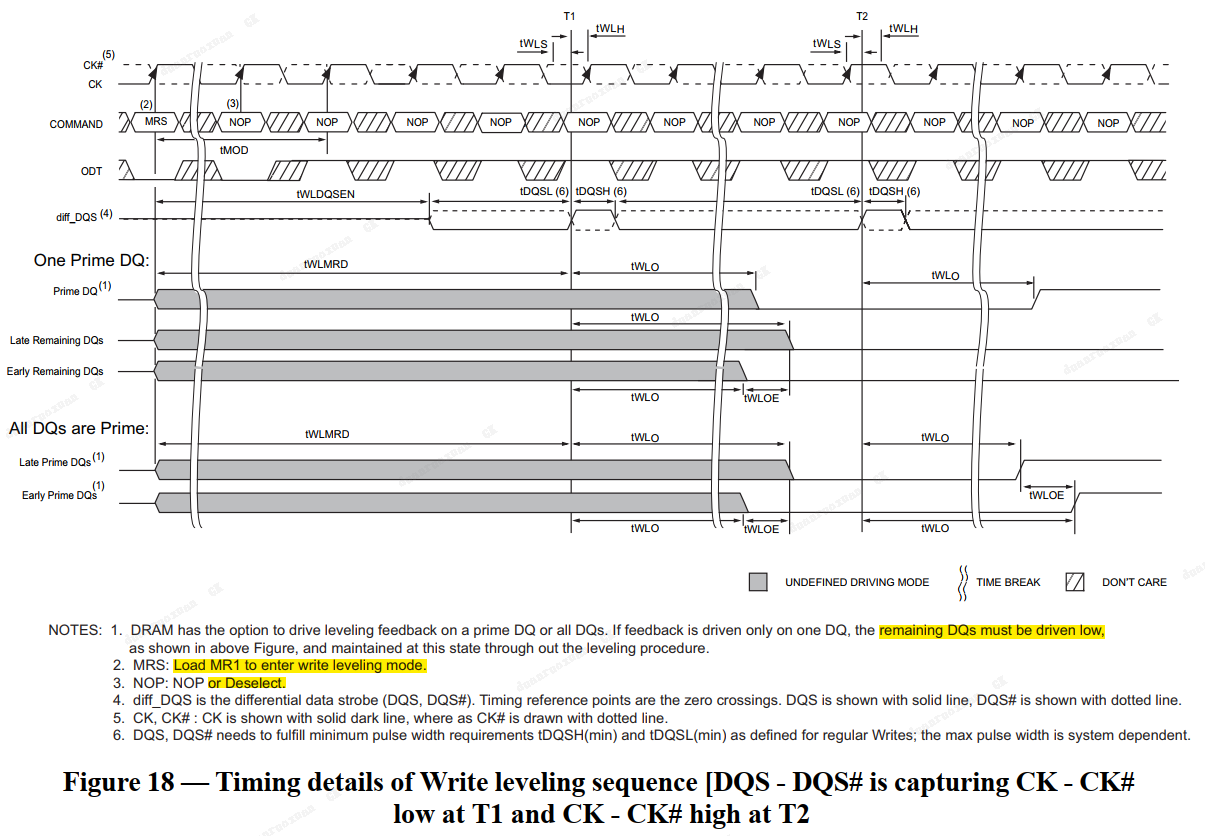

存储器控制器可以使用“写均衡”功能和来自DDR3 SDRAM的反馈来调整DQS-DQS#到CK-CK#的关系。参与调平的存储器控制器必须在DQS-DQS#上具有可调延迟设置,以使DQS-DQS#的上升沿与DRAM引脚处的时钟的上升沿对齐。DRAM通过DQ总线异步反馈CK-CK#,并用DQS-DQS#的上升沿采样(采样CK值,用DQ输出)。控制器反复延迟DQS-DQS#,直到检测到从0到1的转换。通过此法建立的DQS-DQS#延迟将确保tDQSS规范。除了tDQSS,tDSS和tDSH规范也需要满足。实现这一点的一种方法是将应用中的实际tDQSS与DQS-DQS#信号上的适当占空比和抖动相结合。根据应用中的实际tDQSS,tDQSL和tDQSH的实际值可能必须优于“交流定时参数”一章中提供的绝对限值,以满足tDSS和tDSH规范。

源端同步发送的时钟信号 CK 和数据有效信号 DQS 在接收端出现了偏差,一般来说时钟信号会更滞后一些。从 DRAM 端返回的 DQ 值为 0,表示 DQS 上升沿时 CK 信号为低电平。源端 MC 根据 DQ 数值,继续加大 DQS 的延迟,直至 DQ 值为 1,此时 DQS 上升沿时 CK 信号为高电平。再略微将延迟调小,MC 就捕捉到了 CK 的上升沿,记录此时的 DQS 延迟值,就完成了 DQS (数据)与 CK 的同步。

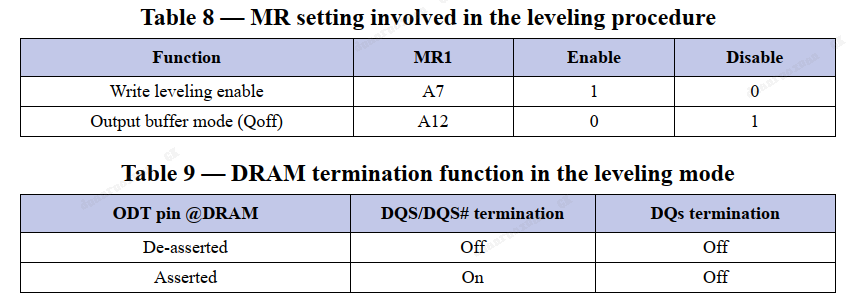

4.8.1该模式下写均衡和DRAM终止功能的DRAM配置

如果MR1中的A7设置为“高”,DRAM将进入写均衡模式,完成均衡后,如果MR1中将A7设置为低,DRAM将退出写均衡模式(表8)。在写均衡模式下,与正常操作不同,只有DQS/DQS#管脚通过ODT启用和停用(表9)。

4.8.2过程描述

存储器控制器通过将MR1的位7设置为1来启动所有DRAM的均衡模式。当进入写均衡模式时,DQ引脚处于未定义(x态?)的驱动模式。在写均衡模式期间,只允许NOP或DESELCT命令,以及更改Qoff位的MRS命令(MR1[A12])和退出写均衡的MRS命令。在退出写均衡模式时,执行退出的MRS命令(MR1[A7]=0)还可以改变A12-A11、A9、A6-A5和A2-A1的MR1比特。由于控制器一次对一个列进行分级,因此必须通过将MR1位A12设置为1来禁用其他列的输出。控制器可以在tMOD之后断言ODT,此时DRAM准备好接受ODT信号。

在tWLDQSEN的延迟之后,控制器可以驱动DQS低电平和DQS#高电平,此时DRAM已经对这些信号施加ODT。在tDQSL和tWLMRD之后,控制器提供一个DQS,DQS#边沿,DRAM使用该边沿对控制器驱动的CK-CK#进行采样。tWLMRD(最大)定时取决于控制器。

DRAM使用DQS-DQS#的上升沿对CK-CK#状态进行采样,并在tWLO后异步提供所有DQ位的反馈。在第一次采样过程之后,DRAM的剩余DQ位被静态地置为低。一旦检测到0到1的转换,控制器就会锁定DQS-DQS#延迟设置,并为设备实现写均衡。

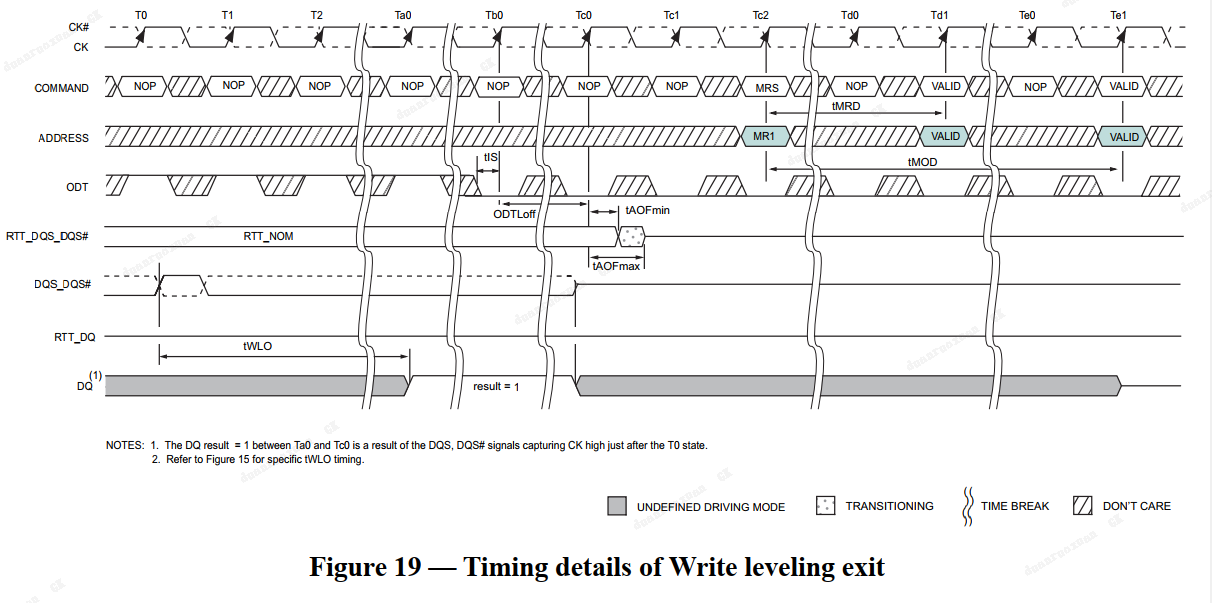

4.8.3写均衡的退出

- 在最后一个上升的选通边沿(T0)之后,停止驱动选通信号(Tc0)。注意:从现在开始,DQ引脚处于x态,并将保持,直到相应MR命令(Te1)后的tMOD。

- 驱动ODT引脚为低电平(必须满足tIS??),并保持为低电平。(见Tb0)

- 关闭RTT后,通过MRS命令禁用写均衡模式(参见Tc2)

- 在满足tMOD(Te1)后,可以寄存任何有效的命令。(MR命令可能在tMRD(Td1)之后发出)

4.9延长温度使用(用处不大)

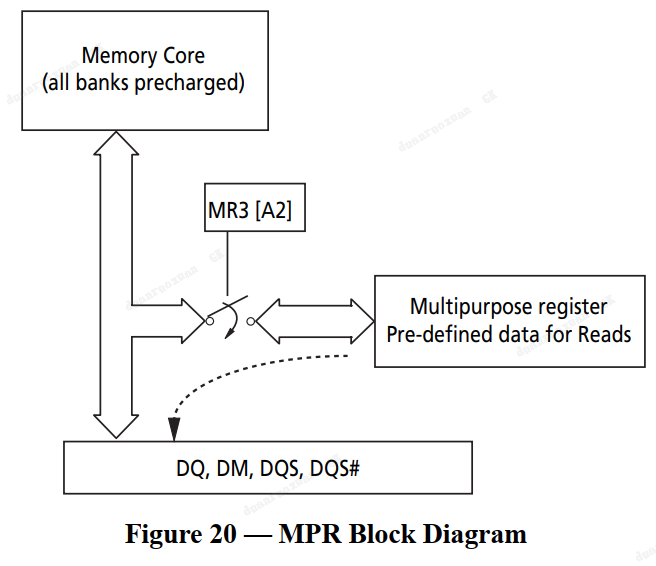

4.10多用途寄存器

多用途寄存器(MPR)功能用于读取预定义的系统定时校准位序列(?)。

Read 时,需要将 DQ 的判定 High/Low 的电压设定在一个理想的值,MPR操作时,读取的数据从寄存器给出,可以避免 cell 问题导致读取数据错误,MPR 就是进行 Read 时 DQ 数据线的 training,确保后续的读写可以正常进行。

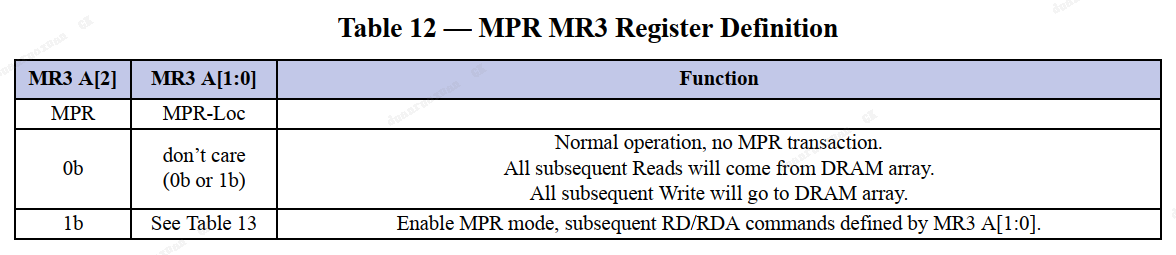

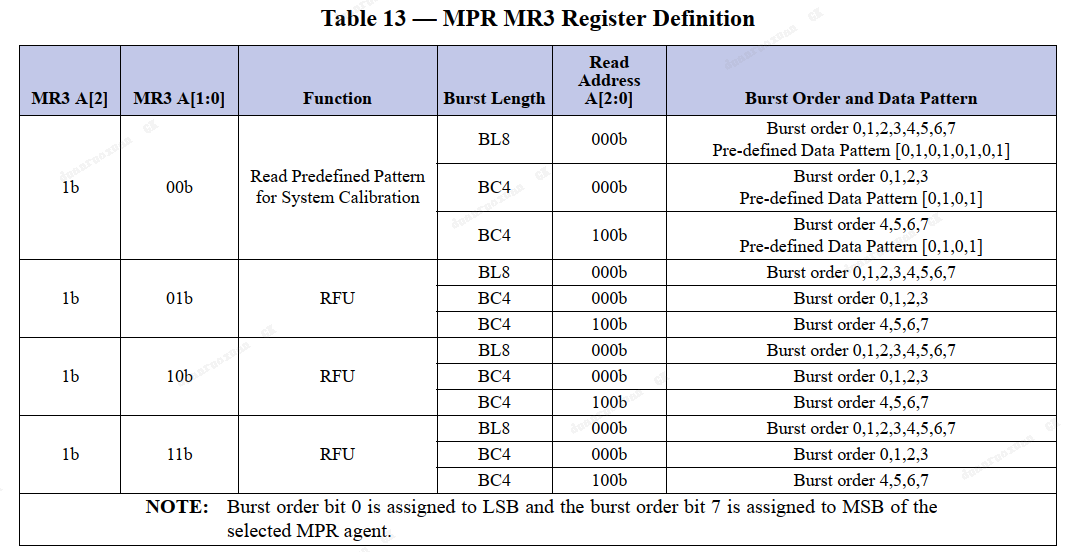

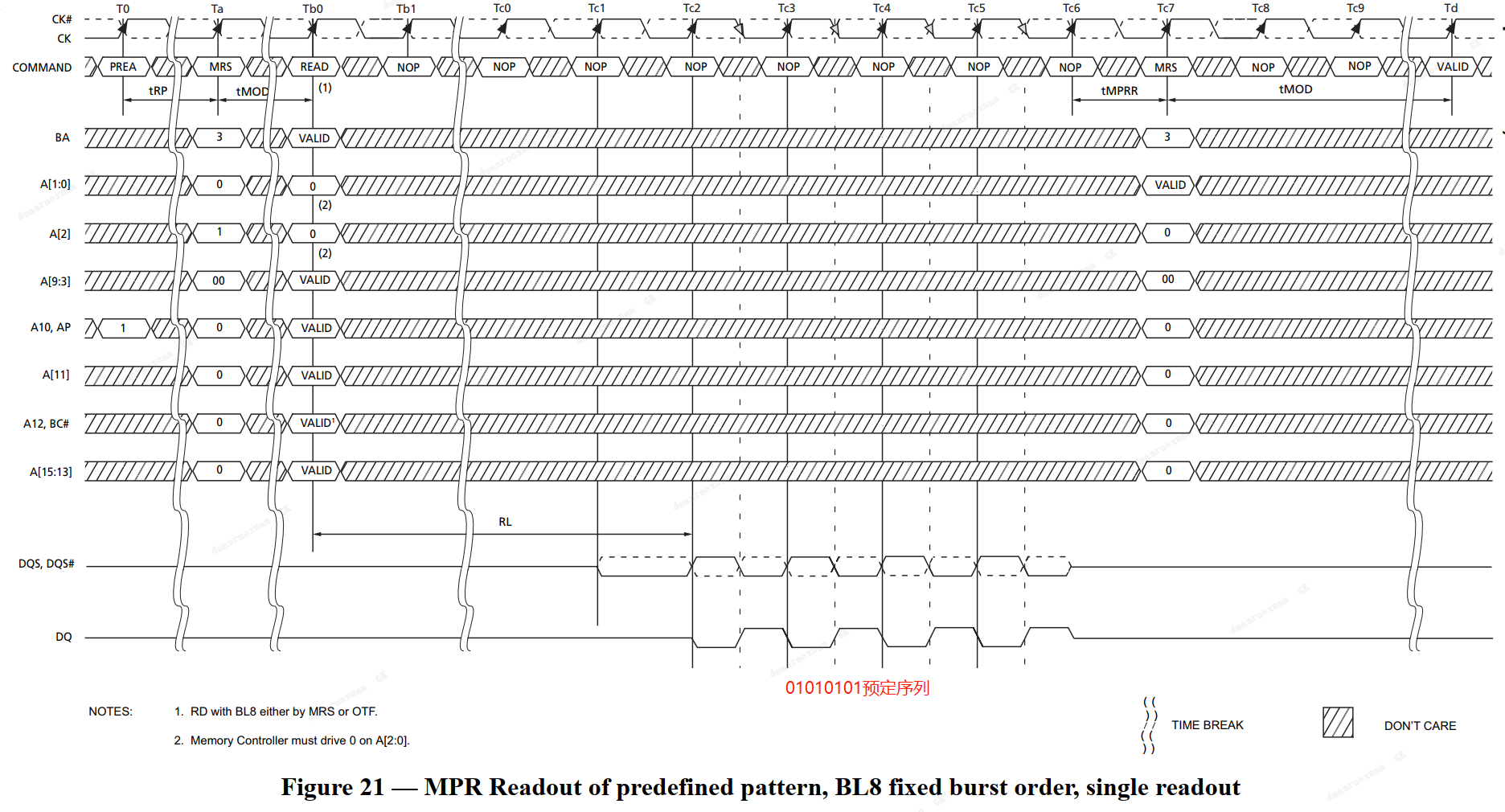

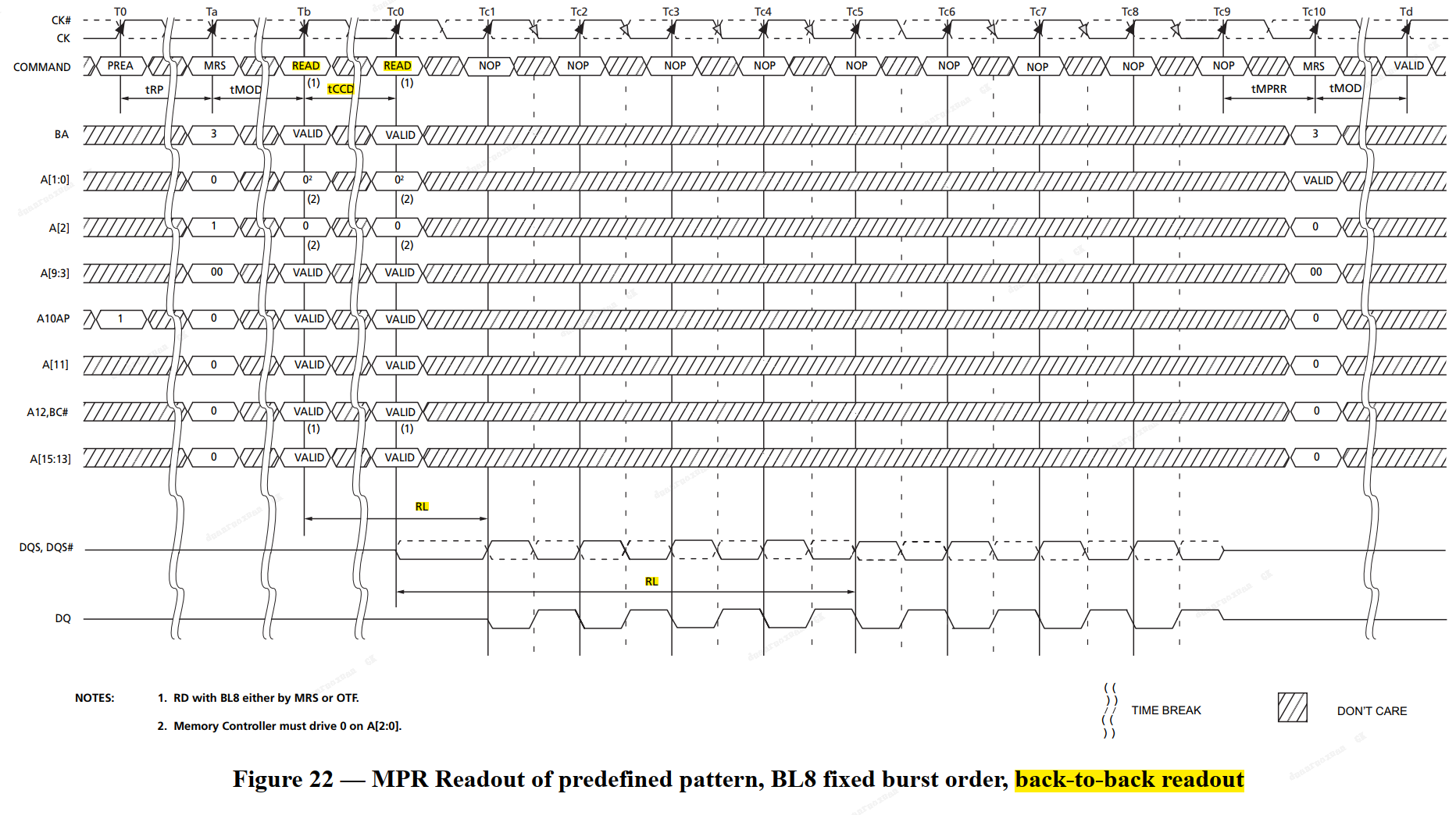

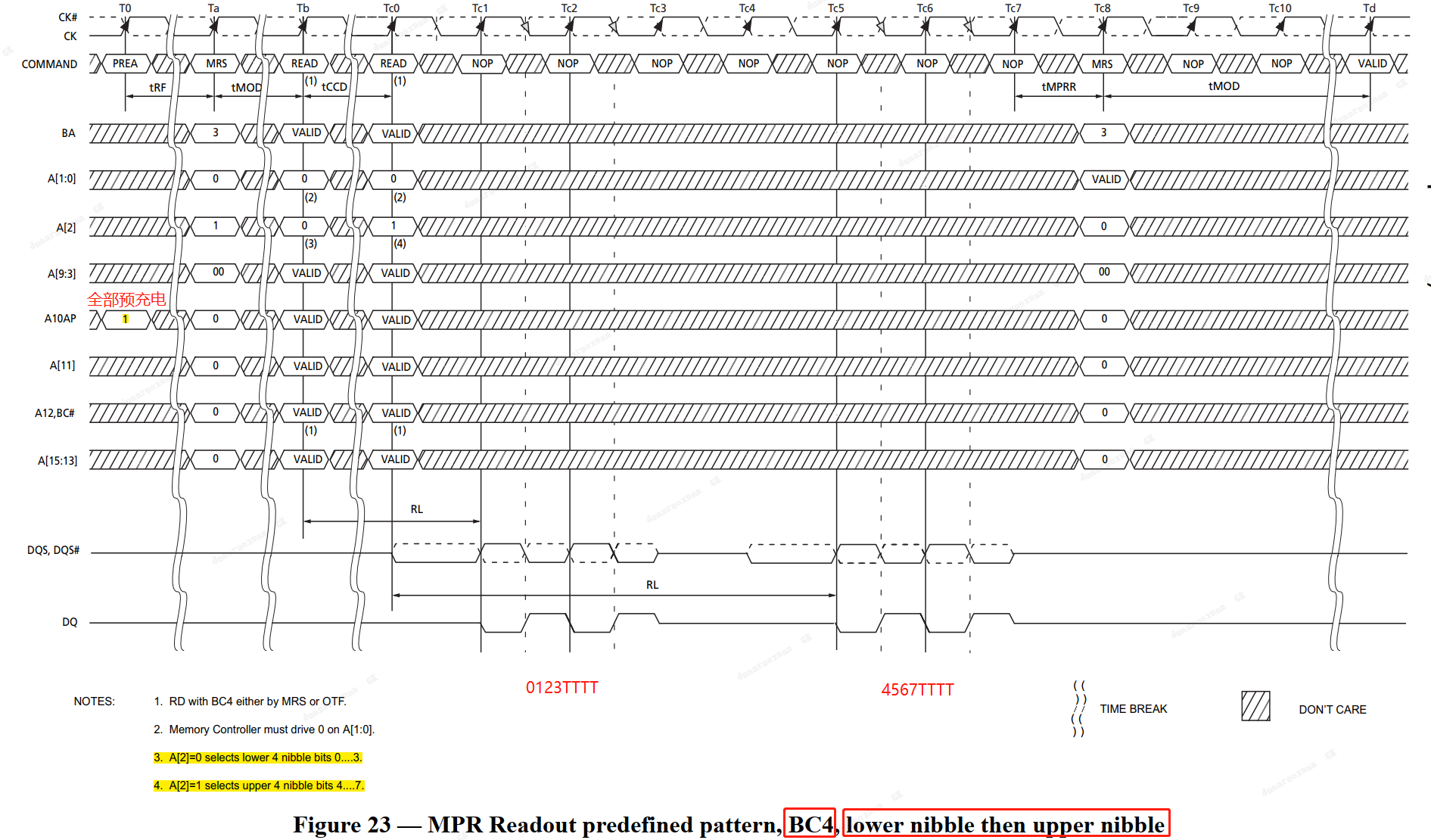

为了启用MPR,必须向MR3寄存器位A2=1发出MODE寄存器集(MRS)命令,如表12所示。在发出MRS命令之前,所有bank必须处于空闲状态(所有bank均已预充且tRP已满足)。一旦启用MPR,任何后续的RD或RDA命令都将被重定向到多用途寄存器。当发出RD或RDA命令时,结果操作由启用MPR时的MR3位a[1:0]定义,如表13所示。当启用MPR时,只允许RD或RDA命令,直到在禁用MPR的情况下发出后续MRS命令(MR3位A2=0)。注意,在MPR模式下,RDA具有与READ命令相同的功能,这意味着RDA的自动预充电部分被忽略。在MPR启用模式期间,不允许使用power-down模式、自刷新和任何其他非RD/RDA命令。MPR启用模式期间支持RESET功能。

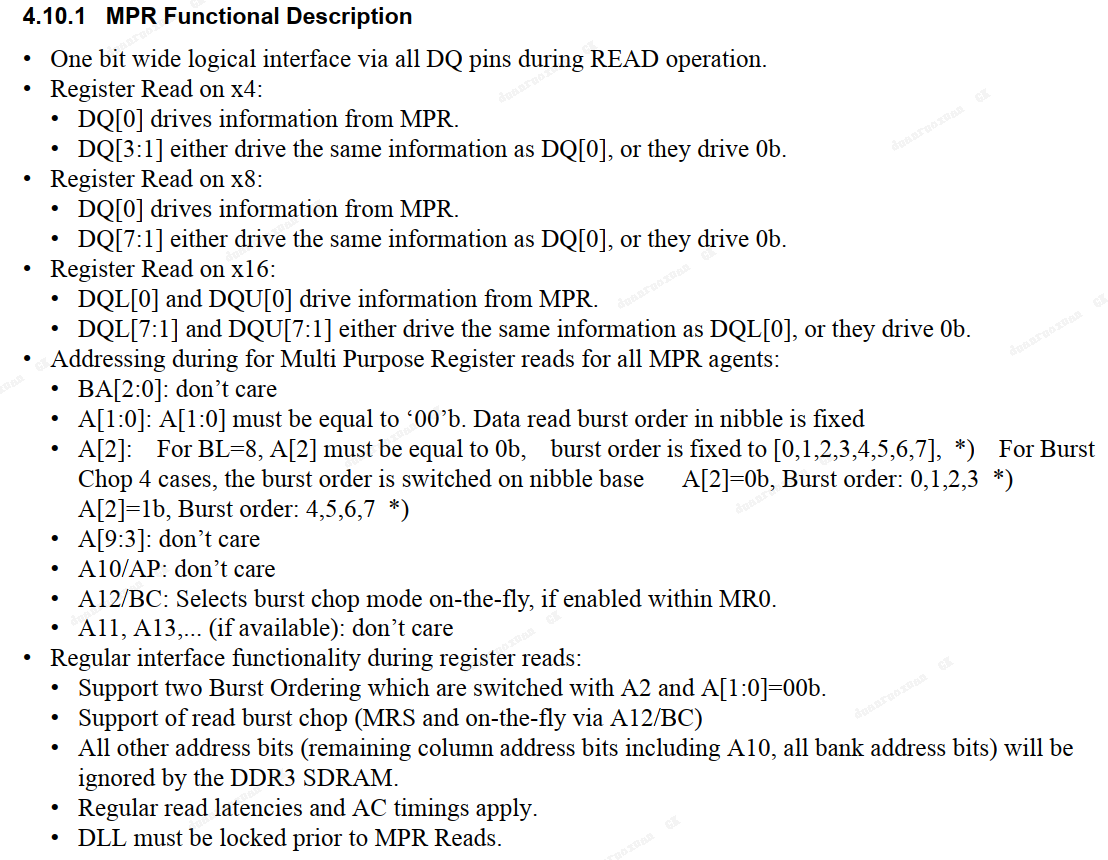

4.10.1MPR功能描述

4.10.2MPR寄存器地址定义

表13提供了可用数据位置的概述,MR3 A[1:0]在MRS到MR3期间如何寻址这些位置,以及在多用途寄存器读取期间如何将它们的各个位映射到突发顺序位。

4.10.3协议示例

读取预定的读取校准模式。(从多用途寄存器进行多次读取,以便根据预定和标准化的模式进行系统级读取定时校准)

协议步骤:

- 全部预充电。

- 等待tRP满足要求。

- MRS MR3, Opcode “A2 = 1b“ and “A[1:0] = 00b“

- 等待tMRD和tMOD满足要求(然后准备读取多用途寄存器)。在MR3 A2=1期间,不允许进行数据写入操作

- 读操作:

- A[1:0]='00'b(数据突发顺序从半字节开始是固定的,这里总是00b)

- A2='0b

- A12/BC=1(使用常规的8burst length(等于0就chop为四位了))

- 所有其他地址引脚(包括BA[2:0]和A10/AP):不关心

- 在RL=AL+CL之后,DRAM会读出预定义的读取校准模式。

- 存储器控制器重复这些校准读取,直到存储器控制器处的读取数据捕获得到优化

- 在最后一个MPR读取脉冲串结束后,等待tMPRR得到满足。

- MRS MR3,操作码“A2=0b”和“A[1:0]=有效数据,但值无关紧要”(所有后续的读写访问都将是DRAM阵列的常规读写操作)

- 等待tMRD和tMOD满足要求。

- 继续执行“常规”DRAM命令,例如激活存储体进行常规读写访问。

4.11激活命令

ØACTIVE命令用于激活特定bank中的行,以便后续访问。

ØBA0-BA2输入上的值选择bank,输入A0-A15上提供的地址选择行。

Ø在向该bank发出预充电命令之前,此行对访问保持激活(或打开)状态(可读写访问)。

Ø在打开同bank中的不同行之前,必须发出PRECHARGE命令。

4.12预充电命令

PRECHARGE命令用于停用特定存储体中的open row(??)或所有存储体中的open row。在发出预充电命令后的指定时间(tRP)内,存储体将可用于后续的行激活。但并发自动预充电的情况除外,在这种情况下,只要不中断当前存储体中的数据传输并且不违反任何其他时序参数,就允许向不同存储体发出读取或写入命令。一旦存储体被预充电,它就处于空闲状态,必须在向该存储体发出任何读取或写入命令之前激活。如果该存储体中没有open row(空闲状态),或者如果之前open row已经在预充电过程中,则允许使用预充电命令。但是,预充电时间将由向存储体发出的最后一个预充电命令决定。

4.13读操作

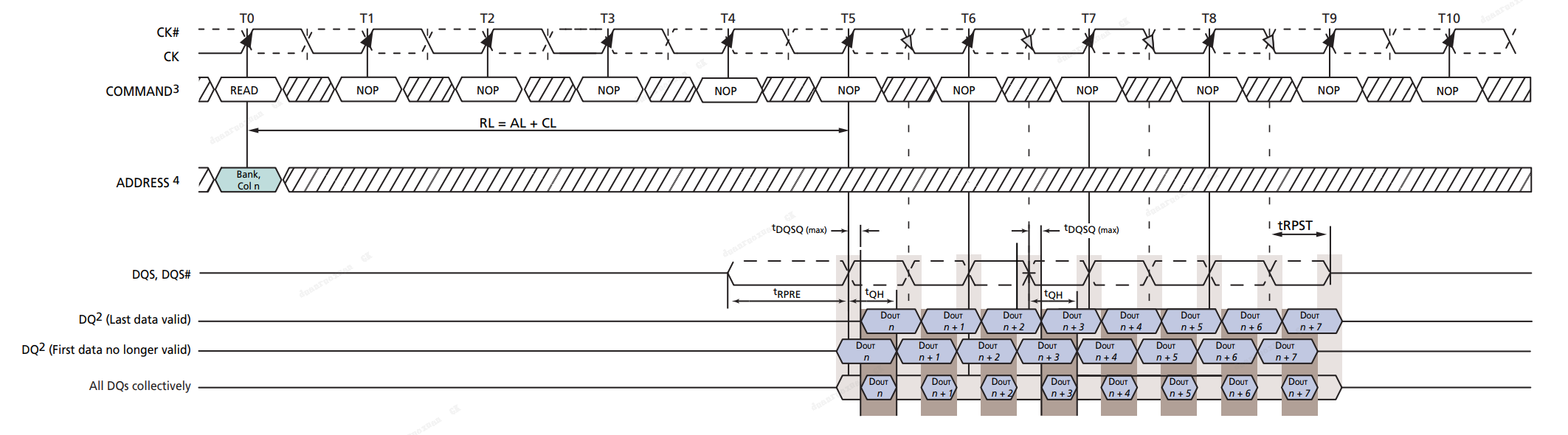

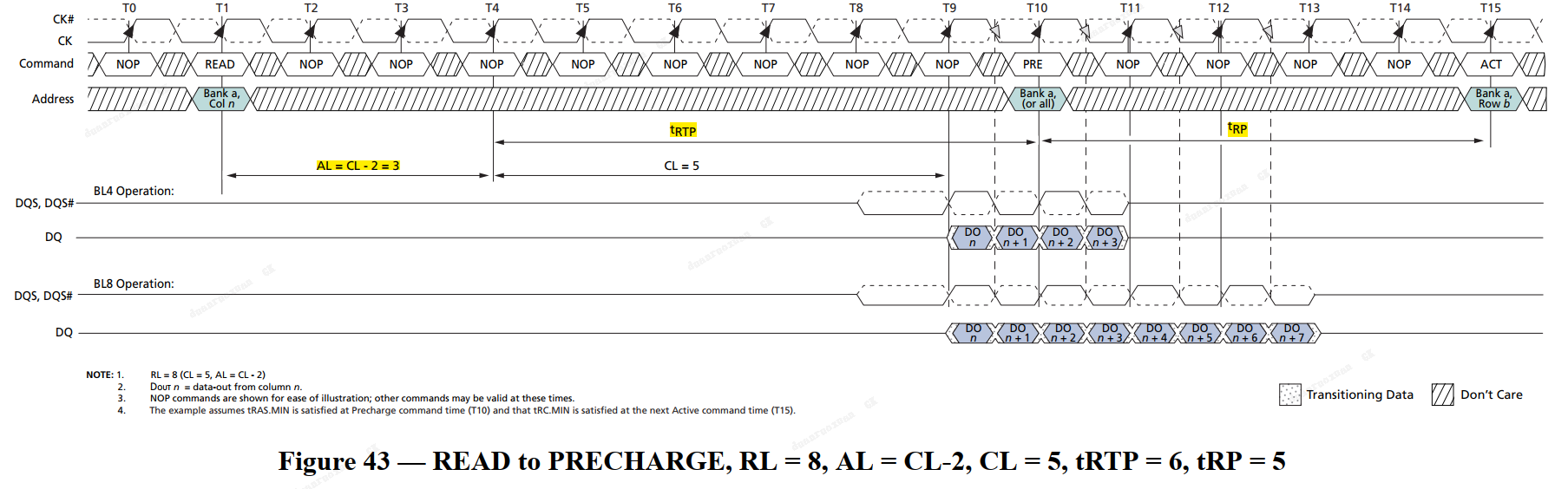

4.13.1读突发操作

DDR3在读或写期间可以使用地址线A12动态支持BC4和BL8(需要在MR0中配置为OTF模式)。可以选择是否在读/写命令后进行预充电。当读写命令期间A10为高则执行RDA/WRA,读写结束后自动进入预充电状态。

A12仅用于突发长度控制,而不是作为列地址。

读操作前后需要tRPRE/tRPST的DQS差分信号的脉冲宽度

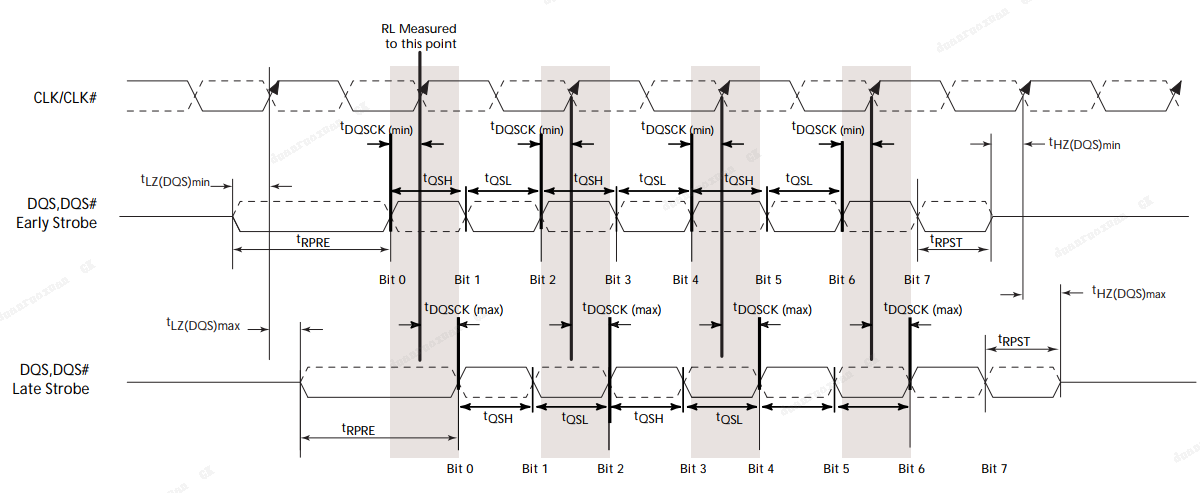

4.13.2读时序

1.tDQSCK(MIN/MAX):DQS信号上升沿相对于时钟信号边沿 所允许的延迟范围。

2.tDQSCK:DQS信号相较于时钟边沿的实际延迟。

3.tQSH:DQS信号高电平脉冲脉宽。

4.tQSL:数据有效信号低电平脉冲脉宽。

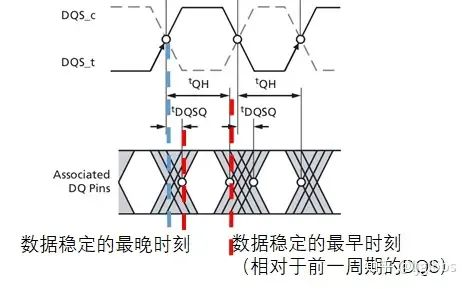

1.tDQSQ:描述 DQ 上升沿相对于 DQS 边沿的最晚时间,晚于该点将影响采样。

2.tQH:描述 DQ 上升沿相对于 DQS 边沿的最早时间,早于该点将影响采样。

tDQSQ:描述 DQ 上升沿相对于 DQS 边沿的最晚时间,(译注,晚于该时刻将影响本次数据采样),在下方的图中可以看到, tDQSQ 指的是 DQS 上升沿至有效 DQ 信号左边沿的时间

tQH:描述 DQ 上升沿相对于 DQS 边沿的最早时间,(译注,早于该时刻将影响前次数据采样),在下方的图中可以看到,tQH 指的是 DQS 上升沿至有效 DQ 信号的右边沿的时间

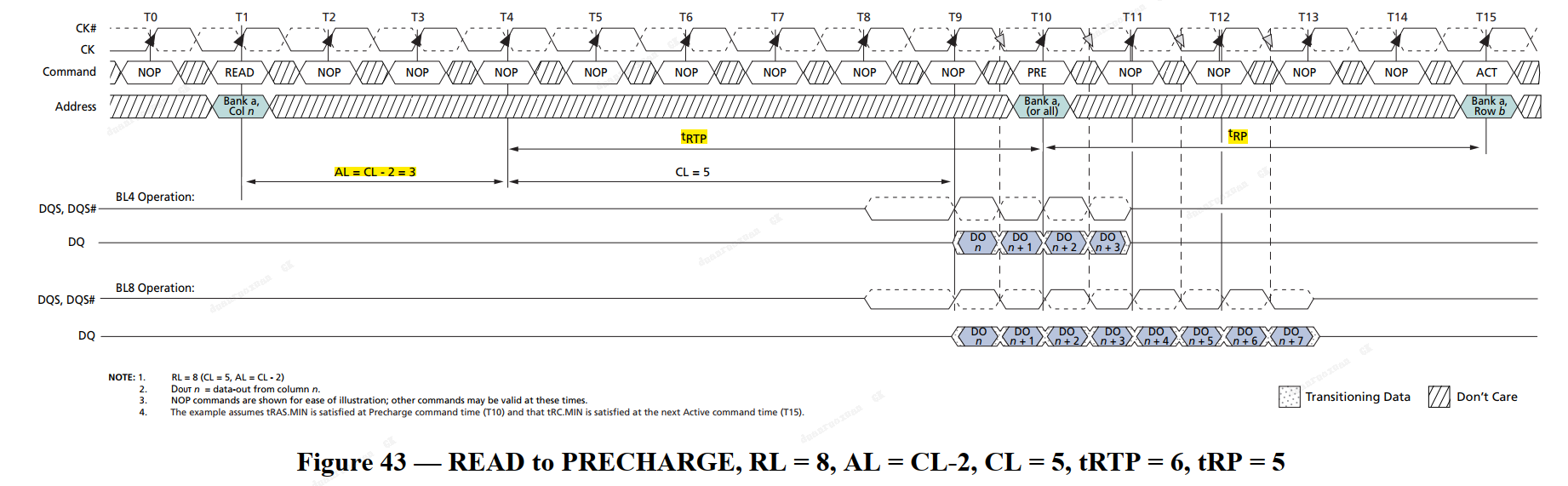

4.13.3预充电后的突发读取操作

4.14写操作

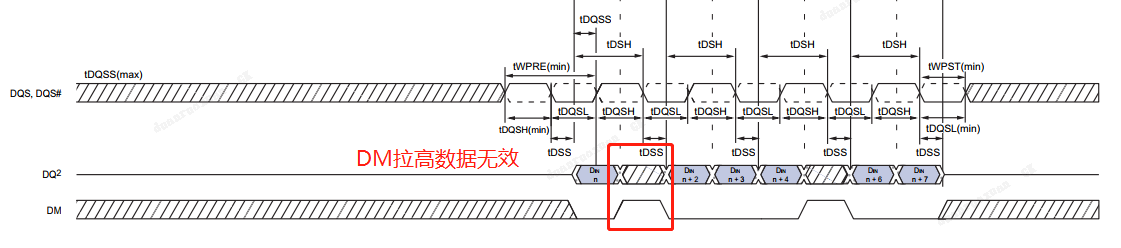

4.14.3写数据掩位

DDR3 SDRAM将支持每8个数据位(DQ)对应一个写数据掩码(DM)引脚。

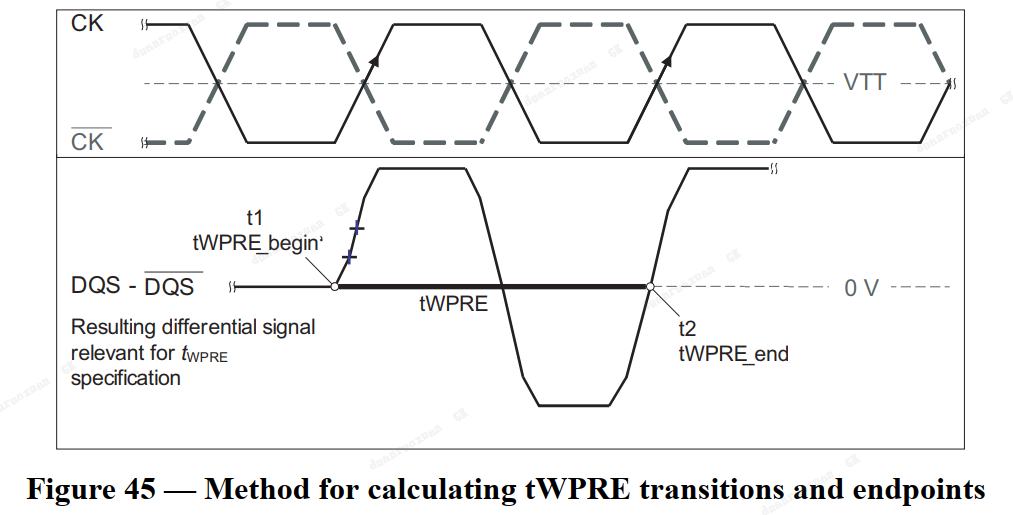

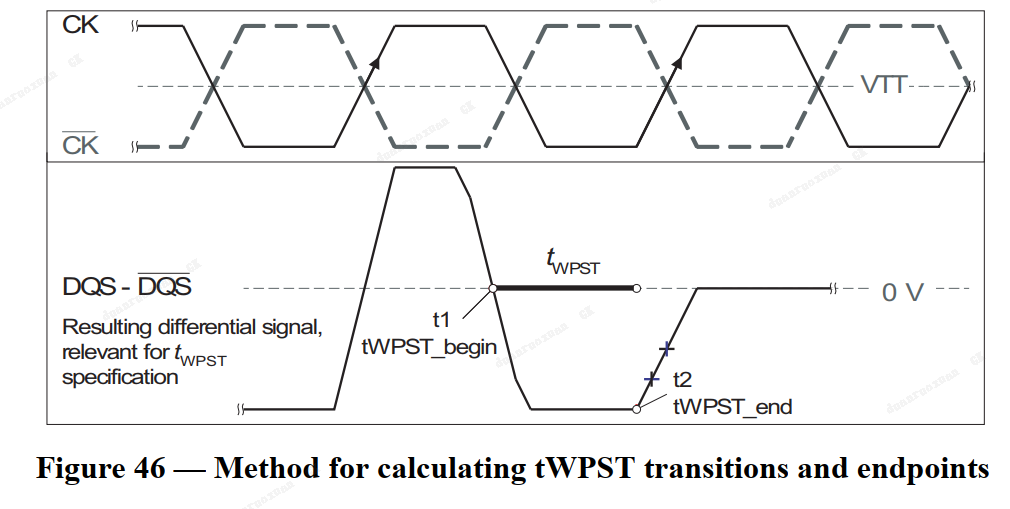

4.14.4tWPRE/tWPST

4.14.5写时序

对于写操作,所有工作频率下都需要一个2tCK时间长度的DQS前置差分工作信号

4.15刷新命令

- tREFW(refresh window):所有的DRAM device都有一个retention time(记忆时间),超过这个时间数据会有误,一般是32/64ms,这个时间窗口内必须把所有row都refresh一次;

- tREFC(refresh command):执行一个refresh command需要的时间;

- tREFI(refresh interval):发送两个refresh命令的间隔时间;

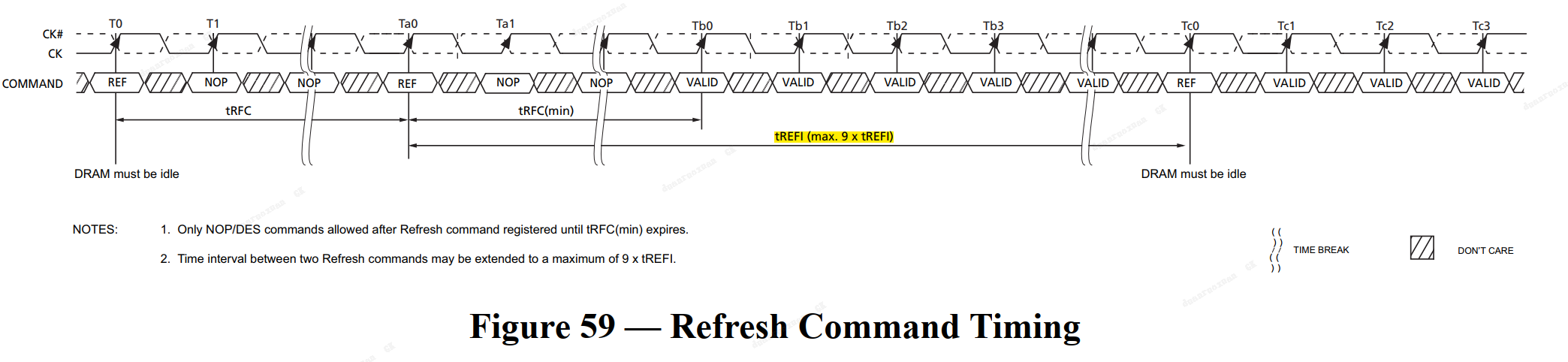

刷新命令(REF)在DDR3 SDRAM正常运行期间使用。此命令是非持久性的,因此每次需要刷新时都必须发出。DDR3 SDRAM要求两个刷新周期的平均周期间隔为tREFI。当CS#、RAS#和CAS#在时钟的上升沿被保持为低并且WE#为高时,芯片进入刷新周期。在使用刷新命令之前,SDRAM的所有存储体必须预充电并空闲至少预充电时间tRP(min)。刷新寻址由内部刷新控制器生成。这使得地址位在刷新命令期间“不重要”。内部地址计数器在刷新周期内提供地址。一旦这个循环开始,就不需要控制外部地址总线。当刷新周期完成时,SDRAM的所有存储体将处于预充电(空闲)状态。刷新命令和下一个有效命令(NOP或DES除外)之间的延迟必须大于或等于最小刷新周期时间tRFC(min),如图59所示。请注意,tRFC定时参数取决于存储器密度。

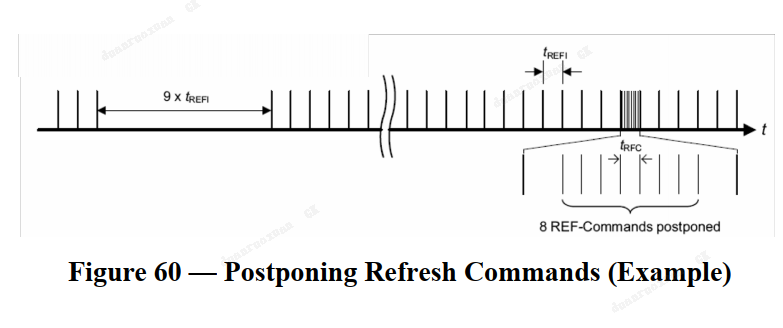

一般来说,每tREFI间隔需要定期向DDR3 SDRAM发出刷新命令。为了提高任务调度和切换的效率,提供了绝对刷新间隔的一些灵活性。在DDR3 SDRAM的操作期间,最多可以推迟8个刷新命令,这意味着在任何时候都不允许推迟超过8个刷新指令。如果连续推迟8个Refresh命令,则相邻Refresh命令之间的最大间隔限制为9×tREFI(见图60)。

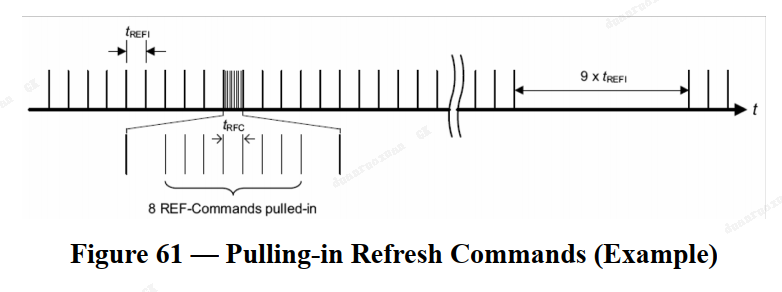

最多可以提前发出8个额外的刷新命令(“pull in”),每个命令都会将之后所需的常规刷新命令数量减少一个。提前拉取8个以上的Refresh命令并不会进一步减少以后所需的常规Refresh命令的数量,因此两个相邻Refresh命令之间的最大间隔限制为9×tREFI在任何给定时间,在2 x tREFI内最多可以发出16个REF命令。 自刷新模式(Self-Refresh Mode)可以在最多推迟 8 次刷新命令的情况下进入。在退出自刷新模式后,如果存在一个或多个被推迟的刷新命令,则可以进一步推迟刷新命令,但在自刷新前后推迟的刷新命令总数不得超过 8 次。在自刷新模式期间,推迟或提前的刷新命令数量不会发生变化。

4.16自刷新操作

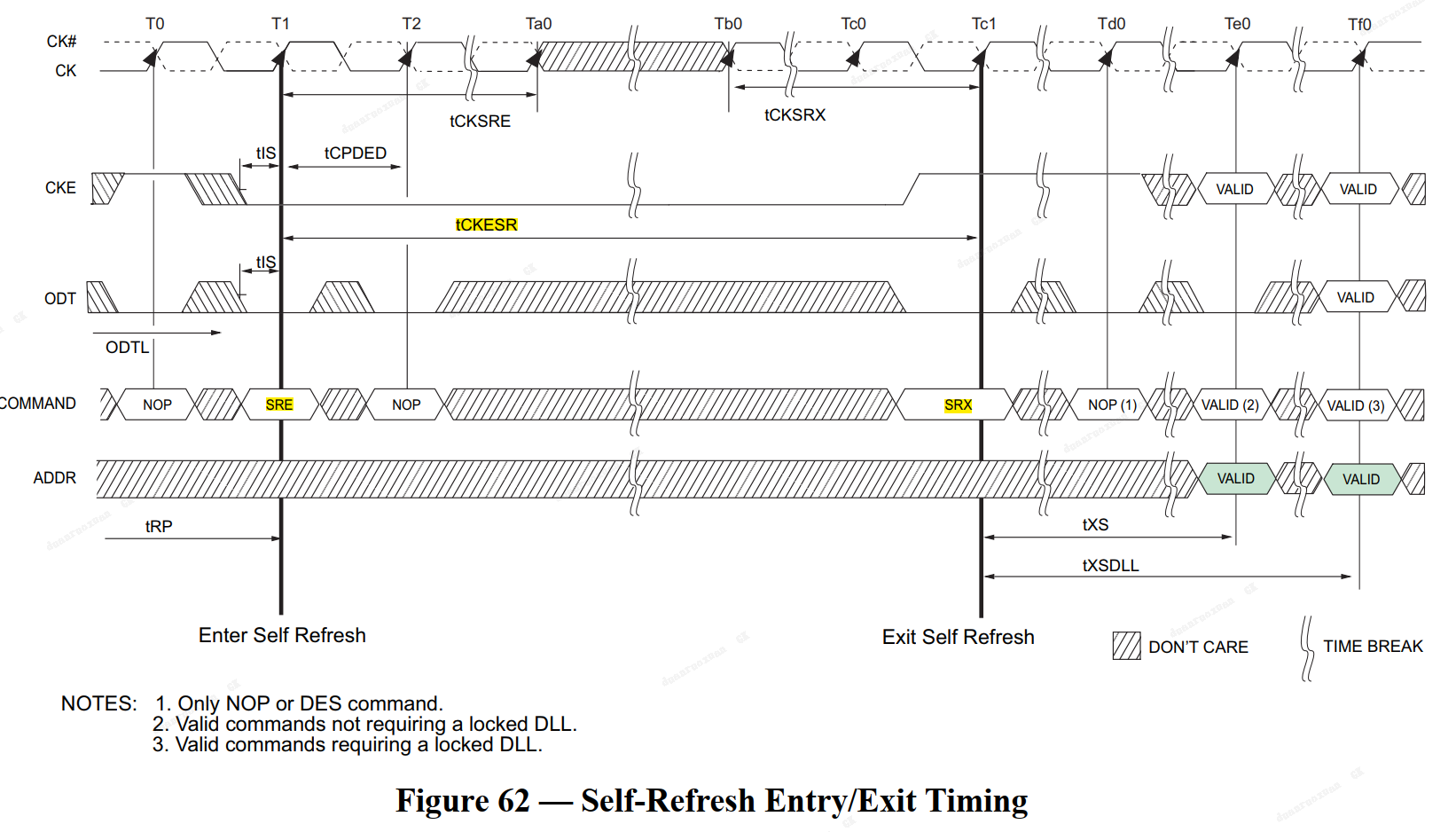

Self-Refresh命令可用于将数据保留在DDR3 SDRAM中,即使系统的其余部分已断电。在自刷新模式下,DDR3 SDRAM在没有外部时钟的情况下保留数据。DDR3 SDRAM设备有一个内置定时器,以适应自刷新操作。SelfRefresh-Entry(SRE)命令通过在时钟的上升沿使CS#、RAS#、CAS#和CKE保持低电平而WE#保持高电平来定义。

在发出自刷新条目命令之前,DDR3 SDRAM必须处于空闲状态,所有存储体预充电状态均满足tRP。“空闲状态”定义为所有存储体都关闭(满足tRP、tDAL等),没有数据突发正在进行,CKE为高,并且满足先前操作的所有定时(tMRD、tMOD、tRFC、tZQinit、tZQoper、tZQCS等)。此外,在发出自刷新条目命令之前,必须关闭ODT,方法是在自刷新条目指令之前拉低ODT引脚“ODTL+0.5tCK”时间,或使用MRS到MR1指令。一旦注册了自刷新条目命令,CKE必须保持低电平,以使设备保持在自刷新模式。在正常操作期间(DLL打开),MR1(A0=0),DLL在进入自刷新时会自动禁用,在退出自刷新时自动启用(包括DLL重置)。

当DDR3 SDRAM进入自刷新模式时,除CKE和RESET#外,所有外部控制信号都“不重要”。为了正确的自刷新操作,所有电源和参考引脚(VDD、VDDQ、VSS、VSSQ、VRefCA和VRefDQ)必须处于有效电平。并且在退出自刷新后,第一次写入操作或第一次写均衡操作可能不会早于512 nCK发生。一旦DRAM进入自刷新模式,它将在tCKE周期内内部启动至少一个刷新命令。

在自刷新操作期间,时钟在内部被禁用以节省电源。DDR3 SDRAM必须保持在自刷新模式的最短时间为tCKESR。用户可以在注册自刷新条目tCKSRE后更改外部时钟频率或停止外部时钟,但是,在设备退出自刷新操作之前,必须重新启动时钟并稳定tCKSRX。

退出自刷新的过程需要一系列事件。首先,在CKE回到高电平之前,时钟必须稳定。一旦注册了自刷新退出命令(SRX,CKE变高和命令总线上的NOP或取消选择的组合),在向设备发出不需要锁定DLL的有效命令以允许进行任何内部刷新之前,必须满足至少tXS的延迟。在应用需要锁定DLL的命令之前,必须满足至少tXSDLL的延迟。根据系统环境和自刷新所花费的时间,可能需要ZQ校准命令来补偿电压和温度漂移。

除重新进入自刷新外,CKE必须在整个自刷新退出期后tXSDLL内保持高电平,才能正常运行。退出自刷新后,DDR3 SDRAM可以在等待至少tXS周期并发出一个刷新命令(tRFC的刷新周期)后重新进入自刷新模式。在自刷新退出间隔tXS期间,必须在每个正时钟沿上注册NOP或取消选择命令。在tXSDLL期间必须关闭ODT才能正常运行。但是,如果DDR3 SDRAM在满足tXSDLL之前被置于自刷新模式,一旦DDR3 SDRAM进入自刷新模式后,ODT可能会根据图62(自刷新进入/退出时间)变得无关紧要。

4.16低功耗模式

4.14.4进入与退出

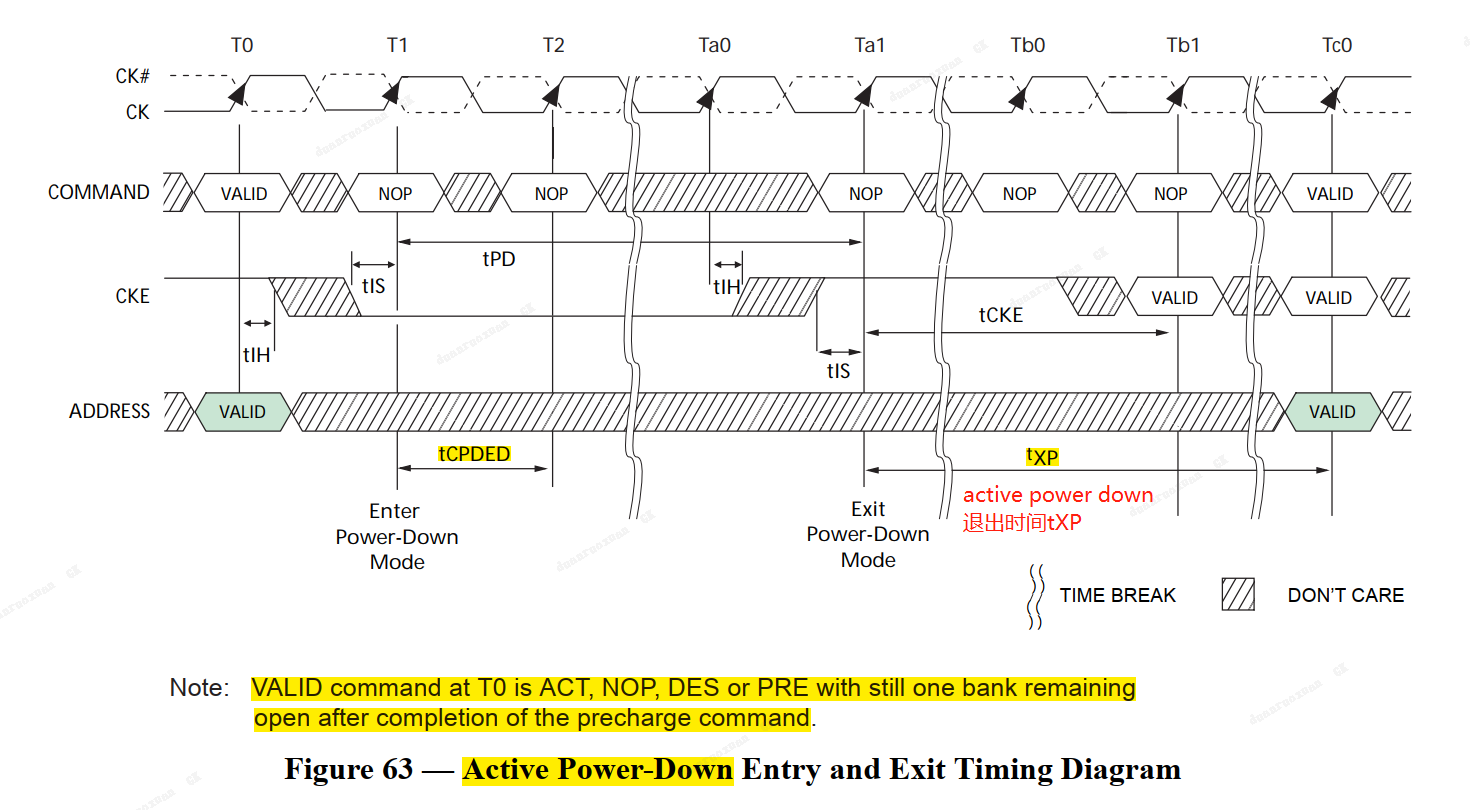

当CKE为低时(同时命令为NOP或取消选择),会同步进入低功耗状态。当模式寄存器设置命令、MPR操作、ZQCAL操作、DLL锁定或读/写操作正在进行时,不允许CKE变低。

当进入低功耗状态时,DLL应处于锁定状态,以获得最快的低功耗退出时间。如果在低功耗进入期间DLL未锁定,则必须在退出低功耗模式后重置DLL,以便进行正确的读取操作和同步ODT操作。

如果所有Bank都处于关闭状态,DDR将进入Precharge Power-Down状态;只要有Bank处于激活状态,则进入Active Power-Down状态;

进入低功耗状态会停用输入和输出buffer,但CK、CK#、ODT、CKE和RESET#除外。为了保护CKE线上的DRAM内部延迟以阻止输入信号,在CKE关闭期间和之后的cycles中需要多个NOP或取消选择命令,该时间段定义为tCPDED。在tCPDED后,CKE_low将导致命令和地址接收停用。

此外,在进入预充电低功耗(慢退出模式)时,DLL被禁用,但在预充电低功耗(快退出模式)或主动断电期间,DLL保持启用状态。在低功耗模式下,DDR3 SDRAM的输入端必须保持CKE低、RESET#高和稳定的时钟信号,ODT应处于有效状态,但所有其他输入信号都是“不重要”。(如果RESET#在掉电期间变低,DRAM将退出PD模式并进入复位状态。)必须保持CKE低,直到满足tCKE。低功耗持续时间受设备tREFI的9倍限制。

当CKE为高时(同时命令为NOP或取消选择),低功耗状态会同步退出。在满足tCKE之前,必须保持CKE高。在CKE变高后,可以在低功耗出延迟、tXP和/或tXPDLL后启用有效的可执行命令。

对于重复的“PD慢速退出-刷新-PD进入”序列的操作,PD慢退出和PD进入之间的时钟周期数可能不足以保持DLL的更新。因此,在PD慢速退出和PD进入之间发出刷新命令时,除了tCKE外,还必须满足以下条件,以保持DRAM的正常运行。如果满足以下条件,低功耗模式可以与刷新命令结合使用:1)在发出REF命令之前必须满足tXP。2) 在进入下一次低功耗之前,必须满足tXPDLL(参考PD慢速退出的注册)。

5.ODT( 片上终结电阻)

ODT是DDR3 SDRAM的一项功能,它允许DRAM通过ODT控制引脚为x4和x8配置的每个DQ、DQS、DQS#和DM(以及x8配置的TDQS、TDQS#,当通过MR1中的A11=1启用时)打开/关闭端接电阻(??)。对于x16配置,ODT通过ODT控制引脚应用于每个DQU、DQL、DQSU、DQSU#、DQSL、DQSL#、DMU和DML信号。ODT功能旨在通过允许DRAM控制器独立地打开/关闭任何或所有DRAM器件的端接电阻来提高存储器通道的信号完整性。

自刷新模式下要关闭ODT。

发送写操作命令时需要打开ODT。

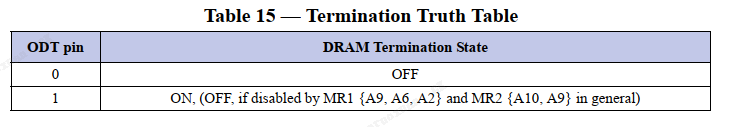

5.1ODT模式寄存器和ODT真值表

如果MR1{A9、A6、A2}或MR2{A10、A9}中的任何一个不为零,则启用ODT模式。在这种情况下,RTT的值由这些位的设置决定(参见第MR1,MR2寄存器的图)。

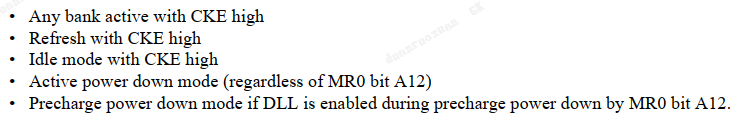

5.2同步ODT模式

只要打开并锁定DLL,就会选择同步ODT模式。根据低功耗定义,这些模式是:

在DLL关闭模式下不支持直接(?)ODT功能。在DLL关闭模式期间,必须通过连续注册ODT引脚低电平和/或通过模式寄存器设置命令将RTT_Nom位MR1{A9、A6、A2}编程为{0,0,0}来禁用管脚上终端电阻。

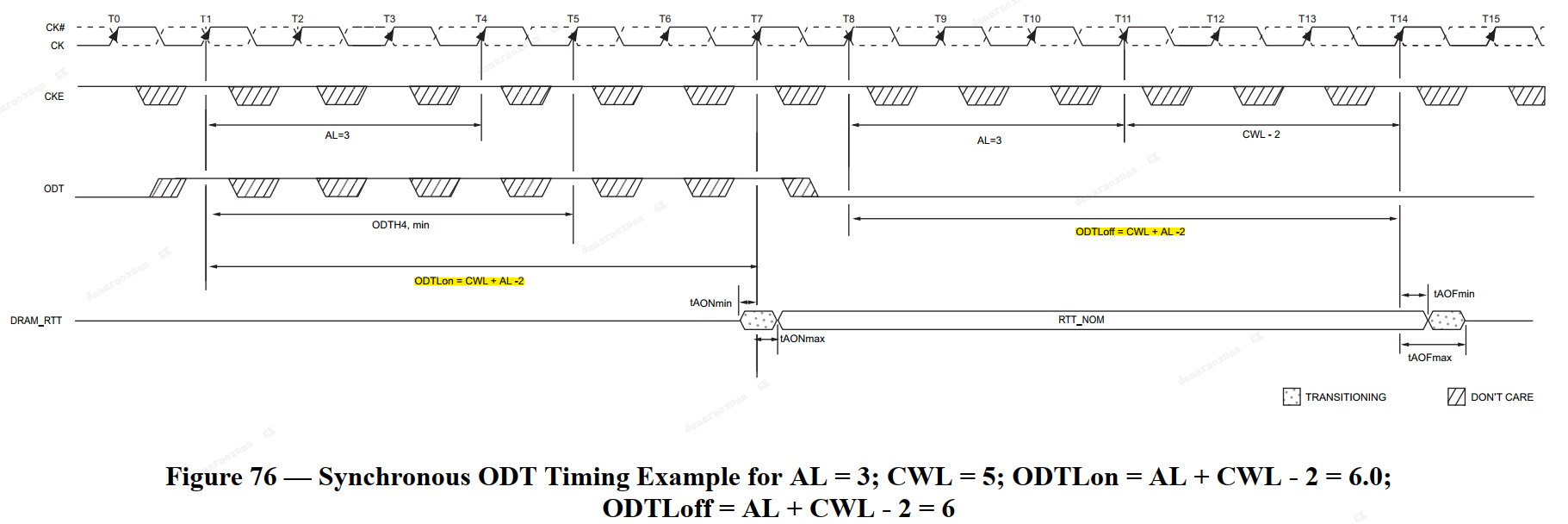

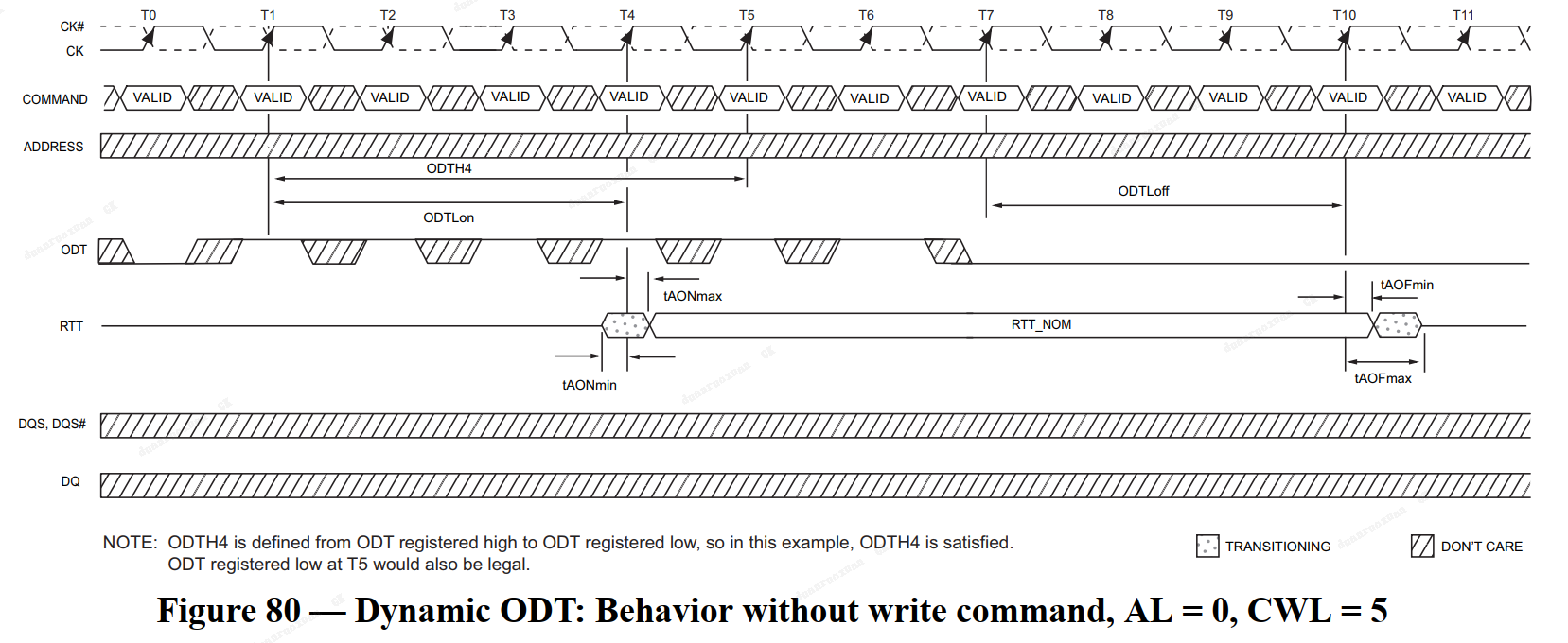

在同步ODT模式下,RTT将在ODT被上升的时钟沿采样为高后ODTLon时钟周期开启,并在ODT的上升时钟沿被记录为低后ODTLoff时钟周期关闭。ODT延迟与写入延迟(WL)的关系如下:ODTLon=WL-2;ODTLoff=WL-2。

5.2.1ODT延迟和发布ODT

在同步ODT模式下,编程到模式寄存器(MR1)中的加性延迟(AL)也适用于ODT信号。DRAM内部ODT信号相对于外部ODT信号延迟了由加性延迟(AL)定义的多个时钟周期。ODTLon=CWL+AL-2;ODTLoff=CWL+AL-2。

5.2.2时序参数

在同步ODT模式下,使时序以下定时参数(另见图76):

![]()

- 最小RTT开启时间(tAONmin)是设备离开高阻抗并且ODT电阻开始开启的时间点。最大RTT开启时间(tAONmax)是ODT电阻完全开启的时间点。两者都是从ODTLon开始测量的。

- 最小RTT关闭时间(tAOFmin)是设备开始关闭ODT电阻的时间点。最大RTT关闭时间(tAOFmax)是ODT达到高阻抗的时间点。两者都是从ODTLoff测量的。

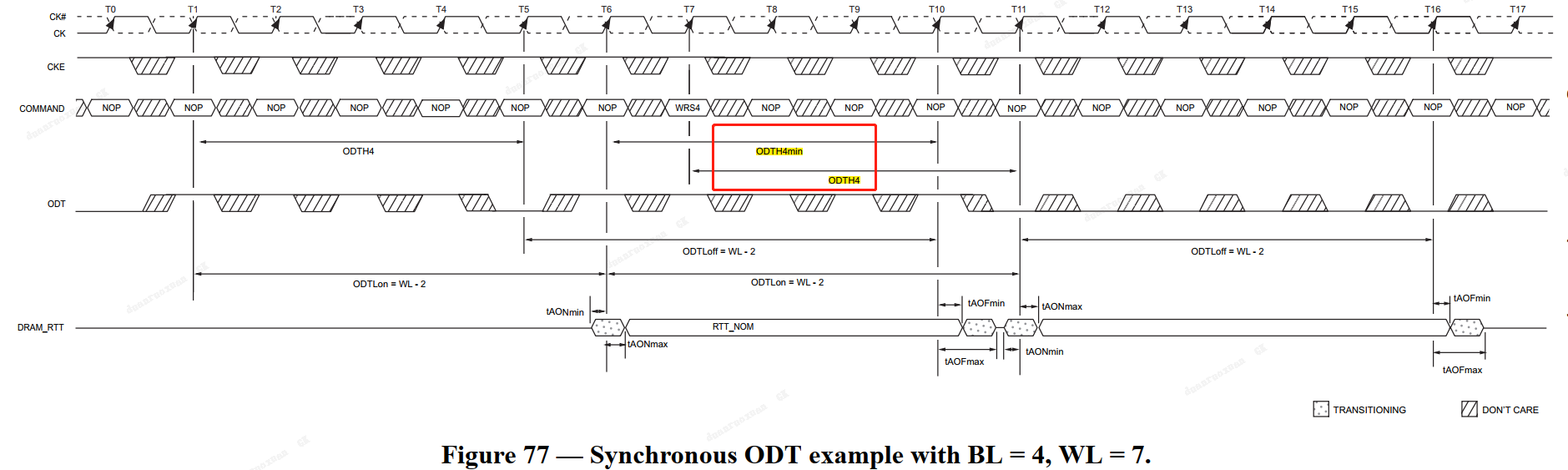

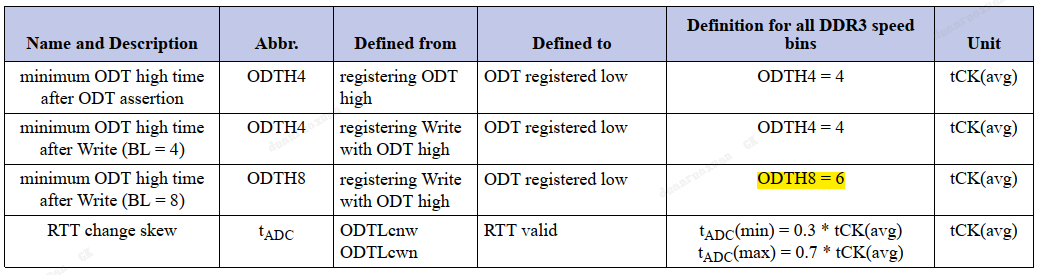

- 当ODT拉高时,它必须保持高电平,直到满足ODTH4(ODT拉高4clycles)。如果SDRAM以ODT高电平注册了写命令,则ODT必须保持高电平,直到写入命令后的ODTH4(BL=4)或ODTH8(BL=8)为止(见图77)。ODTH4和ODTH8是从ODT注册高到ODT注册低或从写入命令的注册到ODT被注册低进行测量的。

在T1时刻断言后,ODT必须拉高至少ODTH4;在写入命令后,ODT必须保持高ODTH4(BL=4)或ODTH8(BL=8)(T7)。注意,尽管ODTH4在T6开始处得到满足,但ODT在T11之前不得变低(7+4=11),因为ODTH4也必须在T7处满足。

5.2.3读期间的ODT

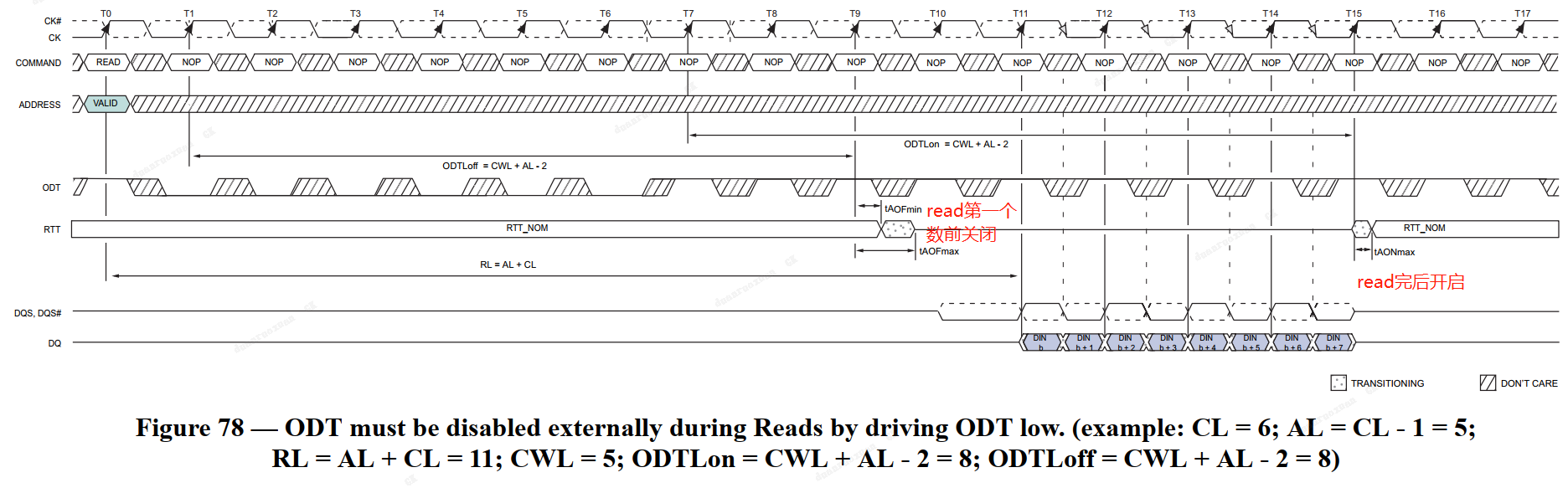

由于DDR3 SDRAM不能同时终止和驱动,因此必须通过适当地将ODT引脚驱动为低电平,在读preamble 之前至少半个时钟周期禁用RTT。RTT可能直到后post-amble 结束才启用,如下例所示。如下图78所示,在周期T15,DRAM在停止驱动时打开终端,这由tHZ决定。

如果DRAM提前停止驱动(即tHZ提前),则tAONmin时序可能适用。如果DRAM停止延迟驱动(即tHZ延迟),则DRAM符合tAONmax时序。请注意,ODT可以在读取之前提前禁用,在读取之后启用,如图78中的示例所示。

5.3动态ODT模式

在某些应用情况下,为了进一步增强数据总线上的信号完整性,希望可以在不发出MRS命令的情况下改变DDR3 SDRAM的终止强度。“动态ODT”功能支持此要求,如下所述:

5.3.1功能描述

如果MR2的位(A9)或(A10)设置为“1”,则启用动态ODT模式。该功能描如下:

- 有两个RTT值可用:RTT_Nom和RTT_WR

- RTT_Nom的值通过MR1中的位A[9,6,2]预选

- RTT_WR的值通过MR2中的位A[10,9]预选

- 在没有写命令的操作期间,终端控制如下:

- 选择标称终端强度RTT_Nom

- 通过ODT引脚和延迟ODTLon和ODTLoff控制终端开/关定时

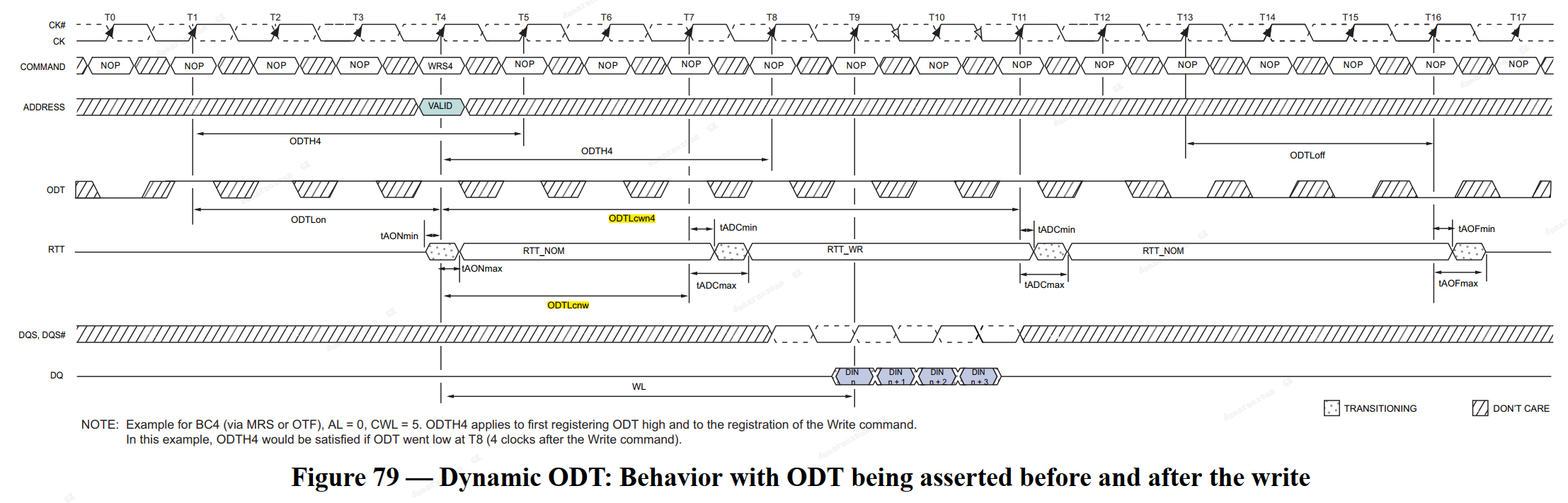

当写入命令(WR、WRA、WRS4、WRS8、WRAS4、WRAS8)被注册时,如果启用了动态ODT,则终端控制如下:

- 选择写入命令后的延迟ODTLcnw、终端强度变为RTT_WR

- 选择写入命令后的延迟ODTLcwn8(对于BL8,由MRS或选定的OTF固定)或ODTLcwn 4(对于BC4,由MRS或者选定的OTF固定),终端强度变为RTT_Nom。

- 通过ODT引脚和ODTLon、ODTLoff控制终端开/关时序

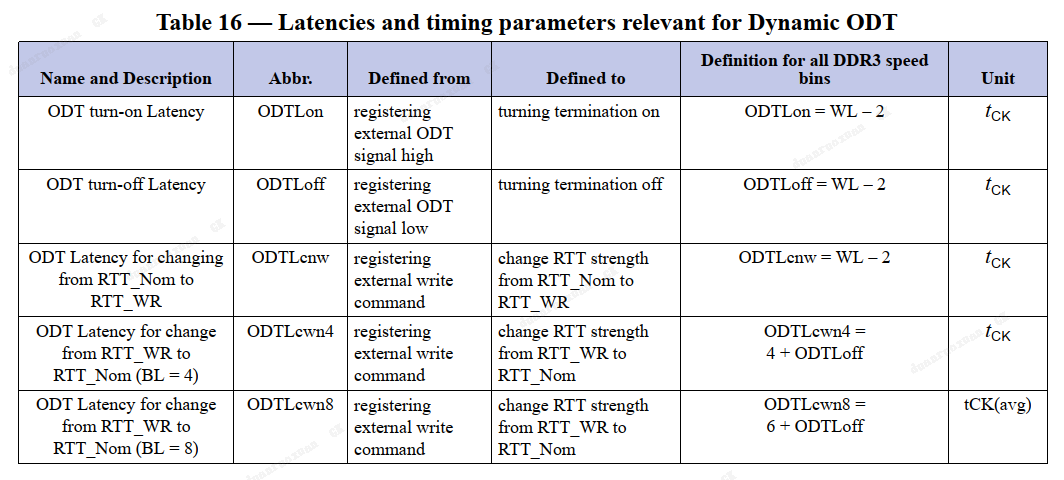

表16显示了与动态ODT模式下的ODT控制相关的延迟和时序参数。

动态ODT功能在DLL关闭模式下不受支持。用户必须使用MRS命令设置Rtt_WR,MR2{A10,A9}={0,0},以从外部禁用动态ODT。

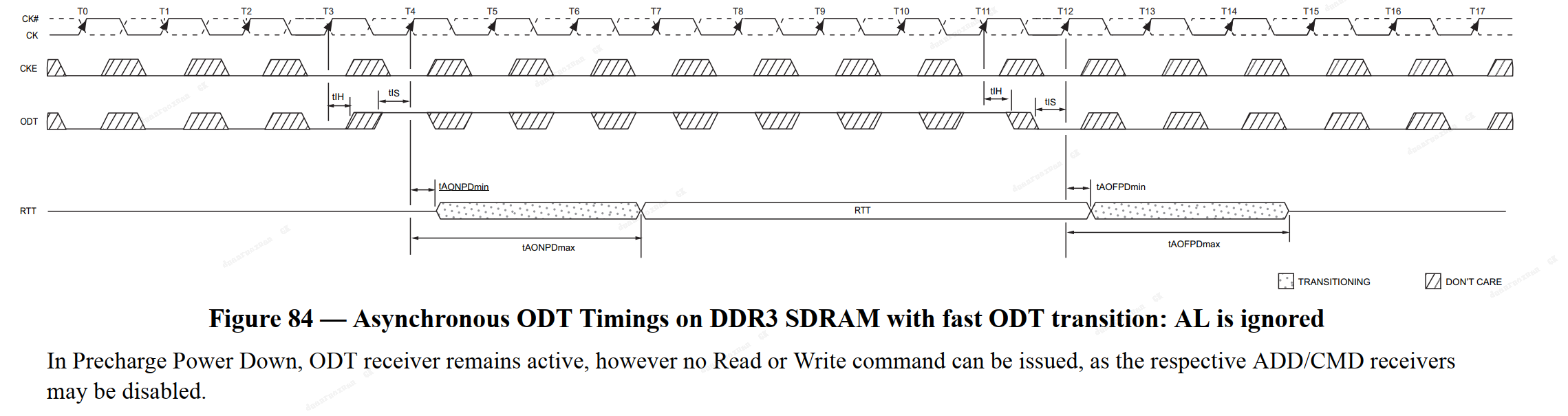

5.4异步ODT模式

在预充电低功耗模式下dll从开启变为关闭后进入异步ODT模式。。

在异步ODT模式下,内部ODT命令相对于外部ODT命令不会因加性延迟(AL)而延迟。

在异步ODT模式下,应用以下时序参数(见图84):tAONPD、min、max、tAOFPD、min和max。

最小RTT开启时间(tAONPDmin)是设备终端电路离开高阻态并且ODT电阻开始开启的时间点。最大RTT开启时间(tAONPDmax)是ODT电阻完全开启的时间点。tAONPDmin和tAONPDmax是从ODT采样高开始测量的。

最小RTT关闭时间(tAOFPDmin)是设备端接电路开始关闭ODT电阻的时间点。最大ODT关闭时间(tAOFPDmax)是ODT达到高阻态的时间点。tAOFPDmin和tAOFPDmax是从ODT采样低开始测量的。

5.4.2低功耗进入期同步到异步ODT模式转换

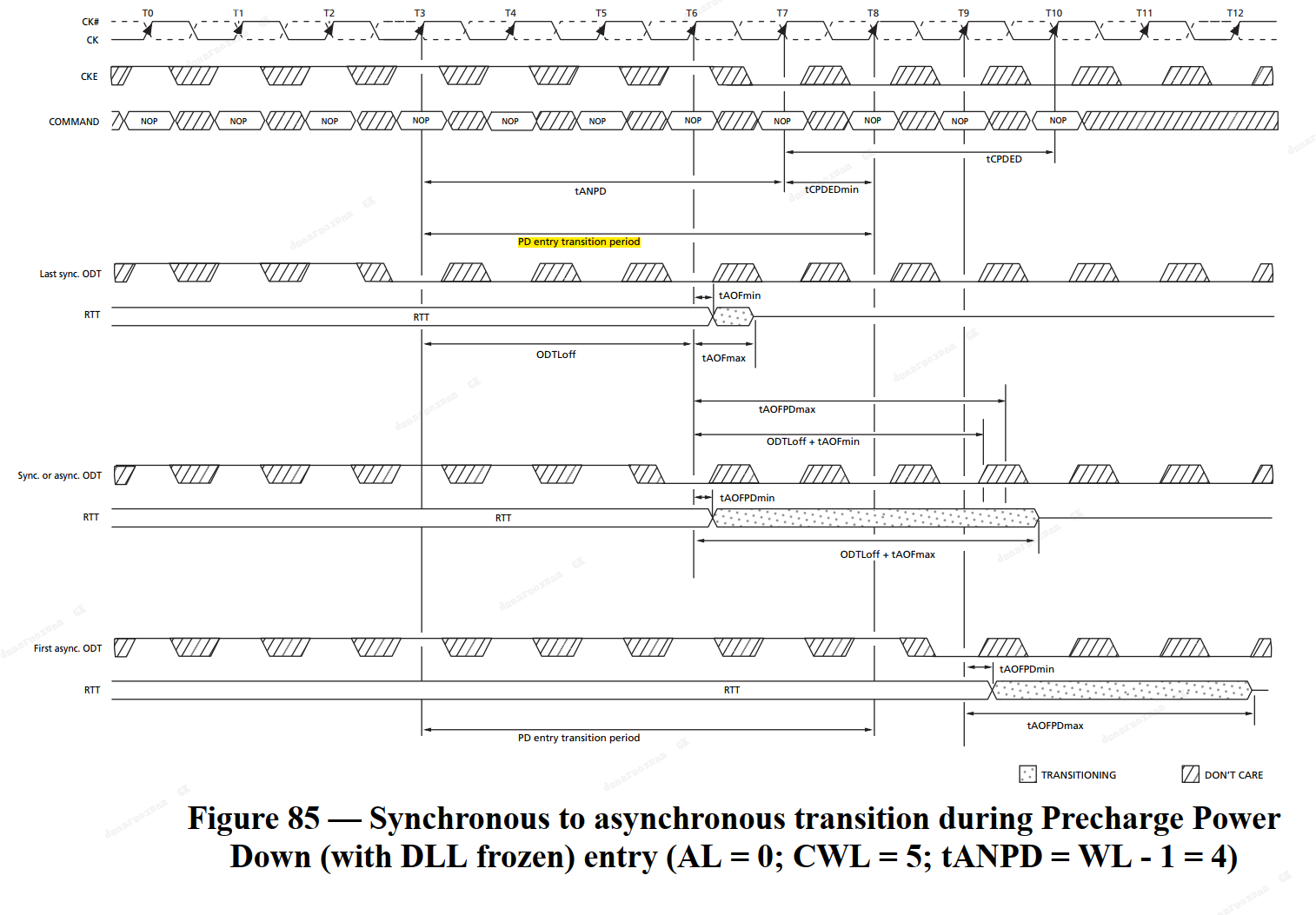

如果通过将MR0中的A12位设置为“0”来选择在预充电断电模式下冻结DLL,则在低功耗进入周围有一个过渡期,DDR3 SDRAM可能会表现为同步或异步ODT????。

过渡期由参数tANPD和tCPDED(min)定义。tANPD等于(WL-1),从CKE首次记录为低的时钟周期开始向前计数。tCPDED(min)从CKE首次记录为低的时钟周期开始。过渡期从tANPD的起点开始,到tCPDED的终点(min)结束,如图85所示。

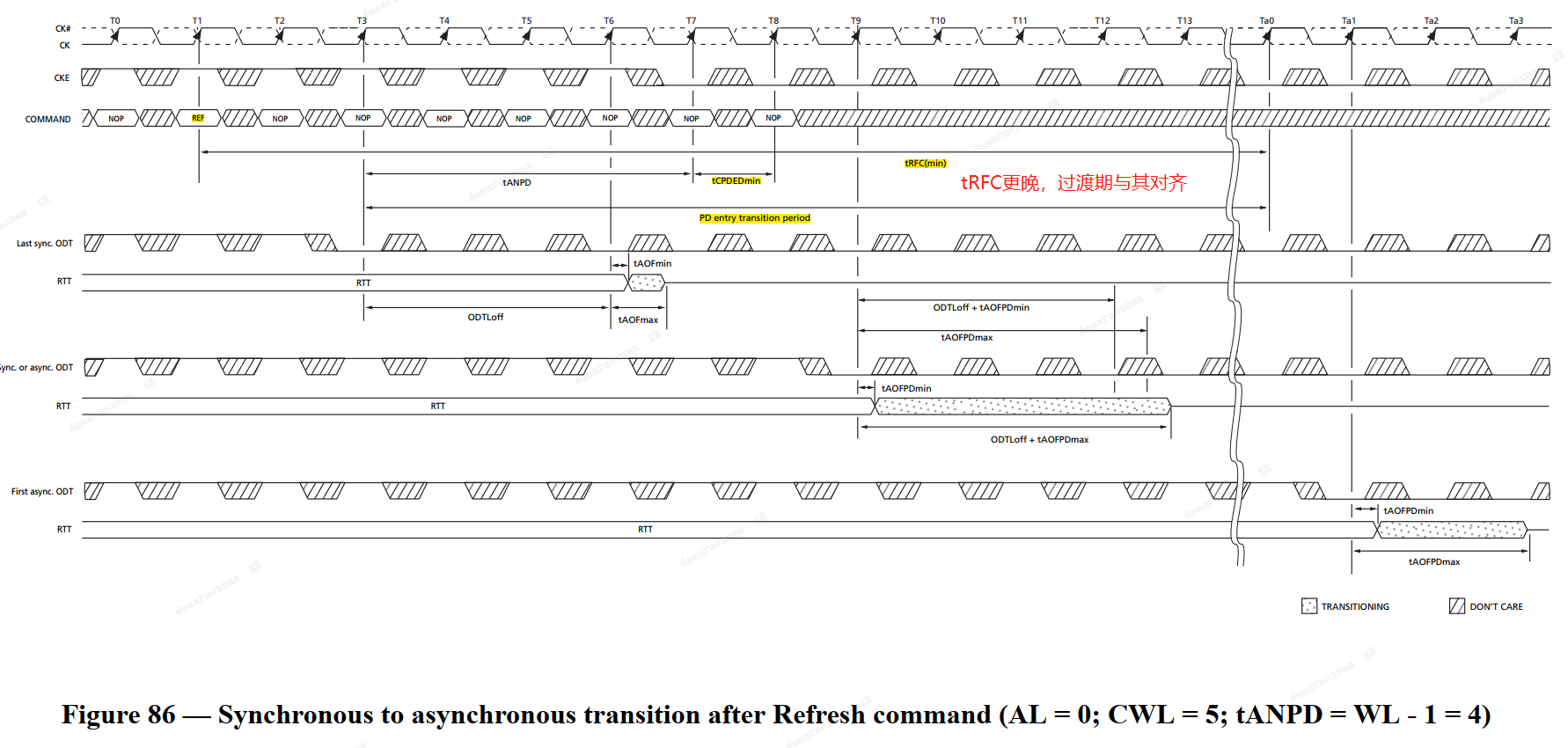

如果在CKE变低时(?)有一个正在进行的Refresh命令,则过渡期在Refresh命令后的tRFC(min)和tCPDED(min)的终点中较晚的一个结束,如图86所示。注意,tANPD的实际起点不包括在过渡期内,tCPDED(min)和tRFC(min)的实际终点分别包括在过渡期间内

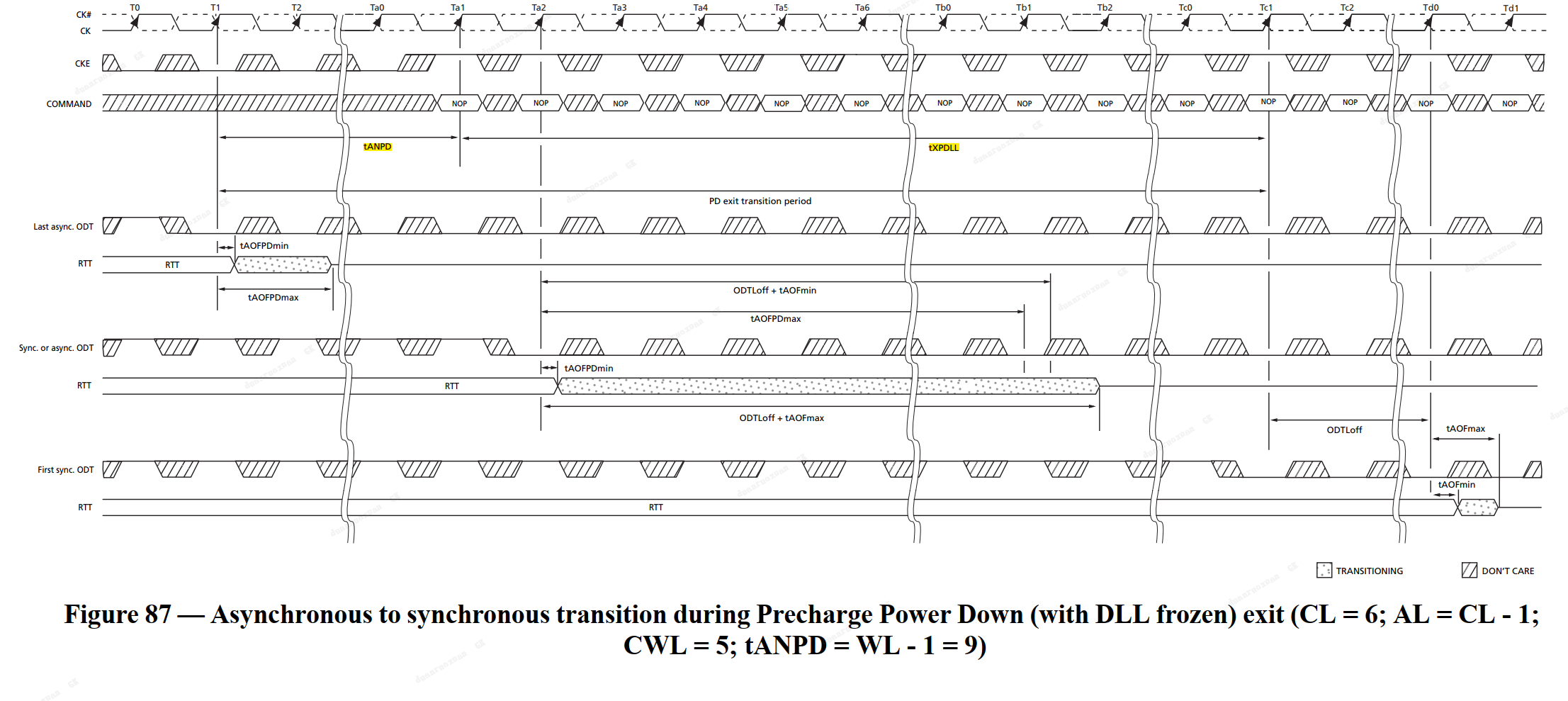

5.4.3低功耗退出期间异步到同步ODT模式转换

如果通过将MR0中的A12位设置为“0”,选择DLL在预充电低功耗模式下冻结,则在低功耗退出前后还有一个过渡期,在这个过渡期内,DDR3 SDRAM必须对ODT的变化做出同步或异步响应。

该过渡期在CKE首次登记为高之前tANPD开始,在CKE第一次登记为高之后tXPDLL结束。tANPD等于(WL-1),从CKE首次记录为高的时钟周期开始(向后)计数。

过渡期间的ODT断言可能会导致RTT变化,最早发生在tAONPDmin和(ODTLon*tCK+tAONmin)中较小的一个,最晚发生在tAONUPDmax和(ODTLSon*tCK+tAONmax)中较大的一个。过渡期内的ODT取消断言可能会导致RTT变化,最早发生在tAOFPDmin和(ODTLoff*tCK+tAOFmin)中较小的一个,最晚发生在tAOBPDmax和(ODTLSoff*tCK+tAOFmax)中较大的一个。见下表:

注意,如果AL的值较大,RTT不确定的范围会变得相当大。图87显示了三种不同的情况:ODT_C,tANPD之前的异步响应;ODT_B在过渡期间具有ODT的状态变化;ODT_A显示了具有同步响应的过渡期后ODT的状态变化。

5.4.4在短CKE高和短CKE低时段期间异步到同步ODT模式

(待补充)

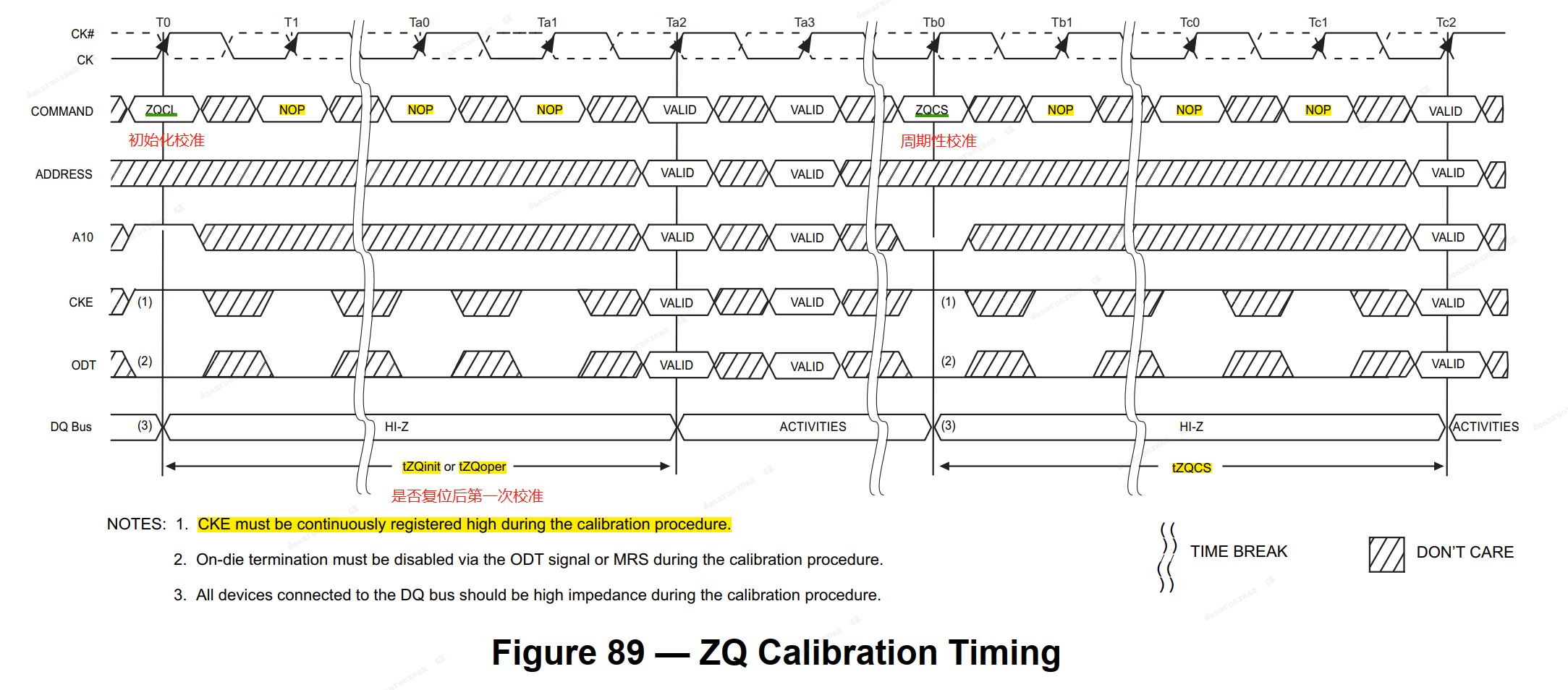

5.5ZQ校准

DRAM 颗粒需要控制器在初始化以及外部环境条件急剧变化时发送 ZQ Calibration 命令,以校正 DRAM 内部集成的发送与接收阻抗。

ZQ Calibration 作用:DRAM ZQ Calibration 校正因为外部环境变化而变化的片上电阻值,Ron 和 ODT,分别是发送驱动逻辑的输出阻抗和接收逻辑的终结电阻值,以保证传输信号的质量。

5.5.1ZQ校准描述

ZQ校准命令用于校准DRAM Ron&ODT值。DDR3 SDRAM在初始化时需要更长的时间来校准输出驱动器和ODT电路,而执行周期性校准所需的时间相对较少。

ZQCL命令用于在上电初始化序列期间执行初始校准。根据系统环境,控制器可以随时发出此命令。ZQCL命令触发DRAM内的校准引擎,一旦实现校准,校准值就会从校准引擎传输到DRAM IO,这会反映为更新的输出驱动器和ODT值。

复位后发出的第一个ZQCL命令允许tZQinit的定时周期来执行完全校准和值传输。除RESET后发出的第一个ZQCL命令外,所有其他ZQCL指令都为tZQoper执行完全校准和值传输。

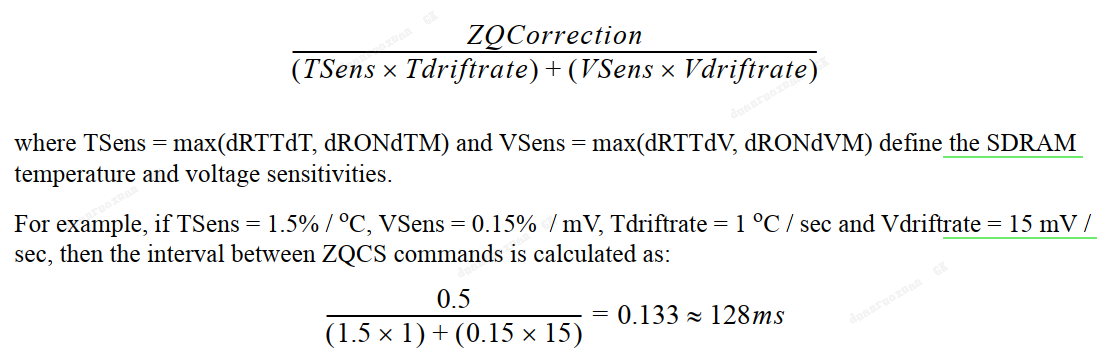

ZQCS命令用于执行周期性校准,以考虑电压和温度变化。提供了一个较短的时序窗口来执行时序参数tZQCS定义的值的校准和传输。假设“输出驱动器电压和温度灵敏度”和“ODT电压和温度敏感性”表中规定的最大灵敏度,一个ZQCS命令可以有效地纠正所有速度区间在64 nCK内校正0.5%((ZQ Correction)的RON和RTT误差。ZQCS命令之间的适当间隔可以从这些表和其他特定于应用程序的参数中确定。示出了一种计算ZQCS命令之间间隔的方法,该方法给定了SDRAM在应用中受到的温度(Tdriftrate)和电压(Vdriftrates)漂移率。间隔可以通过以下公式定义:

在tZQinit、tZQoper或tZQCS期间,控制器不应在DRAM通道上执行任何其他活动。DRAM通道上的静止时间允许对输出驱动器和ODT值进行精确校准。一旦DRAM校准完成,DRAM应禁用ZQ电流消耗路径以降低功耗。

在控制器发出ZQCL或ZQCS命令之前,必须对所有bank进行预充电并满足tRP。

ZQ校准命令也可以在自刷新后与DLL锁定时间并行发出。自刷新退出后,如果没有明确的ZQ校准命令,DDR3 SDRAM将不会执行IO校准。自刷新退出后,ZQ校准命令(短或长)的最早可能时间是tXS。

在设备之间共享ZQ电阻器的系统中,控制器不得允许设备之间的tZQoper、tZQinit或tZQCS有任何重叠