VIO IP核

背景介绍

Vivado中的VIO(Virtual Input/Output,虚拟输入/输出) IP核是一种用于调试和测试FPGA设计的IP核。当设计者通过JTAG接口与FPGA芯片连接时,在Vivado的Verilog代码中添加VIO IP核,就可以让设计者与FPGA内部的寄存器进行交互,设计者也可以实时监视和修改设计中的信号,以便进行调试和验证。

IP核使用

VIO IP核打开如下图所示,该IP核允许用户自定义VIO的输入和输出的探头个数和探头位宽。同时,用户也可以自定义VIO IP核的输出默认值,许多项目的复位信号则可以通过VIO IP核输出的默认值来实现。具体IP核各参数的设置等可以参考下面这篇CSDN文章。

Vivado中VIO IP核的使用

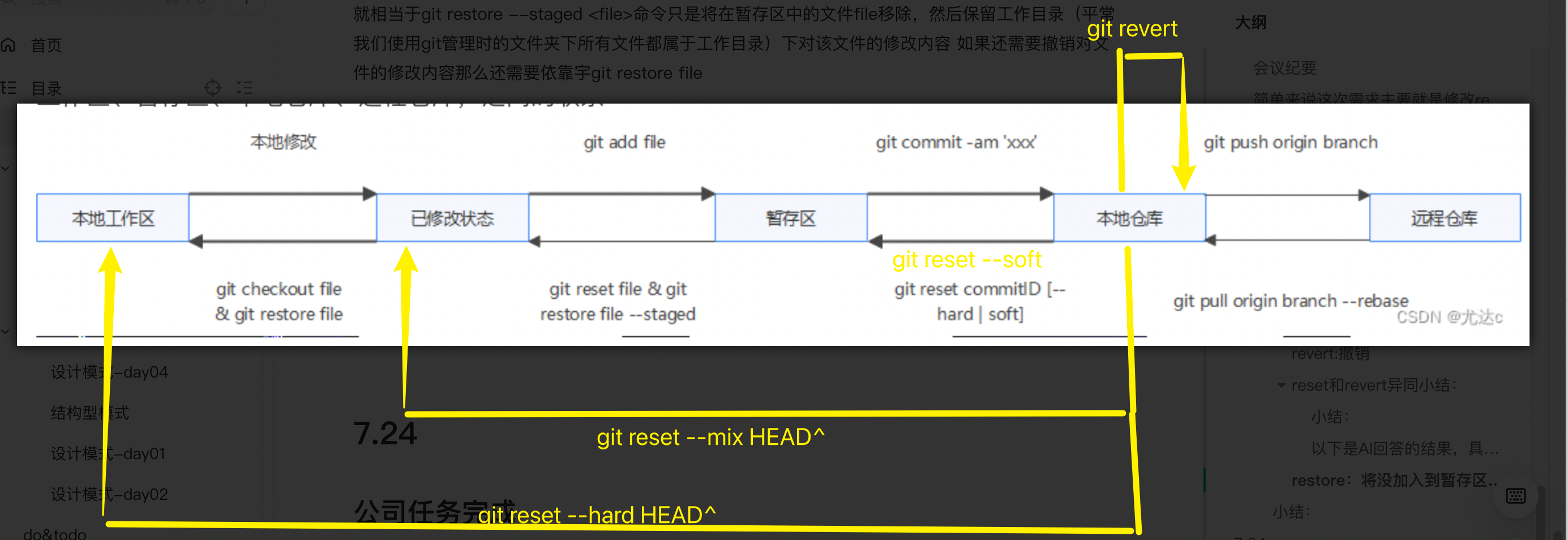

在该IP核的实际使用过程中,VIO与实际待测模块的连接如下所示。若要查看某一待测模块的输出信号状态,就将该输出信号连接自VIO的输入;若要对待测模块的某一输入信号赋初始值或给上升沿下降沿之类的信号,就将VIO的输出与待测模块的输入进行连接。

举例介绍

以一个简单的4选1-选择器为例,若要对其输入输出进行测试,则VIO连接如下图所示。

具体的上板测试验证,可以参考下面这篇CSDN文章。

FPGA_学习_15_IP核_VIO

![[网络]http请求中的URL,方法,header 和 http响应中的状态码](https://i-blog.csdnimg.cn/direct/4580f7d7c68f4583a1480aa64606baa3.png)