本文以测试PS端的UART和DDR3,介绍Xilinx SDK的简单用法。

1 创建VIVADO工程

Step1:新建工程

Step2:

Step3:选择器件

Step4:在接下来的页面中,点击Finish完成工程的创建

Step5:点击IP INTERGATOR 中的Create Block Design,点击OK完成Block的生成

Step6:点击“+”,在弹出对话框中搜索并双击添加ZYNQ7 Processing System IP核

Step7:单击Run Block Automation,

如下所示:

将Zynq的输出时钟连接到输入时钟上

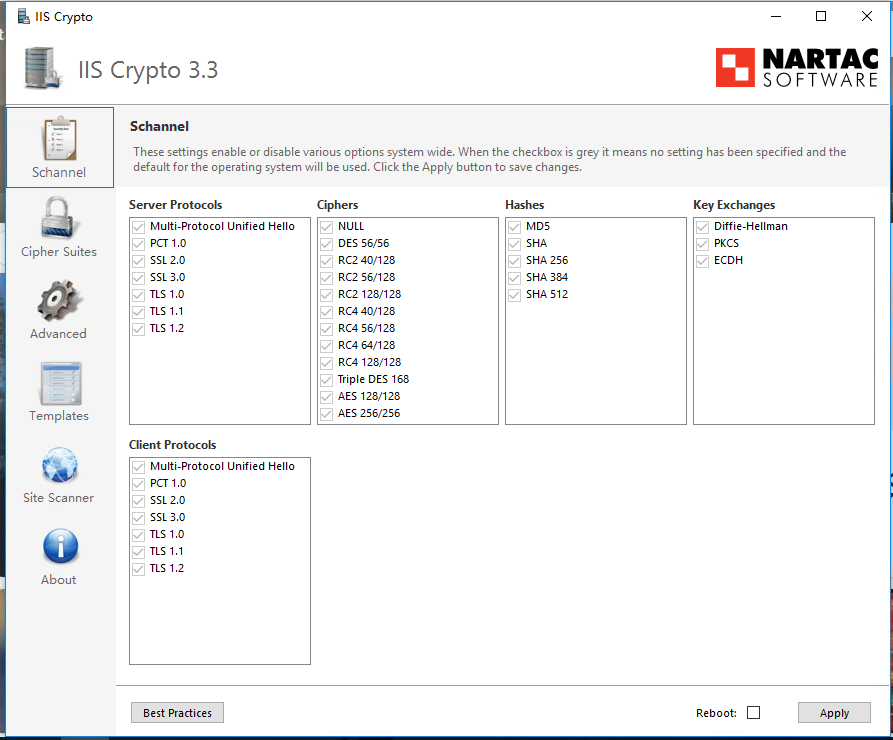

Step8:双击ZYNQ7 IP核,配置PS端UART和DDR3

首先,配置时钟;

其次,配置内存型号

最后,设置外设接口,之后点击OK。

电压配置:

Bank0 IO Voltage为LVCMOS 3.3V,

Bank1 IO Voltage为LVCMOS 1.8V。

UART配置:

点击OK完成配置。

Step9:右键点击design_1.bd,单击Generate Output Products...

Step10:在新弹出的对话框中,选择Global,然后点击Generate等待生成成功。

Step11:右键点击design_1.bd,单击Create HDL Wrapper...,生成顶层的HDL文件

Step12:选择Let Vivado manage wrapper and auto-update,然后点击OK

Step13:点击Generate Bitstream,等待bit文件生成成功。

2 创建SDK工程

Step1:点击File——Export——Export Hardware

在弹出页面中选择Include bitstream,点击OK。

Step2:点击File——Launch SDK,将bit文件加载到SDK中。

在下面的弹出菜单中点击OK。

3 串口测试

Step1:导出完成后,SDK的界面显示如下

左半部分属于硬件部分,是VIVADO定制好的SOC硬件;

右半部分是硬件的地址空间分配。

Step2:点击File——New——Application Project

Step3:在下面的弹出菜单中,工程名命名为HelloWorld,其他使用默认项,然后点击Next

Step4:选择Hello World模版,然后选择Finish。

其中“Hello World”“IwIP Echo Server”等模版属于系统自带的测试工程,可以用来测试串口和网口。

而选项“Zynq FSBL”是在固化文件时使用。

Step5:右键点击HelloWorld—— Generate linker Script

弹出菜单如下,显示所有可用内存的情况,包括代码、数据、堆栈运行所在内存的信息等。全部使用默认选项,点击Generate。

Step6:开始调试

开发板加电,连接号串口,查看串口号(可以在设备管理器中查看)。

Step7:右键点击HelloWorld——Debug As —— Debug Configurations

弹出菜单如下,双击 Xilinx C/C++ application(System Debugger),生成HelloWorld的调试文件。

记得一定要双击哦,不然就找不到调试文件了。

Step8:点击新生成的调试文件,勾选右侧的Reset entire system和Program FPGA两项,然后先点击Apply,再点击Debug。

Step9:进入SDK调试界面,

在该界面中,启用SDK软件自带的串口调试助手,进行相关设置,

在上图中右下角的信息控制台中点击SDK Terminal,如下图所示,点击其右侧的“+”,弹出串口调试器的相关设置,选择合适的端口号等选项,点击OK。

Step10:点击运行按钮![]() ,在SDK Terminal中显示运行结果:HelloWorld

,在SDK Terminal中显示运行结果:HelloWorld

4 DDR3测试

Step1:点击右侧的![]() 按钮,从调试界面返回到C/C++编辑页面

按钮,从调试界面返回到C/C++编辑页面

Step2:新建一个名为DDR3_Test的工程

弹出界面如下,命名为DDR3_Test,点击Next

选择自带的测试函数,然后点击Finish

Step3:开发板加电

Step4:记得点击Generate Linker Script,生成链接脚本

Step5:在Debug Configurations中,双击Xilinx C/C++ application(System Debugger),生成DDR3_Test的调试文件,然后记得勾选Reset entire system和Program FPGA,点击Apply,最后是点击Debug。

Step6:点击运行,在SDK Terminal中显示运行结果

Step6:点击运行,在SDK Terminal中显示运行结果

如果没有提示运行结果,可以在菜单栏中点击![]() (选择“恢复”命令以继续执行当前挂起的调试目标)试试。

(选择“恢复”命令以继续执行当前挂起的调试目标)试试。

![2024.9.9(极客大挑战 2019]EasySQL,[极客大挑战 2019]Knife)](https://i-blog.csdnimg.cn/direct/a3af68333eef4705aff32f7aa134546d.png)