文章目录

- 1.开发工具介绍

- 2.工程目录简介

- 3.Zynq裸机开发流程

- 4.Hello World实现

- 4.1vivado开发部分

- 4.2vitis开发部分

- 5.传送门

1.开发工具介绍

xilinx提供了一系列的开发环境帮助用户提高开发效率,构建了完整的软件生态。对于最新的versal系列芯片,还提供了AI的仿真工具,AI推理开发工具等。这里介绍与Zynq相关的三个开发工具vivado、vitis、petalinux。

- Vivado工具与纯PL的开发的功能是一致的,主要包括设计输入:支持使用Verilog、VHDL等硬件描述语言编写PL逻辑。综合:将HDL代码综合成FPGA的网表文件。实现:包括映射、布局布线等过程,将设计映射到实际的FPGA资源上。生成比特流:将设计生成FPGA可配置的比特流文件,包括bit文件和MCS文件。调试:通过逻辑分析仪、ILA(Integrated Logic Analyzer)等工具对FPGA进行实时调试。

- Vitis是Xilinx的开发环境Xilinx SDK的前身,主要用于处理系统部分(PS)的软件开发。它包括以下功能:应用开发:编写、编译、调试运行在Zynq ARM处理器上的C/C++应用程序。驱动程序开发:开发和调试PS与PL间的驱动程序。硬件-软件协同设计:结合Vivado生成的硬件平台文件,实现软硬件的协同设计与调试。

- PetaLinux工具是为Zynq系列提供的一个嵌入式Linux开发环境。主要功能包括:Linux内核配置和编译:根据硬件配置定制和编译Linux内核。文件系统定制:创建和定制适合Zynq的根文件系统。应用开发和调试:开发和调试Linux用户空间应用程序。设备树配置:生成和配置与硬件设计匹配的设备树文件。

2.工程目录简介

在一个工程目录下,SOC 工程一级目录一般包含 3 个文件夹,用于管理各类文件:

soc_hardware:文件夹放 system.xsa 文件

soc_fpga:文件夹放 FPGA 工程

soc_vitis:文件夹放 SDK 相关的开发文件

- FPGA文件目录soc_fpga中包含:

- cache:vivado软件运行缓存

- hw:波形文件

- ip_user_files:用户关于IP的文件

- runs: 编译与综合的结果,其中impl-1文件夹中存放的是编译生成的可执行文件,.bin 是可以固化的文件,.bit是烧写的bit流文件。

- sim:仿真结果文件

- srcs:源码,仿真文件,约束文件

- tmp:自制IP核时的临时设计工程文件夹

- xpr: vivado的工程文件

- Vitis文件目录soc_vitis中包含:

工程名文件夹(project_name): 这是项目的主文件夹,通常包含与软件开发相关的内容。它主要存放以下内容:应用程序源代码:包括C/C++源文件、头文件等。编译生成的中间文件和可执行文件。项目配置文件:用于管理项目的编译选项、链接库和其他软件配置。 - 工程名+system文件夹(project_name_system): 这个文件夹专门用于管理与系统设计相关的内容,通常涉及硬件设计和硬件-软件协同设计。

system_wrapper文件夹包含系统级封装文件,是硬件设计的顶层封装。它通常用于将多个硬件模块或IP核组合在一起,形成一个整体的硬件系统。其中:- hw文件夹中存储的是硬件设计相关的生成文件和中间文件。这些文件包括从Vivado导出的硬件平台描述文件(如*.xsa),这些文件定义了PL部分的资源分配和配置。

- export/文件夹用于存储导出的硬件设计文件,特别是在硬件设计完成后,这些文件可以被导出到Vitis的其他部分进行软件开发。通常包含硬件平台描述文件(如

*.xsa)和一些约束文件。 - psu_cortexa53_0/`文件夹通常与处理系统(PS)部分相关,特别是与Cortex-A53核的配置和生成有关。它可能包含启动文件、设备树文件、以及与处理器配置相关的文件,帮助定义Cortex-A53处理器在系统中的行为和配置。

- zynqmp_fsbl/文件夹存储的是Zynq MPSoC平台的FSBL(First Stage Boot Loader,一级启动加载器)相关文件。FSBL负责初始化硬件平台,加载和引导后续的启动镜像,如ATF(Arm Trusted Firmware)、PMU固件、U-Boot等。

- zynqmp_pmufw/文件夹包含的是与Zynq MPSoC平台的PMU(Power Management Unit,电源管理单元)固件相关的文件。PMU固件用于管理Zynq设备的电源状态、时钟和复位控制,确保系统的电源管理和状态切换功能。

3.Zynq裸机开发流程

Zynq裸机开发(Bare-Metal Development)指的是在没有操作系统的情况下直接在Zynq SoC(System on Chip)上开发应用程序。裸机开发通常涉及直接控制硬件资源,适用于对性能要求较高或需要精细控制的应用。以下是裸机开发的典型流程:

1.vivado硬件设计,选择MPSoc IP核,配置内存控制器,外设以及PL、PS交互情况,最后生成bit流文件,导出xsa文件。

2.vitis进入软件开发,创建硬件平台工程和应用工程并完成相关程序的编写、调试、编译。

3.上板验证

这里vivado的作用类似于单片机开发中的STM32Cube,即用图形化的方式配置硬件内部的连接,vivado将为PS端定制一个外设,定义了二者之间的交互,以及其他PS外设的使用。具体的开发流程结合HelloWorld工程在下节实现。

4.Hello World实现

4.1vivado开发部分

1.创建vivado工程,设置工程名为HelloWorld。

2.选择器件型号 XCZU4EV-SFVC784-2I,本系列所有工程基于该器件。

3.创建BD工程,添加zynq IP核。

4.通过创建好的tcl文件完成IP配置,这是购买开发板的时候厂家把所有PS端的配置做好之后生成的TCL文件,使用的时候直接导入就可以,后面会随着文章的推进逐步讲解如何做好PS端配置。

5.选择validate design完成IP 核配置验证。

6.①编译并导出平台文件,右键block文件,选择generate output products;②等待完成后右键block文件,选择create HDL Wrapper;system_wrapper.v 为创建的 Verilog 文件,该模块使用 Verilog HDL 对设计进行封装,主要完成了对 block design 的例化。

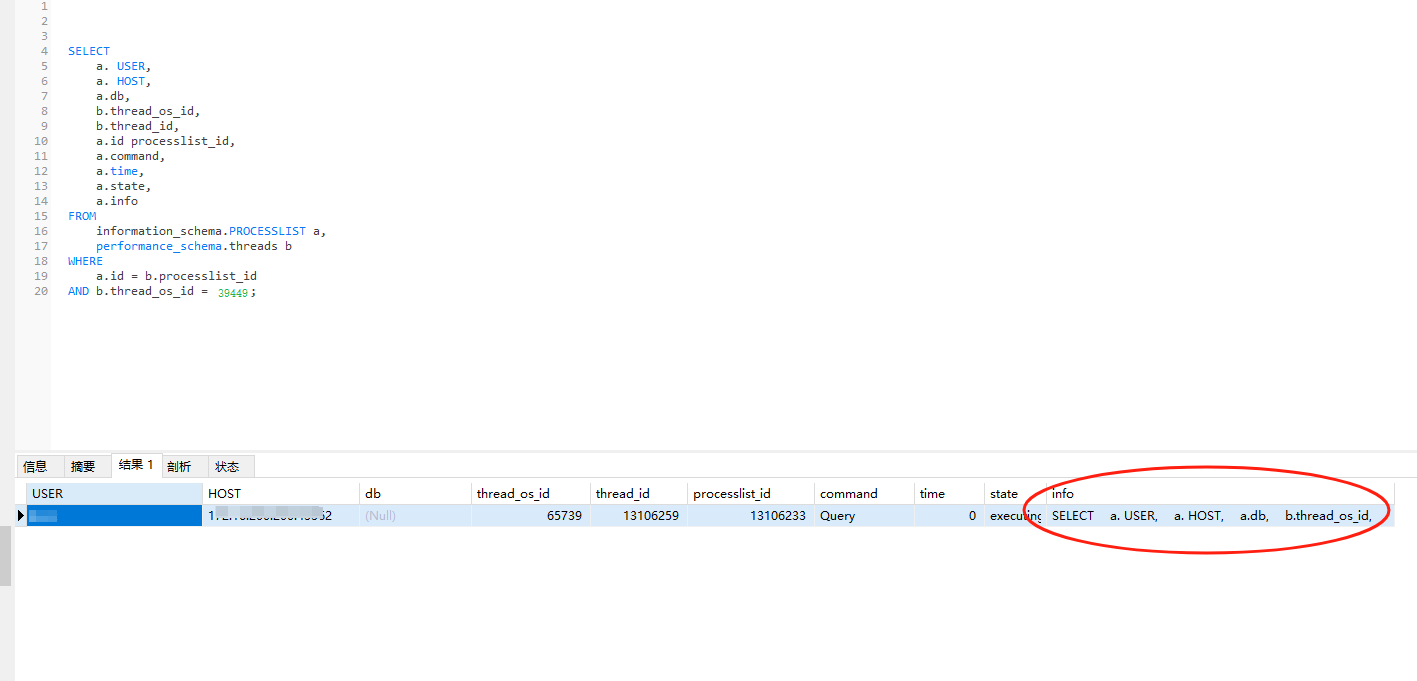

7.添加约束xdc文件,生成bit流;完成后 File->Export Hardware->Include bitstream。本工程中没有使用PL端的资源,所以无需添加约束,也无需生成bit流,直接导出硬件即可。具体按照下图选择即可。

8.tools->launch Vitis IDE,并选择工作空间为创建好的soc_vitis目录

4.2vitis开发部分

1.选择new->new application project,create a new platform from hardware,选择刚才创建的xsa文件,为应用工程起名字为hello_world;生成之后,其中system_wrapper为平台工程,hello_world为应用工程,hello_world_system为系统工程。在最后的界面中选择一个helloworld的模板,点击finish完成创建。

2.打开应用工程中的cpp文件,可以看见该模板通过串口完成了hello world 的打印功能。选中应用工程,右键选择build project,编译完成console框提示Build Finished 。

3.右键应用工程选择run as->run configurations

4.window->show view中添加terminal,单击小图标进行串口配置,第一次调试应该安装串口驱动后在设备管理器查找相应的COM口,其余配置如下图所示,最后看见在交互框中打印了“HelloWorld”。

5.传送门

- 我的主页

- Zynq从零开始专栏汇总导航

| END |

🔈文章原创,首发于CSDN论坛。

🔈欢迎点赞❤❤收藏⭐⭐打赏💴💴!

🔈欢迎评论区或私信指出错误❌,提出宝贵意见或疑问❓。