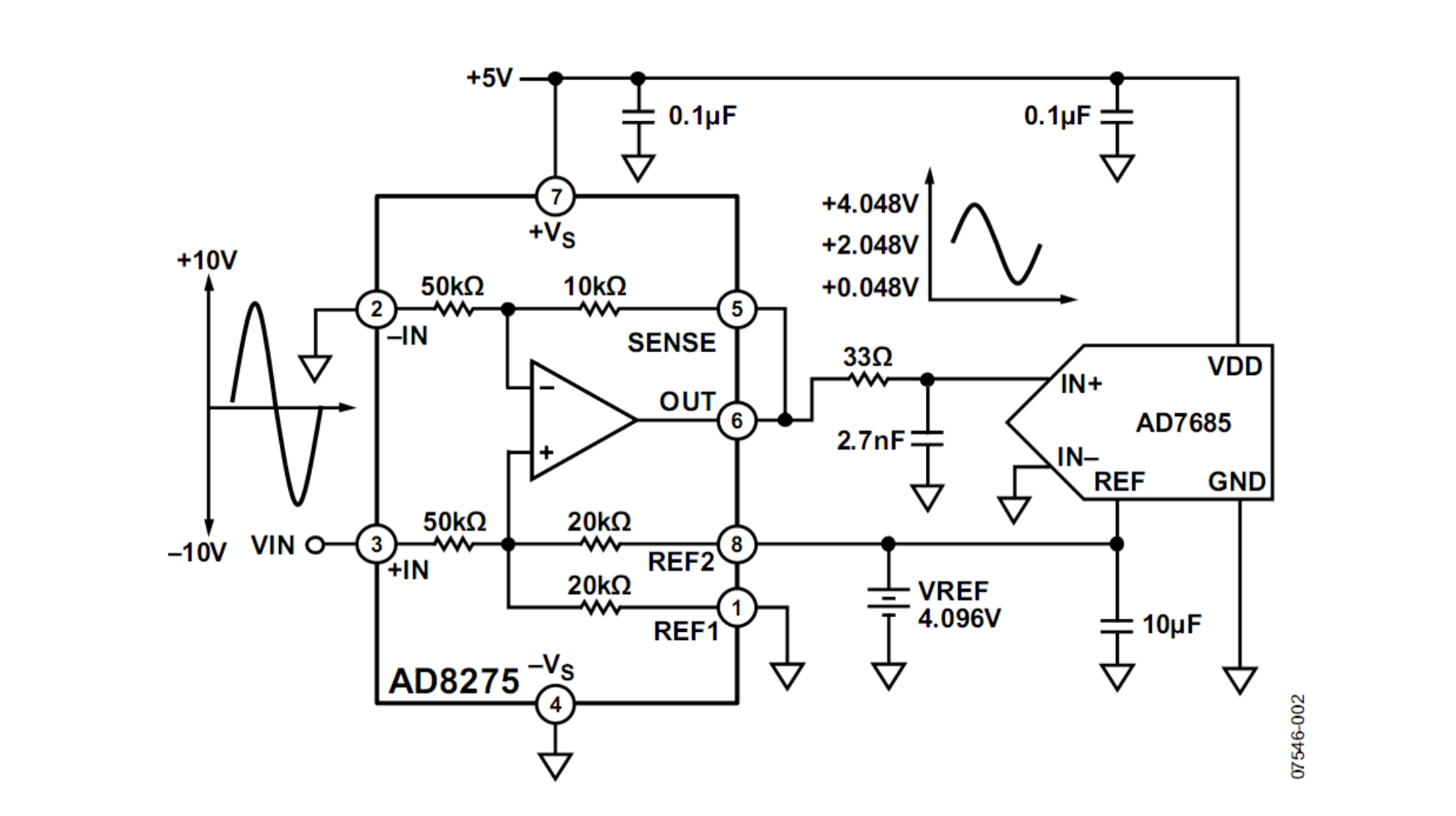

1 电平移位电路

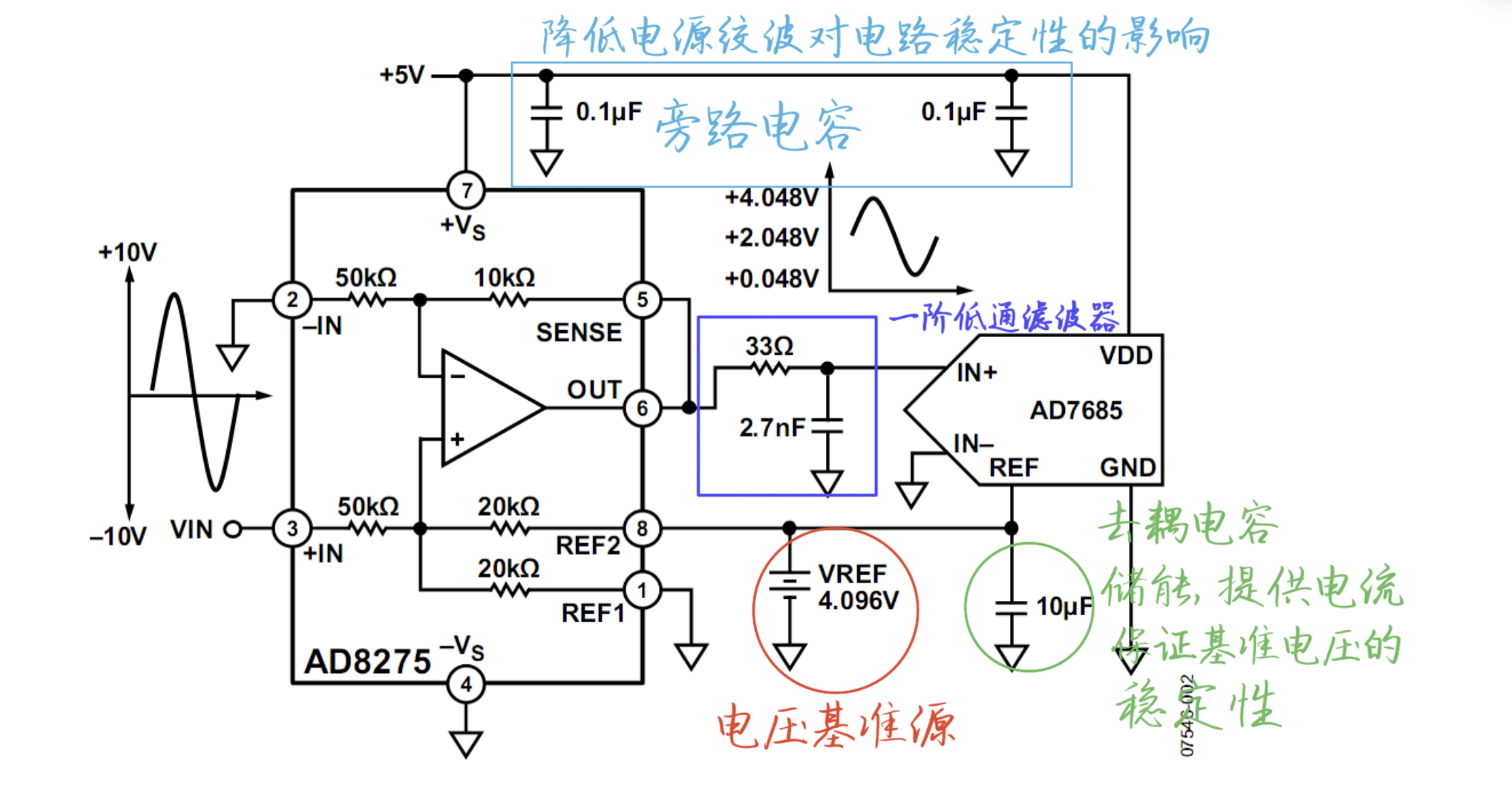

如图所示的电平移位电路,用于ADC的前级驱动,它将一个变化范围为-10V ~ +10V的输入信号,线性变化成0.048V ~ 4.048V的信号,以满足ADC的输入范围要求。

2 电路说明

- V R E F V_{REF} VREF为电压基准源,能产生非常稳定精确的4.096V电压。

- 输出端的 33 Ω 33Ω 33Ω电阻和 2.7 n F 2.7nF 2.7nF电容,组成一阶低通滤波器,起到ADC入端抗混叠滤波器的作用

- 两个 0.1 u F 0.1uF 0.1uF电容为旁路电容,降低电源纹波对电路稳定性的影响,可有效降低电源端本就已经存在的噪声

- 10 u F 10uF 10uF电容为去耦电容,主要作用是提供储能库,当ADC转换过程中,瞬间需要较大的充电电流,该充电电流由去耦电容提供电荷形成,而不需要基准源再提供较大的输出电流,这样大大保证了基准源的稳定性

3 电路分析

- 根据叠加原理,得到运放正输入端电压 u + = V I N × 10 k ( 20 k 与 20 k 并联 ) 10 k + 50 k + V R E F × 100 7 k ( 50 k 与 20 k 并联 ) 100 7 k + 20 k = 1 6 V I N + 5 12 V R E F = 1 6 V I N + 5 × 2.048 6 u_{+}=V_{IN}\times \cfrac{10k(20k与20k并联)}{10k+50k}+V_{REF}\times \cfrac{\frac{100}{7}k(50k与20k并联)}{\frac{100}{7}k+20k}=\cfrac{1}{6}V_{IN}+\cfrac{5}{12}V_{REF}=\cfrac{1}{6}V_{IN}+\cfrac{5\times 2.048}{6} u+=VIN×10k+50k10k(20k与20k并联)+VREF×7100k+20k7100k(50k与20k并联)=61VIN+125VREF=61VIN+65×2.048

- 该运放为同相比例运算,根据输入输出关系可得 V O U T = ( 1 + 10 k 50 k ) u + = 6 5 ( 1 6 V I N + 5 × 2.048 6 ) = 1 5 V I N + 2.048 V_{OUT}=(1+\cfrac{10k}{50k})u_{+}=\cfrac{6}{5}(\cfrac{1}{6}V_{IN}+\cfrac{5\times 2.048}{6})=\cfrac{1}{5}V_{IN}+2.048 VOUT=(1+50k10k)u+=56(61VIN+65×2.048)=51VIN+2.048

- 当 V I N = 0 V V_{IN}= 0V VIN=0V时, V O U T = 2.048 V V_{OUT}=2.048V VOUT=2.048V;

- 当 V I N = − 10 V V_{IN}=-10V VIN=−10V时, V O U T = 0.048 V V_{OUT}=0.048V VOUT=0.048V;

- 当 V I N = + 10 V V_{IN}=+10V VIN=+10V时, V O U T = 4.048 V V_{OUT}=4.048V VOUT=4.048V;