一、处理器结构

如下图所示,主要包括处理器内核、嵌套向量中断控制器(NVIC)、系统节拍定时器(SysTick)以及可选的浮点单元,还有一些内部总线系统、可选的存储器保护单元(MPU)以及支持软件调试操作的一组部件。

(1)NVIC是异常/中断处理的内置中断控制器。常规的处理器的系统异常由MPU内部控制,而外部中断由中断控制器控制。为了提高处理器的响应速度和方便处理,Cortex-M4将中断与系统异常处理合在了一起形成了NVIC。

(2)SysTick主要用于产生周期性的操作系统中断,与NVIC和处理器紧耦合,可以加快操作系统的进程或者任务切换速率。

二、处理器总线

1. Cortex-M4处理器内核采用两条总线,即指令访问总线和数据访问总线,再经过内部总线连接产生5个总线,即:

(1)程序指令总线(I-Bus):程序存储器中指令和向量的读取

(2)程序数据总线(D-Bus):程序存储器中的数据读取和调试访问

(3)系统总线(S-Bus):用于访问RAM和外设

(4)私有外设总线(PPB):只能用来访问内部私有外设和外部调试部件,不能用于其他外设

(5)调试访问端口(DAP):调试接口模块产生到任意存储器位置的调试访问操作

2. 以上总线都采用基于AMBA(高级微控制器总线架构)的总线接口设计,特点如下:

(1)AHB(AMBA高性能总线)Lite协议用于存储器和系统总线流水线操作。

(2)APB(高级外设总线)协议用于外部设备和调试部件的访问操作。外设分为内部私有外设(NVIC、SysTick、MPU等系统部件)、外部调试部件和通用外设、外设采用APB总线通过总线桥部件连接到系统总线上。

(3)代码存储区域采用专用的总线接口,独立于系统总线,使得数据的访问和取指可以并行进行、。这种分离的总线机构还可以加快中断响应,在中断处理期间,栈访问和读取程序映像中的向量表同时进行。

3. 在简单的微处理器设计中,程序存储器一般都会被连接到I-Bus和D-Bus总线,而SRAM和外设会被连接到系统总线。

普通外设一般采用APB(高级外设总线)协议。但是高性能外设可以使用AHB(AMBA高性能总线)Lite协议以提高带宽和运行速度。PPB不能用于普通外设。

程序存储器的访问具有两个总线(I-Bus和D-Bus)接口,分别用于取指和取数,在设计中可以使用一个简单的总线复用部件将这两个总线合并,利用这两个接口可以实现FLASH的访问加速。

三、系统异常与中断

系统异常和中断主要是由两个部件来控制和管理:一个是系统控制模块(SCB),主要配置系统异常;另一个是NVIC,主要配置外部中断和管理所有异常操作。

NVIC可以配置带有256个优先级、8级抢占优先权的中断。它可以处理多个中断请求(IRQ Interrupt Request)和一个不可屏蔽中断(NMI)请求。IRQ一般由片上外设或者外部中断输入产生,NMI可以用于掉电检测。

每个异常都有一个优先级,当新的异常优先级较高时,那么当前正在执行的任务就会暂停,有些寄存器会被保存在栈空间中,而微处理器开始执行新的异常的处理,这个过程称为抢占。当更高的优先级的异常处理完后,就会异常返回,微处理器自动从栈中恢复寄存器内容,并且继续执行之前的任务。最高的优先级为系统复位,值为-3,其次为掉电检测(NMI),值为-2;再次为硬故障,值为-1。

四、SysTick

SysTick属于是NVIC的一部分,可以产生SysTick异常(编号为15)。它是一个向下计数的24位计数器,使用的是处理器时钟或者外部参考时钟(片上时钟源)。

在操作系统中,需要一个周期性的中断来定期触发操作系统内核,使处理器可以在不同的时间片内处理不同任务。微处理器确保运行在非特权等级的应用任务无法禁止该定时器,以免锁定整个系统。当不需要使用操作系统时,该定时器可以作为简单的定时器外设,用来产生周期性延时或中断。

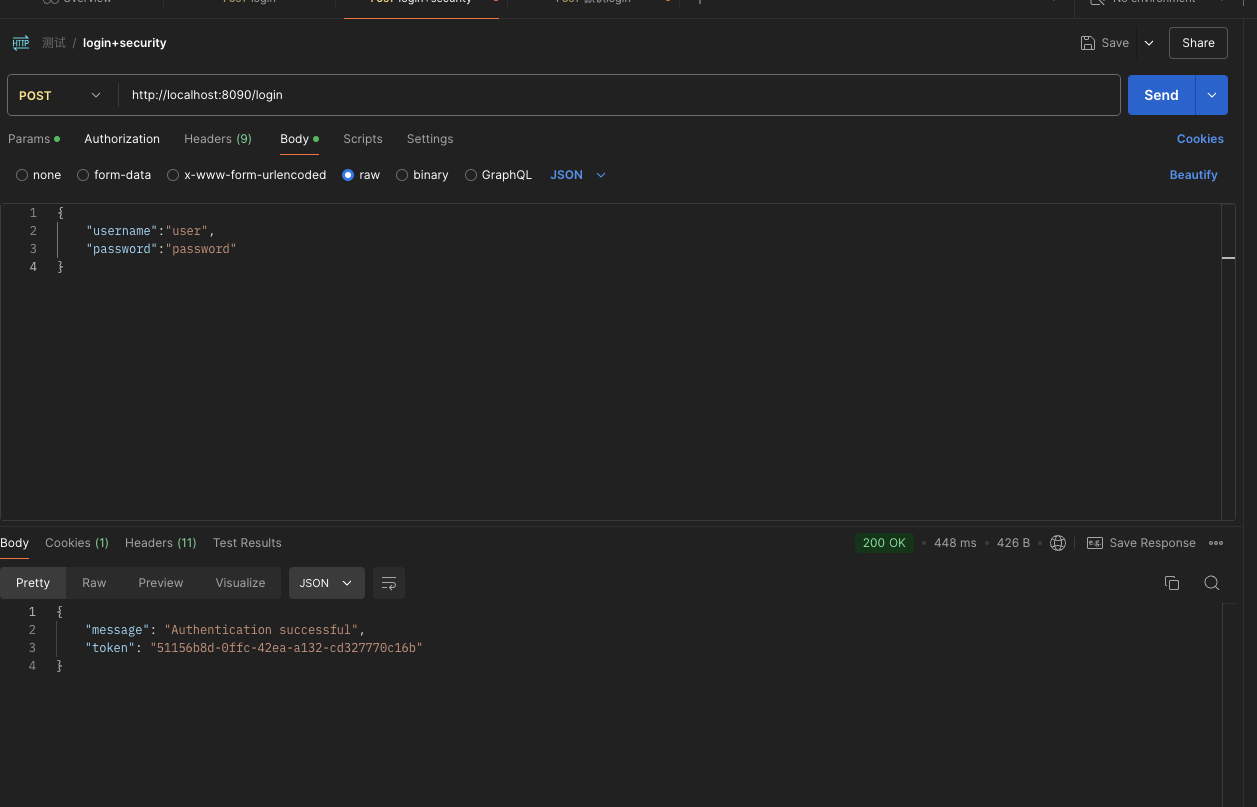

SysTick的基本框架如下图所示: