微观引入时钟源

在芯片内部,布满了各种逻辑电路,通过数字信号进行通信

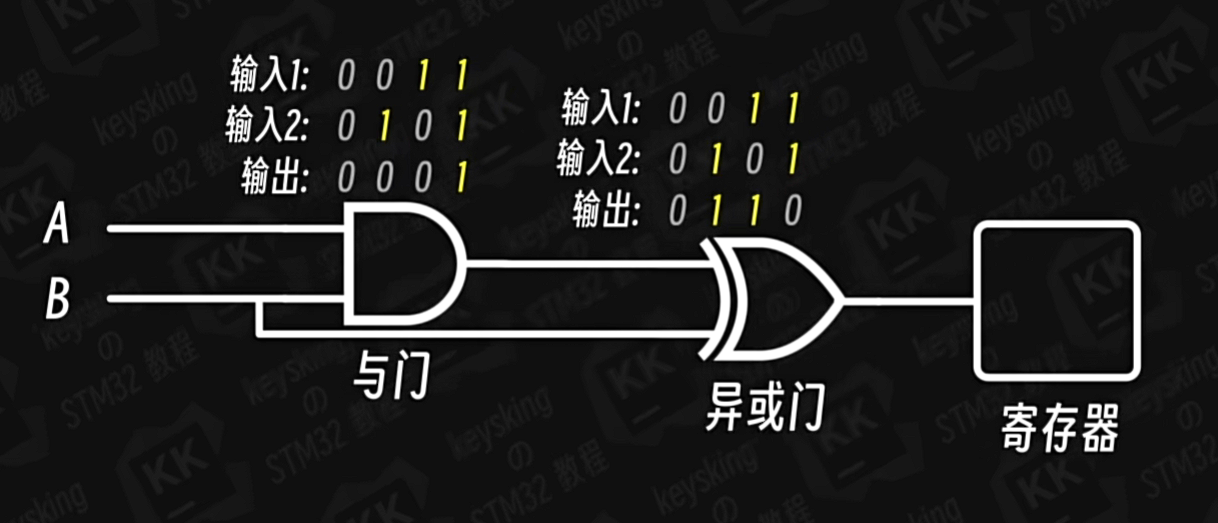

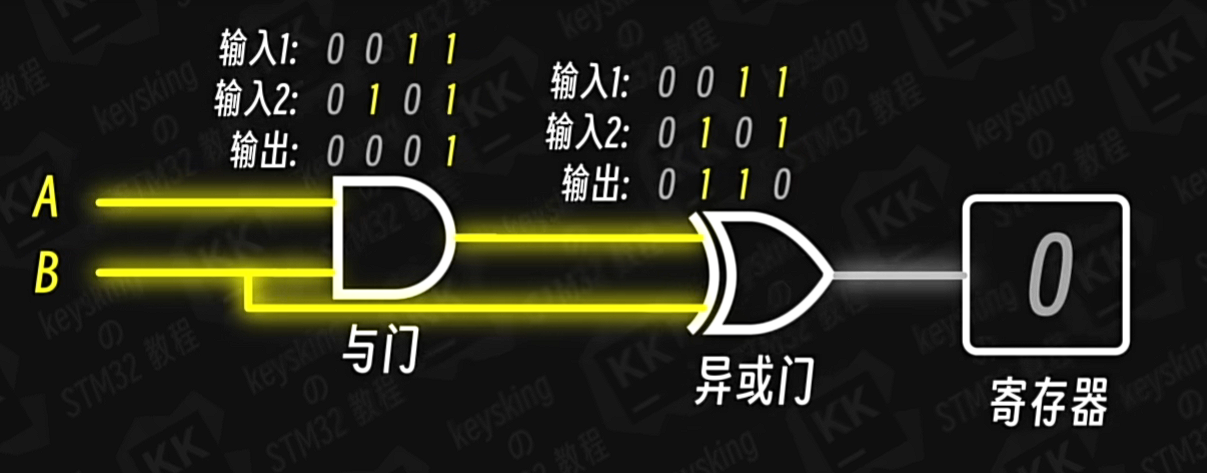

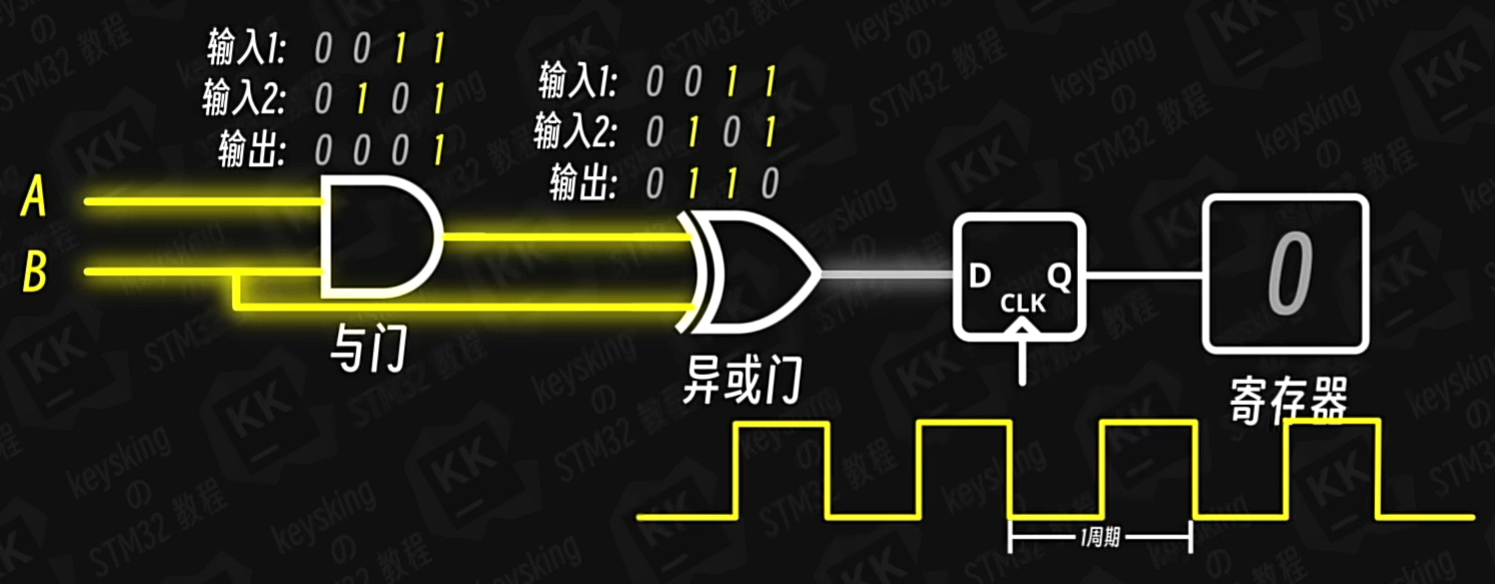

假设芯片内部存在如下这种逻辑电路:

①状态:当A、B均输入1时,与门输出1,异或门输出0,故此时寄存器的值为0

②状态:当A输入1,B输入0时,与门输出0,异或门输出0,此时寄存器的值为0

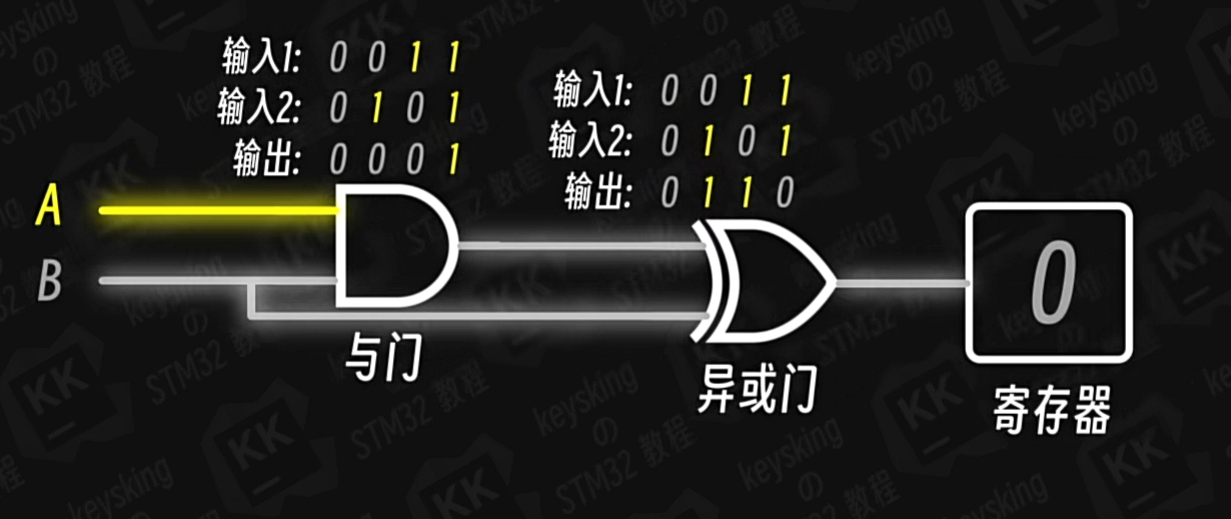

问题引出:受到逻辑门内部电路的影响,上述两种状态并不能瞬间完成,即存在过渡状态

过渡状态:

- 当B由1突变为0时,与门的输出没有立即变为0,在等待与门运算的过程中,异或门的两个输入信号一高一低,故在这个过渡状态下异或门的输出值为1,即寄存器的值也为1.

- 当与门运算完成后,与门输出0,与上述同理,异或门经一段时间再输出0,寄存器值为0(此时才达到②状态)

正因为这种过渡状态(因逻辑电路运算延时而产生的错误状态)的存在,极易对数字电路产生巨大影响

解决办法:加入边沿触发器

边沿触发器通过上升沿控制导通,通过调整合适的方波周期,使逻辑电路在一个周期完成相应的逻辑运算,规避过渡状态,避免信号混乱

这个具有一定周期的方波信号,便是我们的时钟信号

该部分内容参考于大佬视频:https://www.bilibili.com/video/BV1ph4y1e7Ey/?spm_id_from=333.337.search-card.all.click&vd_source=2c974fb85c05e13d278d1bbe4cddc944

时钟系统

时钟是嵌入式工作系统的同步节拍,时钟系统由信号源,定时唤醒器,分频器组成。常见的信号源包括晶振和RC振荡器

时钟系统是嵌入式系统中的心脏,心脏每搏动一次相当于产生一个时钟脉冲,连续的脉冲便称为时钟信号。处理器执行指令以及外设的正常工作都需要时钟的配合,当晶振不起振或者振荡不稳、停振时,嵌入式系统都是无法正常工作的。

时钟源

从时钟频率来分可以分为高速时钟源和低速时钟源,

HSI, HSE 以及 PLL 是高速时钟, 为芯片的内核和主要外设提供时钟;

LSI 和 LSE 是低速时钟,为芯片的RTC和看门狗提供时钟

外部高速时钟(HSE)

一般接石英/陶瓷谐振器及其配套电路构成的时钟电路,其频率范围为4MHz~16MHz(具体可参考相应芯片手册)

外部低速时钟 (LSE)

接频率为 32.768kHz 的石英晶体。其经过16分频即可得到准确的1 Hz的秒时钟信号,提供给实时时钟RTC

内部高速时钟 (HSI)

RC 振荡器, 频率为 8MHz。系统启动时,硬件默认使用改时钟,硬件启动完成后,一般在初始化程序中会将时钟源配置为更为稳定的 HSE

内部低速时钟 (LSI)

RC 振荡器,频率为 40kHz。 独立看门狗的时钟源只能是 LSI,同时 LSI 还可以作为 RTC 的时钟源

锁相环(PLL)

内部PLL可以用来倍频HSI RC的输出时钟或HSE晶体输出时钟。PLL 为锁相环倍频输出,可输出高频且稳定的时钟信号,其时钟输入源可选择为 HSI/2、 HSE 或者 HSE/2。倍频可选择为2~16 倍,但是其输出频率最大不得超过 72MHz(因不同芯片而异)

时钟电路设计

振荡模式

该模式下,在MCU外部连接一个晶振和两个电容。利用MCU片内集成的反相器构成振荡电路,进而产生时钟信号。

旁路时钟模式

该模式下,直接由外部电路输入一个稳定的时钟信号。外部时钟信号送入OSC_IN引脚,悬空OSC_OUT引脚。

系统时钟

外部高速时钟信号HSE

HSE是高速的外部时钟信号,可以由有源晶振和无源晶振提供

- 使用有源晶振时:时钟从OSC_IN引脚进入,OSC_OUT引脚悬空

- 使用无源晶振时:配合谐振电容,时钟从OSC_IN和OSC_OUT引脚进入

当使用HSE或HSE经过PLL倍频之后的时钟作为系统时钟SYSCLK时,若HSE出现故障,HSE和PLL都会关闭,此时HSI作为备用时钟信号维持系统时钟,直至HSE恢复正常

锁相环PLL

主要功能:倍频,然后将时钟输出到各个功能部件

PLL可分为两个:主PLL、PLLI2S(专用)

其中主PLL有两路时钟输出:

第一路是输出时钟PLLCLK用于系统时钟

第二路是输出用于USB OTG FS的时钟、RNG和SDIO时钟

专用的PLLI2S用于生成精确时钟,给 I 2 S I^{2}S I2S提供时钟

系统时钟SYSCLK

来源可以是:HSE、HSI、PLLCLK

AHB总线时钟HCLK

由SYSCLK经过AHB预分频器分频之后得到的时钟叫APB总线时钟,即HCLK

APB1总线时钟PCLK1

由HCLK经过低速APB预分频器得到,属于低速的总线时钟

APB2总线时钟PCLK2

由HCLK经过高速APB2预分频器得到,属于高速的总线时钟

其他时钟

RTC时钟

通常由LSE提供,32.768KHz

独立看门狗时钟

由LSI提供,32KHz

I 2 S I^{2}S I2S时钟

由专用的PLLI2S提供,也可由外部时钟引脚I2S_CKIN提供

时钟与系统性能的关系

- 系统超频的时候会带来性能上的提升,但是发热也会增大,影响系统稳定性

- 在设备运行时,时钟频率越高其功耗越大,发热越大,系统不稳定,需要苛刻的外部散热条件

- 外设不用的时候最好关闭其对应的时钟线

时钟与周期的关系

振荡周期

广义上指任何振动现象重复出现的时间间隔,在嵌入式领域中,振荡周期等于晶振或者RC振荡器的频率的倒数

时钟周期(节拍)

等于芯片的工作频率的倒数。在单片机中,时钟周期等于振荡周期,而在STM32处理器中,为满足性能的需要,经常对时钟进行倍频处理,此时系统工作频率可以超过晶振频率,时钟周期也就小于振荡周期。

时钟周期是嵌入式中最基本、最小的时间单位,在一个时间周期内,芯片只能完成一个最基本的动作。系统工作频率越大,时钟周期越小,系统工作速度越快

状态周期

等于两个时钟周期(节拍)

机器周期

系统完成一个基本操作,例如取指令、读写存储器的时间, 一个机器周期由若干个时钟周期(在51单片机中一般是12个时钟周期)组成

指令周期

系统从内存中取出指令和执行指令的总时间,通常由若干个机器周期组成,指令的不同,指令周期包含的机器周期数就不同,指令周期长短也就不同

总线周期

在嵌入式系统中,存储器和IO口等外设都是挂在总线上的,处理器对存储器和IO接口等外设的访问,是通过总线实现的。通过总线完成一次内存读写操作或完成一次输入输出设备的读写操作所需要的时间 ,称为总线周期,一个总线周期通常由4个时钟周期组成,这4个时钟周期分别称4个状态,即T1状态、T2状态、T3状态和T4状态

![[SUCTF 2018]annonymous1](https://i-blog.csdnimg.cn/direct/0aa85775d0b84744b624abf2469f67ec.png)