目录

- Abstract

- INTRODUCTION

- BACKGROUND AND RELATED WORK

- Trusted Execution Environment (TEE)

- Neural Processing Unit (NPU)

- Integrated NPU v.s. Discrete NPU

- Multi-tasking Requirements for NPUs

- Low NPU utilization for a single ML workload

- Simultaneous execution of both secure and non-secure tasks

- Limitation of Current NPU TEEs

- DESIGN OVERVIEW

- Goals

- Utilization

- Security

- Performance

- Threat Model

- DETAILED DESIGN

- NPU Guarder: Memory Access Guarder for NPU

- Challenges of current NPU access control

- NPU memory access pattern

- NPU Guarder

- NPU Isolator: Inner Resource Isolation for NPU

- Specialized hardware structures in NPU

- Lack of protecion for the scratchpad

- Strawman solution

- ID-based scratchpad isolation

- Lack of the NoC isolation and integrity protection

- NoC isolation

- Route integrity

- NPU Monitor: Trusted Software Module for NPU

- Interaction between NPU and CPU

- NPU Monitor

- Secure boot

- IMPLEMENTATION

- NPU Guarder

- NPU Isolator

- NPU Monitor

- EVALUATION

- Experimental Setup

- Prerequisite

- Comparative Systems

- Normal NPU

- TrustZone NPU

- sNPU

- Protected Memory Access for sNPU

- ID-based Scratchpad Isolation

- NoC Isolation

- Hardware Cost Analysis

- TCB Size Analysis

- DISCUSSION

- Multiple Secure Domains

- Memory Encryption

- Using a compromised NPU to attack CPU-side resources

- Compared with other TEE designs for ML accelerators

- CONCLUSION

Abstract

可信执行环境(TEE)通过针对安全敏感任务的硬件扩展提供强大的安全保证。由于其众多的优点,TEE 得到了广泛的采用,并从仅 CPU 的 TEE 扩展到 FPGA 和 GPU TEE 系统。然而,现有的 TEE 系统对新兴(且重要)的处理单元 NPU 的支持不足且效率低下。例如,商业TEE系统对NPU采用粗粒度和静态保护方法,导致性能显着下降(10%20%)、多任务处理能力有限(或没有)以及资源利用率不佳。在本文中,我们提出了一种安全的 NPU 架构,称为 sNPU,旨在减少 NPU 架构设计固有的漏洞。首先,sNPU提出NPU Guarder来增强NPU的访问控制。其次,sNPU利用scratchpad和NoC等NPU内部结构定义了新的攻击面,并设计了NPU隔离器以保证scratchpad和NoC路由的隔离。第三,我们的系统引入了一个名为 NPU Monitor 的可信软件模块,以最小化软件 TCB。我们在 FPGA 上评估的原型表明,sNPU 显着降低了与安全检查相关的运行时成本(从高达 20% 降至 0%),同时资源成本不到 1%。

INTRODUCTION

可信执行环境(TEE)是现代硬件辅助安全架构中的一个热门话题。我们目睹了跨各种指令集架构(ISA)实现的大量 TEE 设计,包括 Intel SGX [18] 和 TDX [42]、AMD SEV [90]、ARM TrustZone [4] 和 CCA [8] 以及 RISC- V蓬莱[26]和Keystone[54]。 TEE 为安全任务提供了一个具有隔离硬件资源的可信执行环境。由于硬件安全保证,TEE 之外的攻击者无法泄露安全任务中的秘密。

此外,随着 LLM [11]、[82]、自动驾驶和图像识别等人工智能应用的发展,将 ML 任务卸载到称为神经处理单元 (NPU) 的特定领域加速器的趋势日益增长。为了加速 AI 工作负载,NPU 利用矩阵计算单元 (MCU)、scratchpad和片上网络 (NoC) 等专用硬件结构。由于移动设备上人工智能应用的高需求,当前的移动芯片[6]、[15]、[24]、[28]、[60]、[86]、[101]、[107] 还在 SoC 中集成了 NPU 内核,以提高能效和性能。

然而,NPU 在 SoC 中的集成引入了新的攻击面,需要在 TEE 系统中考虑。这些攻击面可以分为三个方面:(1)利用受损的NPU攻击CPU侧资源:移动设备中的NPU通常具有对CPU侧安全内存的访问权限,其中包含个人面部特征等敏感数据。如果 NPU 受到损害,恶意 NPU 任务可以窃取这些秘密,对 CPU 端资源构成威胁。 (2)NPU的内部攻击:现代NPU支持多个任务的并发执行[17],[30],[49],[50],[53],[112]。然而,并发执行会带来利用scratchpad和 NoC 等内部 NPU 资源窃取机密模型或数据的风险。与此同时,另一个团队也同时披露了一个利用 NPU 内部结构的漏洞,称为 LeftoverLocals [98]。此漏洞利用加速器的本地内存(scratchpad)从正在处理的模型中提取秘密信息。 LeftoverLocals 已被证实影响 Apple、AMD 和 Qualcomm 的平台,这表明各种硬件实现中存在广泛的风险。 (3)利用CPU攻击NPU:CPU端任务可以利用NPU指令或NPU驱动程序中的漏洞[69]-[72]来攻击NPU端任务。为了解决这些安全问题,结合CPU和NPU的综合TEE变得至关重要。

一些先前的工作提出了针对 CPU-NPU 系统的粗粒度和静态 TEE 设计。一种方法是暂时将整个 NPU 指定为安全设备,并将整个 NPU 驱动程序迁移到 TEE 中。然而,该解决方案导致 NPU 资源利用率严重不足,并且由于软件堆栈的复杂性导致 TCB 较大。其他 NPU TEE [37]、[38]、[57]、[58]、[95] 重点关注内存加密和完整性保护。这些方法主要考虑对 DRAM 的物理攻击(例如冻结内存),但缺乏对 NPU 内部结构的保护,因为 NPU 内部的数据仍然是明文。此外,GPU[21]、[40]、[45]、[67]、[80]、[106]等其他加速器上的TEE系统主要关注GPU全局内存、CPU-GPU连接等的保护。 ,直接将这些机制从 GPU TEE 应用于集成 NPU 是不够的。首先,GPU TEE 中采用的 IOMMU 等隔离机制对于集成 NPU 来说效率不高,因为 NPU 需要更大的内存带宽。其次,NPU具有scratchpad和NoC等专门的硬件结构,这带来了新的攻击面。因此,NPU TEE 应该解决上述潜在的攻击,并满足两个基本要求:最小化运行时性能开销和实现更高的资源利用率。

在本文中,我们提出了 sNPU,一种用于集成 NPU 的 TEE 系统,它通过三种新颖的设计解决了上述与 NPU 相关的攻击。首先,为了防御利用 NPU 外部行为(例如内存访问)的攻击,我们引入了基于图块的内存翻译和检查单元,专门为适应 NPU 内存访问模式的特征而设计。这种设计产生(几乎)零运行时开销,同时节省了检查能量。其次,为了解决利用scratchpad和片上网络等 NPU 内结构的新攻击面,sNPU 利用scratchpad与主存储器没有关联的观察结果,并可以对其采用更细粒度和动态的隔离机制。同时,sNPU还结合了NoC隔离机制和离线路由检查,保证了NoC网络的完整性。第三,为了最大限度地减少CPU端恶意软件的潜在攻击,sNPU减少了NPU堆栈的软件TCB。 sNPU 在安全世界中引入了 NPU 监视器,仅用于必要的安全检查。与此同时,人工智能框架和 NPU 驱动程序等其他软件组件可能仍然不受信任。

我们使用 Chipyard [5] 实现了 sNPU 原型,这是一个定制的 RISC-V SoC 生成器,包括 CPU、NPU(例如 Gemmini [29] 和 NVDLA [79])以及 SoC 中的其他组件。我们通过 NoC 扩展扩展了 Gemmini 中 sNPU 的安全功能。为了建立全面的TEE系统,我们将sNPU与CPU侧TEE集成,将硬件资源划分为正常世界和安全世界。评估结果表明,sNPU 的设计对各种 AI 模型的 NPU 运行时性能(例如 DMA、Scratchpad 和 NoC)没有影响。此外,sNPU 中的安全扩展不会影响安全和非安全任务的 NPU 资源利用率。这些扩展的额外硬件成本也很小,估计不到 1%。

BACKGROUND AND RELATED WORK

Trusted Execution Environment (TEE)

TEE在当代计算机架构中得到了广泛的应用。 CPU厂商推出了自己的TEE架构,如Intel SGX和TDX[18]、[42]、ARM TrustZone和CCA[4]、[8]、AMD SEV[90]、RISC-V蓬莱、CURE和Keystone [9]、[26]、[54]和其他[10]、[19]、[27]、[89]、[116]。在移动系统中,TrustZone是TEE的主流实现。它利用安全分区的概念,有效地将硬件资源隔离到不同的分区,例如正常世界和安全世界。在这种架构设计中,不信任在正常世界中执行的任何软件,包括不受信任的操作系统和应用程序。特权软件监视器(例如 ARM EL3 或 RISC-VM 模式)负责监督安全分区,管理所有硬件资源。我们的论文基于这种 TEE 设计,将其范围扩展到包括 NPU,因此,可信 AI 工作负载可以利用安全分区内的安全硬件资源,包括 CPU、NPU 和内存。

还有其他几种 TEE 设计,例如 Enclave(例如 SGX)和 CVM(例如 SEV、CCA、TDX)。 SGX 提供了称为 Enclave 的用户级 TEE 抽象。它可以与不受信任的用户应用程序一起工作,但与它们具有很强的隔离性。不受信任的应用程序和内核无法访问 Enclave 的私有内存。 SEV、TDX 和 CCA 代表了 CVM 设计,它们利用安全处理器或轻量级 CVM 模块来控制 VM 的所有安全敏感资源。因此,CVM 可以不信任虚拟机管理程序(或 VMM)。虽然Enclave和CVM提供了更灵活的TEE抽象,但底层机制仍然依赖于安全分区——Enclave和CVM还需要定义哪些硬件资源是安全的,哪些是不安全的。扩展我们的 NPU TEE 设计以合并 Enclave 或 CVM 仍然是未来工作的一个领域。

Neural Processing Unit (NPU)

NPU [15]、[24]、[28]、[29]、[47]、[60]、[79]、[101]、[107] 是专门的硬件加速器,擅长高效执行神经网络计算。与通用处理器相比,NPU 经过专门优化,以满足神经网络的独特要求。它们提供大规模并行性、高速数据处理和矩阵计算等功能。这些功能对于处理深度学习算法中涉及的密集计算至关重要。

为了满足这些要求,NPU采用了几种特殊的硬件结构。现代 NPU 的关键单元之一是矩阵计算单元 (MCU),如tube [13]、[14]、[60]、[91]、脉动阵列 [29]、[35]、[77] 等。通过这些矩阵单元,NPU 可以在一次运算中执行乘法和卷积等矩阵计算。一些 NPU 还具有其他专用单元,用于某些特殊运算,如稀疏矩阵计算、激活函数等。

除了矩阵单元之外,NPU 还经常采用近数据计算(NDC)架构 [29]、[65]、[73]、[79] 以最大限度地减少数据检索开销。例如,神经网络中的权重预先存储在矩阵单元附近的 SRAM/scratchpad中,以便在计算过程中快速访问。这样就无需从主内存中为每个任务检索权重,从而减少了延迟和能耗。 NDC 通过最小化内存访问瓶颈来优化数据流并提高计算效率。

此外,NPU 还利用带有片上网络 (NoC) 网络的多核架构 [35]、[50]、[65]、[91]、[117] 来进一步并行化数据计算。 NoC 网络允许 NPU 内核之间直接进行数据传输,无需额外的内存加载/存储指令。开发人员可以将不同层的神经网络映射到不同的 NPU 内核并获得性能优势。

Integrated NPU v.s. Discrete NPU

集成 NPU [15]、[24]、[28]、[29]、[47]、[60]、[76]、[79]、[101]、[107] 是指专用硬件组件,直接内置于 SoC(或处理器)中。在这种配置中,NPU 与芯片的其他组件紧密集成。另一方面,分立 NPU 是独立于主 SoC 的独立硬件组件。与分立式NPU相比,集成式NPU主要有三大优势:首先,集成式NPU可以共享统一地址空间的系统缓存,无需在CPU和分立式NPU之间进行额外的内存传输或加密。其次,集成的NPU可以实现更好的带宽和更低的系统内存访问延迟,从而提高整体性能。第三,与分立式NPU相比,NPU的集成设计显着降低了能耗和芯片尺寸。因此,几乎所有移动SoC都采用集成NPU设计,有利于本地设备上运行的AI工作负载的蓬勃发展。本文重点关注集成 NPU,我们的技术也可以应用于分立 NPU。

Multi-tasking Requirements for NPUs

Low NPU utilization for a single ML workload

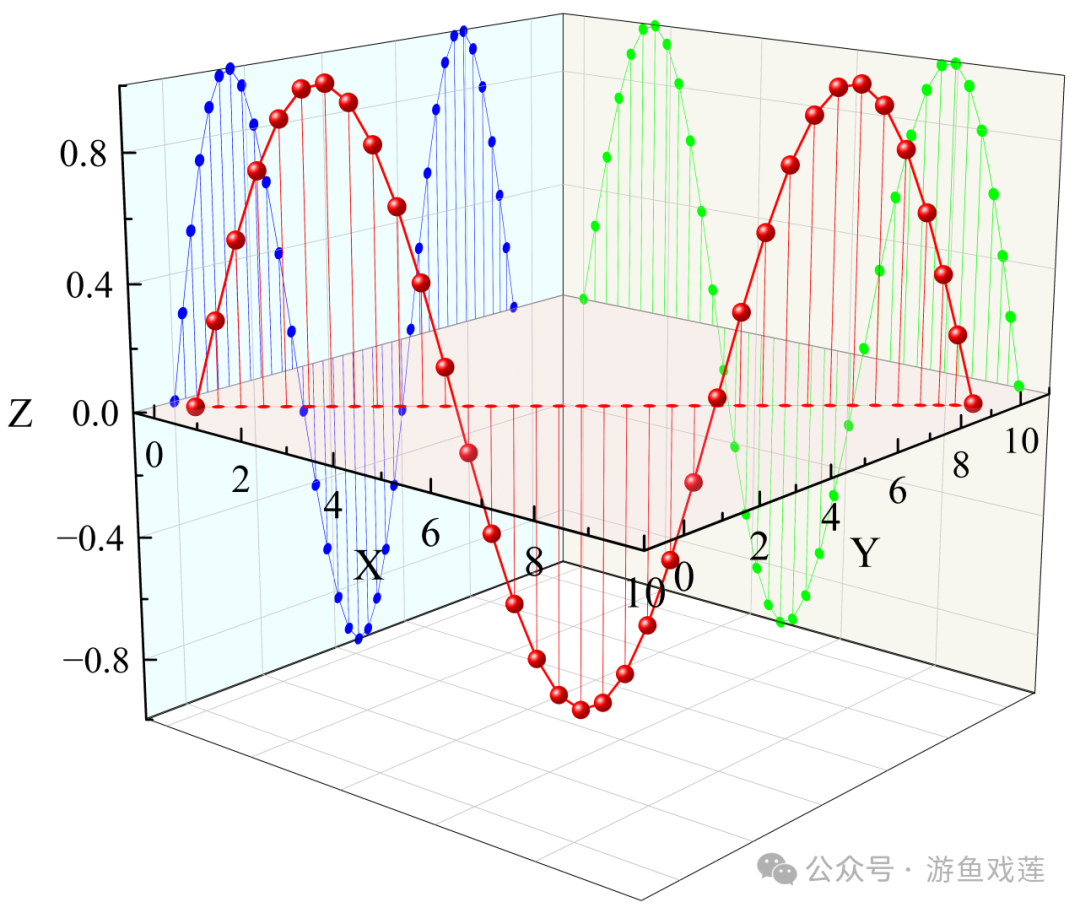

最新的NPU[3]、[32]、[47]采用了强大的计算能力(>100 TFLOPs)以及大内存容量(>100MB SRAM和>50GB HBM),有利于支持多任务需求。我们分析了在 TPU 上运行不同的 ML 工作负载时的 NPU 利用率 [47]、[112],如图 1 所示。大多数 ML 工作负载仅利用 TPU 核心中可用计算资源的不到 50%。这种未充分利用的主要原因是 MCU 的暂时空闲和内存带宽的低效使用。为了优化 NPU 的利用率,最近的研究 [49]、[50]、[112] 提出在单个 NPU 上同时执行多个 ML 任务,确保任务的服务级别协议(SLA)不受影响。

Simultaneous execution of both secure and non-secure tasks

同时执行安全和非安全任务已成为人们高度关注的话题,特别是在移动设备[30]和自动驾驶车辆[31]中。例如,开发人员可能需要同时运行机密模型以及由潜在不受信任的实体开发的其他模型。目前,智能手机供应商[94]倾向于通过静态方式来满足这一要求划分 NPU 的计算资源,例如将一个 NPU 核心专用于安全任务,同时分配另一个核心用于非安全任务。此外,安全和非安全任务的同时执行在自动驾驶领域也很明显。这里,诸如占用网络之类的安全任务可以与诸如车载娱乐之类的非安全任务同时执行。

Limitation of Current NPU TEEs

NPU 的硬件辅助安全仍然是一个新兴主题,当前的解决方案在实现 NPU 内资源的细粒度隔离和多任务支持(安全和非安全)方面面临局限性。 ITX [105]提出了人工智能加速器的机密计算。然而,ITX 专门针对 Graphcore 智能处理单元 (IPU),它是位于主板上的独立 AI 加速器。 ITX的主要重点是在用户和ITX之间建立证明,以及秘密数据和模型的安全传输。 TNPU [57]和其他NPU TEE [37]、[38]、[58]、[95]专注于内存加密和完整性保护,并使用NPU中的特定内存访问模式最小化开销。在我们的工作中,我们专注于 NPU 内结构(如scratchpad和 NoC)的隔离。即使使用内存加密(如先前作品中介绍的那样),这些结构中的数据仍然是明文。在多任务场景中,非安全任务可能与安全任务同时运行,并有可能从scratchpad中窃取秘密模型[97]、[98]。因此,我们的设计与基于加密的 NPU TEE 是互补的。

目前业界采用的是粗粒度的NPU TEE设计,我们称之为TrustZone NPU。例如,智能手机供应商通过 TrustZone 扩展来扩展 NPU 的 sMMU。具体地,sMMU中使用附加的安全位来指示相应的NPU是否是安全设备。然而,这种设计只允许将整个NPU切换到安全世界,不支持NPU内资源的细粒度和动态隔离。此外,TrustZone NPU 设计需要将整个 NPU 驱动程序迁移到具有更大 TCB 的 TEEOS 中,并在模式切换期间清除所有敏感的 NPU 上下文。由于上述限制,TrustZone NPU 的资源利用率和性能较差,如我们的评估所示(参见§VI-B 和§VI-C)。

在本文中,我们提出了一种专为集成 NPU 量身定制的新型 TEE 系统。我们的设计为scratchpad和 NoC 等 NPU 特定硬件结构实现了强大且(几乎)零成本的隔离。通过在 NPU 内提供细粒度的隔离,我们的设计可以在同一 NPU 内并发执行多个安全和非安全的神经网络任务。此外,隔离机制确保资源利用率不受影响,允许NPU驱动程序根据任务需求采取任意分配策略。综上所述,我们引入了一种专门为集成 NPU,同时支持多任务处理并最大化资源利用率。

DESIGN OVERVIEW

Goals

Utilization

现代NPU支持多网络并发执行,以提高资源利用率。因此,我们的设计还应该支持安全和非安全任务的多任务,并实现细粒度的资源隔离

Security

我们的设计应该从三个方面考虑NPU的安全性。首先,恶意用户无法利用NPU访问系统中的敏感数据。其次,非安全机器学习任务无法窃取 NPU 中安全机器学习任务的秘密模型或数据。第三,攻击者无法利用运行在CPU端的NPU软件来攻击运行在NPU中的ML任务。

Performance

我们的设计不应该影响非安全 NPU 任务的性能,并且安全任务的成本几乎为零。

Threat Model

我们系统的TCB包含:安全硬件(即安全CPU核心、sNPU硬件扩展、内存保护引擎等)、最高特权模式监视器(例如ARM中的EL3、RISC-V中的M模式)和软件在安全的世界中运行。我们不信任正常世界中的硬件和软件组件,如 NPU 驱动程序、调度程序和 ML 框架等。此外,我们也不信任 NPU 编译器,因为众所周知它很脆弱 [97]。

我们还假设安全和非安全任务可以同时运行,以满足多任务处理和 SLA(服务级别协议)要求。由于这些并发 NPU 任务可能在空间和时间上共享 NPU 资源,因此安全任务必须警惕来自在同一 NPU 上运行的其他任务的攻击,这些任务利用 NPU 内部结构中的漏洞。例如,机密的 ML 任务必须防止模型通过 NPU 的 SRAM 泄露 [98]。

sNPU没有考虑侧通道攻击和物理攻击,如冻结内存、总线监听等。这些攻击在先前的研究中已经得到了很好的研究[37],[44],[56],[61],[81],[ 93]、[95]、[108],我们的 sNPU 设计补充了之前的这些努力。

DETAILED DESIGN

我们推出 sNPU,这是一种全面且安全的 NPU 架构,旨在减轻针对 NPU 硬件和软件的攻击和漏洞。 sNPU 由三个基本组件组成:NPU Guarder、NPU Isolator 和 NPU Monitor。 NPU Guarder 作为轻量级内存转换/访问防护,有效防止来自 NPU 的未经授权的访问尝试。 NPU Isolator 专注于针对 NPU 特定架构(如scratchpad和 NoC)量身定制的轻量级内部资源隔离机制。 NPU Monitor 是一个轻量级可信软件模块,专用于执行必要的安全检查。

NPU Guarder: Memory Access Guarder for NPU

Challenges of current NPU access control

访问控制并不新鲜,但集成 NPU 遇到了一些新的挑战。首先,集成的 NPU 具有不同的内存访问路径,这可能会使统一访问控制器的设计变得复杂。其次,NPU还需要更高的内存带宽,这就需要更高效的检查逻辑。图2展示了不同类型的集成NPU,包括基于IOMMU的NPU [51]、[78]、[79]、[101]、基于MMU的NPU [21]、[86]和CPU耦合的NPU [29]。前两种类型的 NPU 是 MMIO 设备,一种利用 DMA 进行系统内存访问,另一种采用 ld/st 指令。第三种类型与CPU核心耦合,允许其访问CPU缓存。为了防止任意内存访问,一些 NPU(Type-1 和 Type-2)利用单独的 IOMMU/MMU 来限制 NPU 访问,而其他 NPU(Type-3)则依赖 CPU 端的访问检查机制。集成NPU没有统一的内存访问控制器,这增加了设计复杂性。此外,由于页表遍历、TLB ping-pong等,IOMMU/MMU 机制为 NPU 引入了不可忽略的开销。这种开销可能会导致实际应用程序高达 15% 到 20% 的性能损失 [29]。

NPU memory access pattern

与通用单元不同,NPU 是专为 ML 任务设计的特定领域加速器。 ML 任务通常涉及多个层,每个层由大量矩阵计算组成,并辅以激活函数。对于单个任务,NPU 需要有限类型的数据集:输入数据、权重(包括偏差)以及输出结果,如图 3 所示。

NPU 利用直接内存访问 (DMA) [109] 将数据从系统 DRAM/HBM 提取到 NPU 内 SRAM(即scratchpad)中。 NPU 驱动程序使用特定的内存分配器来管理这些 DMA 缓冲区(NPU 保留内存)。例如,Android/Linux 引入了 ION 堆 [21]、[63],NVIDIA Tegra 使用 NVMA [78],Qualcomm MSM 使用 PMEM [62] 作为为 NPU 内存设计的内存分配器,与系统内存分开。为了保留连续的 DMA 缓冲区,NPU 驱动程序要么在系统启动期间固定内存,要么使用连续内存分配器(CMA)[102]。在将任务卸载到NPU之前,NPU驱动程序需要在NPU保留的内存中分配多个块,并且NPU将每个块进一步划分为多个块。在执行期间,NPU 通过将权重从系统内存加载到 SRAM 来启动计算序列。随后,它直接从系统内存或从 SRAM 检索输入值,SRAM 保留前一层计算的输出结果。计算完成后,NPU 将输出结果存储回系统内存。总之,NPU 在一次计算期间只需要加载和存储有限的数据块(输入、权重和输出),并且每个块(属于数据块)的 VA 到 PA 映射是一致的。这种内存访问和分配模式可用于克服 NPU 内存访问控制的挑战。

NPU Guarder

图 4 展示了我们的 NPU Guarder 设计,这是一种利用 NPU 中特定内存访问模式的轻量级内存访问控制器。与MMU或IOMMU相比,它有两个主要优点:(1)它具有轻量级设计,无需检查开销,(2)它可以集成在NPU内部。

首先,为了消除传统基于分页的内存访问控制的运行时开销,NPU Guarder 采用粗粒度内存检查和细粒度翻译机制。对于存储器检查,它利用记录连续存储器区域的访问权限的检查寄存器,因为移动系统中的敏感数据通常存储在预先分配的安全存储器区域(例如,TrustZone安全存储器区域)中。至于地址转换,NPU Guarder 在图块级别(例如输入图块和输出图块)提供细粒度的转换寄存器。每个转换寄存器将特定区域从虚拟地址映射到相应的物理地址。与很少修改的检查寄存器不同,转换寄存器可以在 NPU 计算之前更新(如果需要)。

其次,NPU Guarder 将这些检查和转换寄存器集成在 NPU 内核内部,位于 DMA 引擎之前。与独立模块(例如IOMMU)相比,集成设计降低了SoC的复杂性。此外,由于内存检查和转换是在 DMA 请求级别而不是内存数据包级别执行的,因此与 IOMMU 相比,NPU Guarder 可以节省额外的能量。当接收到 DMA 请求时,DMA 引擎将其分为多个固定大小的内存数据包(例如 64 字节)。因此,NPU Guarder 仅检查一次(并且节省能源),而 IOMMU 需要在内存数据包级别检查 O(N) 次。

NPU Isolator: Inner Resource Isolation for NPU

Specialized hardware structures in NPU

为了优化人工智能工作负载,NPU 结合了专用硬件结构,例如scratchpad和 NoC(片上网络)。scratchpad是高速、低延迟的 SRAM,需要程序员显式管理。由于 NPU 需要更大的内存带宽,scratchpad/SRAM 已广泛应用于现代 NPU [32]、[41]、[47]、[66] 中,以加速 AI 工作负载 [20]、[33]。与高速缓存不同,scratchpad保存的数据只能通过其索引(而不是全局地址)访问,与系统内存没有任何关联。它不包括命中或未命中等机制,并且不维护内存一致性。 NoC是连接多个NPU核的片上网络。 NoC 对于多核 NPU 来说是不可或缺的[32]、[47]、[50]、[66]、[92],因为它可以实现计算资源的可扩展,同时通过互连解决内存带宽不可扩展的问题。大多数 NoC 网络都使用基于包的协议 [115]。一个包通常由一个头部弹片、多个身体弹片和一个尾部弹片组成。 head flit 包含路由信息,指定源核和目标核之间的路径(例如,x:+4、y:+2)[65]、[85]。

Scratchpad 和 NoC 是 NPU 中用于加速 AI 工作负载的专用结构,但它们也引入了新的漏洞。

Lack of protecion for the scratchpad

由于scratchpad由程序员显式管理,因此受损的编译器或 NPU 驱动程序可以轻松对其发起攻击。例如,NPU驱动程序可以分配一个已被另一个任务使用的scratchpad条目,并且NPU编译器可以强制读取scratchpad中的内容而不需要之前写入。最近披露的一个漏洞:LeftoverLocal [97] 允许从受害者进程创建的加速器本地内存(scratchpad)中恢复数据。现实世界的 PoC 已经开发出来,攻击者可以监听另一个用户的交互式 LLM 会话(例如 llama.cpp)。由于缺乏底层硬件隔离支持,LeftoverLocals 对各种平台产生了广泛的影响,包括 Apple、Qualcomm、AMD 和 Imagination GPU。

我们对现有的内存保护机制进行了详细的研究,但这些机制并不适合scratchpad结构。图 5 说明了现有的缓存和内存保护机制。例如,CAT [44] 和页面着色 [108] 用于减轻缓存侧通道攻击。分页、标签内存[23]和段机制[111]用于内存隔离。然而,这些机制通常会引入不小的开销,由于其高带宽要求,因此不适合scratchpad。

Strawman solution

表 I 比较了scratchpad的各种隔离机制。刷新所有内容在任务调度之前将其放在scratchpad中是一种简单的方法,但存在一些固有的局限性。例如,刷新不仅仅是将scratchpad中的内容清零,还需要在调度之前保存和恢复任务的上下文。目前集成NPU的调度粒度是在操作内核级别[12]、[68],并且由于算子有限,NPU必须与CPU一起执行细粒度的异构计算。然而,这种细粒度的刷新粒度可能会导致显着的性能开销(在我们的评估和其他工作中大于 25% [112])。更重要的是,只有当scratchpad在不同任务之间临时共享时,刷新才起作用,而当前的 ML 任务往往假设scratchpad在空间上共享以实现更好的性能。即使仅考虑分时,刷新的粒度也会成为性能与 ML 任务的服务级别协议 (SLA) [25]、[110] 合规性之间的权衡。如前所述,频繁的刷新会带来相当大的性能开销,而较粗粒度的刷新可能无法满足SLA要求,资源利用率较低(NPU正在等待CPU计算)。这种困境已被多项研究证实[49]、[50]、[112]。

另一种简单的解决方案是将scratchpad划分为多个区域,如图 6(a) 所示。该分区机制已经在CPU和GPU TEE中得到应用,如ARM TrustZone [4]、NVIDIA MIG [80]。然而,这种机制存在碎片问题,导致难以在运行时调整隔离边界[59]。此外,由于资源利用率低,分区还在现实世界的 NPU 任务中引入了不小的开销(参见§VI-C)。

ID-based scratchpad isolation

在NPU Isolator中,我们提出了一种专门针对scratchpad的基于ID的隔离机制,如图6(b)所示。关键的见解是scratchpad条目和系统内存之间没有地址关联,允许我们在任何scratchpad条目中存储数据。因此,scratchpad可以采用比缓存和内存更细粒度、更动态的隔离机制。我们首先添加 NPU 内核和scratchpad的 ID 状态,值 1 表示安全,0 表示非安全。设置NPU核心的ID状态只能通过安全指令来完成。对于scratchpad,我们定义了两种访问规则: (1) 对于独占scratchpad:我们禁止 NPU 核对具有不同 ID 状态的scratchpad条目进行任何读操作,但允许 NPU 核强制向scratchpad写入数据输入,并自动将scratchpad ID 状态更新为 NPU 内核的状态。 (2) 对于共享scratchpad:我们禁止非安全 NPU 内核访问(读和写)安全scratchpad条目,否则,安全 NPU 内核会强制将访问的scratchpad的 ID 状态设置为安全。专用安全指令用于将scratchpad状态从安全重置为非安全。通过执行这些规则,我们可以实现每个scratchpad条目的细粒度和动态隔离,并将分配策略与其安全检查分离。它允许 NPU 驱动程序重用任何分配实现更好的scratchpad利用率的策略。此外,由于每个scratchpad条目具有较大的有效负载(例如,≥128b),因此一位 ID 状态的资源开销可以忽略不计(<1%)。

Lack of the NoC isolation and integrity protection

除了保护scratchpad之外,NPU 隔离器还确保 NoC 网络的隔离和完整性。 NPU 可以通过跨多个 NPU 核心编排不同级别的 ML 模型来加速 ML 任务,从而允许直接通过 NoC 网络传输中间结果。它显着减少了从内存存储和重新加载数据的开销。然而,NoC 网络的这种使用通过破坏路由完整性引入了新的攻击面,如图 7 所示。路由完整性无法像 CPU TEE 中采用的代码完整性一样得到保护。例如,如果 NPU 调度程序受到损害,它可以将恶意任务调度到错误的 NPU 核心。因此,攻击者可以拦截从源核心传输的秘密中间结果,或者向受害核心发送恶意 NoC 数据包。通过篡改 NoC 网络的路由完整性,攻击者可以操纵整个 ML 任务。

NoC isolation

为了防御NoC网络上的上述攻击,NPU Isolator引入了一种轻量级的NoC身份验证机制,称为peephole,并具有离线路由完整性检查功能,如图8所示。peephole机制为NoC数据包生成身份(head flit)位于源核心,在NoC网络中传播。当目标核收到此 NoC 数据包时,目标核中的窥视孔根据其身份验证此 NoC 请求。 NPU核心的ID状态可以作为窥视孔机制中的有效身份。例如,源自安全 NPU 核心的数据包包括安全位作为其标识。如果目标核是普通NPU核,则认证过程失败并且该NoC请求将被拒绝。否则,安全 NPU 核心将接受此请求并接收以下数据包(主体传输)。

Route integrity

Peephole机制提供了NoC网络中的隔离,但是,为了确保全面的NoC保护,我们还需要考虑在多个NPU核上运行的ML任务的路由完整性。除了计算 ML 任务代码的哈希值并将其与预期测量值进行比较的代码完整性检查之外,路由完整性检查还确保实际的 NoC 路由与用户的期望一致。例如,在需要 2 × 2 NoC 网络的安全 ML 任务的情况下,恶意 NPU 驱动程序可能会为这些任务分配 1 × 4 NPU 核心,这可能会导致 ML 任务在执行过程中与两个意外的 NPU 核心交互。因此,在将ML任务加载到多个NPU核心之前,我们需要验证NPU核心的实际分配是否与安全任务中定义的预期NoC配置相匹配。我们将在§IV-C 中介绍更多细节。

NPU Monitor: Trusted Software Module for NPU

NPU 包含一个由各种组件组成的大型软件堆栈,例如 AI 框架(例如 TensorFlow [1]、PyTorch [83])、编译器(例如 TVM [12]、CANN [88])和 NPU 驱动程序。将整个软件堆栈包含在 TCB 中可能会带来潜在的漏洞和安全风险。为了缓解这个问题,我们坚持安全与策略解耦的设计原则[99],并且只将一个小型监视器移入安全世界。该监视器负责执行安全检查、管理关键资源,并充当安全 CPU 和 NPU 之间的桥梁。

Interaction between NPU and CPU

图9展示了整个TEE系统,包括CPU、NPU和内存。 NPU 和 CPU 之间的交互有两种常见的方法:内存映射 I/O (MMIO) 接口和特定指令(例如矩阵扩展 [7]、[43]、[74]、[76] 或 RoCC [ 16])。建立完整的信任环境中,sNPU 限制 CPU-NPU 交互,仅允许安全 CPU 与安全 NPU 交互。具体来说,安全上下文(例如 ID 状态和检查寄存器)只能由安全 CPU 使用专用于 sNPU 设计的新指令来设置。

NPU Monitor

NPU 监视器在确保多个安全 ML 任务的机密性和完整性方面发挥着关键作用。它由几个 shim 模块组成:上下文设置器、可信分配器、代码验证器和安全加载器。值得注意的是,NPU 监视器仅适用于安全的 ML 任务。而对于非安全任务,我们不应用任何软件检查,仅依靠硬件机制来保证安全任务和非安全任务之间的隔离。

上下文设置器负责设置NPU安全上下文,其中包括NPU的ID状态、安全任务的检查和翻译寄存器。 NPU上下文决定了NPU可以访问的硬件资源,例如系统内存和scratchpad

可信分配器负责在保留的安全内存中分配内存缓冲区,例如输入/输出数据和安全任务模型。它还检查scratchpad是否有重叠。

代码验证器首先将安全任务的代码和敏感模型加载到安全任务队列中。然后,它根据用户的期望计算并验证任务代码的测量结果。

安全加载器首先保证 ML 任务的路由完整性。与传统的 CPU TEE 不同,ML 任务可以利用与 NoC 网络连接的多个 NPU 核心。安全加载程序验证调度的 NPU 内核是否与预期 NoC 网络的拓扑匹配。验证路由完整性后,安全加载器将 ML 任务上传到相应的 NPU 内核中。

除了 shim 模块之外,NPU Monitor 还有两个辅助组件:trampoline 和安全任务队列。 Trampoline 充当非安全 NPU 驱动程序和 NPU Monitor 之间的中介(用于数据传输),而安全任务队列则存储用于调度的安全 NPU 任务。

Secure boot

sNPU 的安全启动流程与之前的工作类似[4]、[21]、[57]。在机器启动期间,安全CPU验证可信加载程序的最小代码,然后加载并验证可信固件[84]、[104]。可信固件在加载正常世界中运行的软件之前,会进一步加载和验证可信世界中的软件,例如 TEEOS [103] 和 NPU Monitor。此安全启动链的信任根保留在 SoC 中。

IMPLEMENTATION

NPU Guarder

图 11 描述了 NPU Guarder 的微架构,强调了原始设计之间的关键区别。在 NPU Guarder 中,安全控制器配置检查寄存器和转换寄存器。检查寄存器包括两个主要字段:内存范围及其权限(读、写等)。这种基于图块的机制特别适合处理连续数据,这是 NPU 中的常见场景。转换寄存器维护从物理地址到虚拟地址的范围映射。当DMA请求到达时,它根据转换寄存器将请求的虚拟地址转换为相应的物理地址。随后,物理地址经过权限检查,只有经过身份验证的请求才会被发送到 DMA 引擎。

NPU Isolator

NPU 隔离器包含两部分:scratchpad隔离和 NoC 隔离。为了实现scratchpad的动态隔离,我们只对scratchpad接口和字线进行了轻微的扩展。除了常规数据之外,每个scratchpad行现在还包含用于 ID 状态的附加位。考虑到每条字线包含一个大数据块(输入/输出scratchpad为128位,累积scratchpad为512位),一到两位的增加可以忽略不计。在本地scratchpad中,写操作不受限制,并且会覆盖 ID 状态。然而,仅当字线的ID状态与NPU的状态匹配时才允许读取操作。对于全局scratchpad,读写操作均受到限制,禁止普通 NPU 内核访问安全字线。

为了支持NoC基于窥视孔的隔离,我们重新设计了路由器控制器。每个NPU核心都有自己的路由器控制器,包括发送和接收引擎,如图12所示。当发送引擎收到发送请求时,路由器从空闲状态转变为窥视状态,并生成相应的认证ID。随后,它向目标核心触发身份验证请求并等待返回数据包。如果身份验证检查通过,路由器将继续将整个数据传输到目标核心。接收引擎具有镜像工作流程。路由器收到认证请求后,验证认证ID,并等待后续数据包。一旦接收到所有数据并将其写入scratchpad,路由器就会转换回空闲状态。值得注意的是,身份验证仅发生一次。验证后,路由器映射锁定,防止其他核心使用该通道。

NPU Monitor

我们在 RISC-V CPU 中使用 PMP 保护 [96] 在安全域内实现了 NPU 监视器。 NPU Monitor 中的主要代码是模型解密和代码完整性测量等加密功能。此外,我们还开发了一种可信分配器,可以有效地在安全内存中分配特定大小(例如scratchpad大小)的内存槽。上下文设置器和安全加载器分别保证 NPU 安全上下文和 NoC 路由的正确性。为了促进与非安全域中的软件的通信,我们设计了一个蹦床协议,其中包括函数 ID、参数和共享内存。

EVALUATION

Experimental Setup

我们在 Chipyard [5] 之上实现了 sNPU 的硬件原型,这是一个定制的 RISC-V SoC 生成器,旨在评估全系统硬件。 NPU设计的微架构参考了Gemmini [29]和AuRORA [50],这是一种基于脉动阵列的DNN加速器。我们将sNPU的所有安全扩展融入到Gemmini中,并进一步实现了体内发送/接收引擎和路由器模块以支持基于NoC的多核NPU。对于CPU端TEE,我们的实现基于Penglai [26],一个RISC-V TEE系统。我们扩展了现有的蓬莱TEE,将所有硬件资源划分为正常世界和安全世界。这种划分确保了这两个世界之间的硬件资源的强隔离,增强整个系统的安全性。我们通过使用 FireSim [48](一种周期精确、FPGA 加速的 RTL 模拟器)运行端到端 DNN 工作负载来评估 sNPU 性能。配置如表二所示。

在我们的评估中,我们选择了六种不同的最先进的 DNN 推理模型,包括 GoogleNet [100]、AlexNet [52]、YOLO-lite [39]、MobileNet [36]、ResNet [34] 和 Bert [22]。这些 DNN 包括用于主流计算机视觉 (CV) 和自然语言处理 (NLP) 的神经网络,具有不同的模型大小、DNN 内核类型、计算和内存要求。

Prerequisite

在我们的评估中,我们排除了离线开销,例如任务复制和模型解密。这些操作可以提前执行,并且不会影响运行时性能。此外,现代移动 SoC [51]、[94] 支持将设备的数据(例如相机)直接传输到安全存储器。因此,没有额外的副本来加载敏感输入数据。在本文中,我们主要关注 sNPU 与其他比较系统之间的运行时性能分析。

Comparative Systems

Normal NPU

普通NPU是指我们评估中的基线,没有任何安全保护机制。

TrustZone NPU

TrustZone是移动设备中使用最广泛的TEE系统。为了支持 TrustZone 中的隔离 NPU 内核,当前 SoC 供应商通过 TrustZone 扩展(S/NS 位)增强了 NPU 的 sMMU/IOMMU,并将整个 NPU 驱动程序迁移到安全世界中。在评估中,我们为 TrustZone NPU 上的内部scratchpad添加了额外的保护机制(例如刷新重载和分区),以满足多任务要求。

sNPU

sNPU 包含 NPU Guarder 和 Isolator 作为附加安全模块。我们将比较 sNPU 隔离机制与前面提到的方法的效率。

Protected Memory Access for sNPU

我们首先评估不同的内存访问控制,例如使用增强型 IOMMU(TrustZone NPU 采用)和 NPU Guarder(sNPU 采用)对端到端性能的影响,如图 13-(a) 所示。我们使用不同数量的 IOTLB 条目来评估 IOMMU 的性能。例如,“IOTLB-4”表示存在四个 IOTLB 条目。评价结果显示与 NPU Guarder 设计相比,IOMMU 将为 DNN 推理吞吐量带来不可忽视的减慢。这是因为 IOMMU 有一些固有的性能开销,例如 IOTLB 未命中、页面行走和 IOTLB 刷新。虽然增加 IOTLB 条目的数量可以在一定程度上缓解这些问题,但由于ping-pong场景,即使有 32 个 IOTLB 条目,实际 NN 工作负载的性能仍然会损失近 10% [50]。如果考虑硬件开销较少的四个条目,损失将高达近20%。相比之下,sNPU 利用翻译/检查寄存器来执行基于图块的翻译和权限检查。因此,sNPU 不会遭受上述性能损失。

除了性能开销之外,IOMMU 还面临额外的能源成本(高达 10% [55], [114]),特别是在低功耗场景下。当前的移动 SoC [51]、[94] 为 NPU 提供低功耗模式来执行长时间运行的后台 ML 任务(例如,眼睛和手势检测)。我们对请求数进行进一步分析,这是一个指标能源成本,介于 IOMMU 和 NPU Guarder 之间。对于 IOMMU,IOTLB 条目会针对每个内存事务进行匹配,无论事务地址是否连续。相比之下,我们的翻译和检查寄存器可以容纳连续的地址块,只需要一个访问请求。如图 13-(b) 所示,与 IOMMU 相比,使用基于图块的转换寄存器仅需要大约 5% 的转换请求。因此,NPU Guarder 模块的功耗开销可以忽略不计。

ID-based Scratchpad Isolation

当前的 NPU 利用scratchpad来存储模型的输入、权重和其他中间结果,这些结果可能由多个 NPU 任务显示。 sNPU 提出了针对本地和全局scratchpad的基于 ID 的动态隔离,我们将该机制的性能与当前 TrustZone NPU 中采用的前述稻草人解决方案进行了比较。第一个稻草人解决方案是冲洗在同一核心上调度另一个 NPU 任务之前,scratchpad中的内容。值得注意的是,刷新并不是一种完全安全的机制(参见§IV-B),它仅适用于独占scratchpad(无空间共享),并假设攻击者在刷新命令之前不会执行任何任务。

即使在时间共享的场景中,刷新仍然会导致性能开销。我们评估不同刷新粒度下 ML 工作负载的端到端执行时间,如图 14 所示。这里我们选择三种粒度:平铺、层和五层。为了保证正确性,刷新并不是简单地将scratchpad清零,而是需要保存执行上下文并在下次调度时恢复它。评估结果显示,细粒度的冲刷粒度会带来不可忽略的开销:在tile粒度下大约有25%的减速。粗粒度刷新开销较小,但很难满足 ML 工作负载的 SLA,因为高优先级任务无法及时抢占低优先级任务 [49]、[50]、[112]。

第二种稻草人解决方案是静态分区,其中片上scratchpad被分为可信部分和不可信部分。我们设置了不同比例的可信部分和不可信部分:四分之一、二分之一和四分之三。为了评估实际应用程序的分区性能,我们将六个工作负载分为三组,每组包含两个工作负载。一个工作负载被分配在可信世界中运行,而另一个工作负载则在不可信世界中运行。两个工作负载在各自的 NPU 核心上并行运行,但使用共享scratchpad。图 15 显示了三组中每个工作负载的标准化执行时间与其各自的执行时间的比较。每组中的左列说明安全工作负载的性能,而右列代表非安全工作负载。不同的颜色表示scratchpad分区的不同比例。例如,紫色列(每组中最左边和最右边的列)表示scratchpad的四分之三分配给受信任的工作负载,而其余的则分配给不受信任的工作负载。

与静态分区相比,我们基于ID的隔离机制允许基于不同策略对共享scratchpad进行动态和细粒度的分离。红色列(每组的中间列)代表我们具有总体最佳策略的机制(最大限度地减少两个工作负载的端到端延迟)。不同的工作负载会根据scratchpad的大小和 NPU 驱动程序表现出不同的行为可以为不同的工作负载分配不同比例的scratchpad。 Yololite 和 mobilenet 对scratchpad大小不敏感,因为它们精心设计了计算和内存交错管道。然而,alexnet和bert的性能根据scratchpad大小的不同而波动剧烈。当将这些不同的工作负载组合在一起时,静态分区策略不能普遍适用于所有情况。

总之,我们基于 ID 的scratchpad动态隔离机制提供了更加灵活和自适应的解决方案,可以提高scratchpad的利用率,同时满足不同 ML 工作负载的不同需求。

NoC Isolation

我们评估了多核 NPU 上使用窥视孔和其他机制进行 NoC 隔离的开销。核心间通信的一种简单隔离机制是利用专用共享内存(即软件 NoC)。例如,将中间数据存储在共享内存中,然后从另一个 NPU 核心重新加载。在此过程中,我们限制共享内存的访问权限,以禁止任何未经授权的访问。然而,这种基于内存的通信成为 NPU 任务的瓶颈。现代NPU利用直接NoC网络(绕过内存)来改善多核之间的数据传输,从而通过缓解内存墙问题来显着提高整体芯片性能。我们在这个NoC网络上添加了窥视孔机制,保证了NoC数据包的身份并拒绝任何恶意请求。

图 16 显示了使用软件 NoC(使用共享内存)、未经授权的 NoC 和带有窥视孔的 NoC 之间的微测试结果。 “交易大小”是指要传输的scratchpad行数。微测试仅考虑软件NoC的理想情况,假设只有NPU请求访问主存。即使在这种理想情况下,我们观察到我们的窥视孔机制几乎可以将延迟减少三分之二,从而将延迟提高三倍与内存共享相比,带宽得到了改善。此外,与未经授权的NoC相比,窥视孔没有性能损失,因为认证仅发生在第一个磁头片中,没有额外的时钟。

为了测试 NoC 窥视孔机制在现实场景中的性能,我们分析了图 17 中所示的工作负载。值得注意的是,NN 工作负载的端到端性能与映射策略紧密耦合,映射策略与映射策略正交。我们工作的主要重点。出于测试目的,我们仅使用可行的映射策略,但可以通过精心设计的映射方法来实现进一步的改进。图 17 显示了不同工作负载的整体性能(通过未经授权的 NoC 标准化),利用软件 NoC 和基于窥孔的 NoC 进行数据传输。通过利用基于窥孔的 NoC,我们观察到与软件 NoC(使用共享内存)相比,不同 ML 工作负载的总体执行时间减少了近 20%,因为它消除了 NPU 核心和内存之间的冗余内存副本。

Hardware Cost Analysis

我们在 FPGA 上综合 sNPU,并将其硬件资源与基准 NPU 和 TrustZone NPU 进行比较。图 18 说明了 sNPU 在 LUT、RAM 和 FF 方面所需的额外资源。我们评估 sNPU 的不同配置:S Reg(翻译/检查寄存器)、S Spad(基于ID的scratchpad隔离)和S NoC(带窥视孔的安全NoC),而TrustZone NPU仅采用IOMMU进行访问控制。我们的评估表明 sNPU 产生的硬件资源开销最小。与基准 NPU 相比,它仅需要额外 1% 的 RAM 资源 (S Spad),对 LUT 和 FF 的影响可以忽略不计。此外,当将 sNPU 与 TrustZone NPU 进行比较时,IOMMU 涉及复杂的 IO 页表遍历,这会消耗更多的硬件资源。

TCB Size Analysis

sNPU 设计仅引入带有 NPU 监视器的小型软件 TCB 大小,如第 §IV-C 节中所述。 NPU Monitor 代码仅包含 12,854 LoC,而加密代码则占 10,781 LoC。第二大功能代码是可信分配器,包含 1,564 个 LoC。与包括 ML 框架(例如 TensorFlow [1] 的 330,597 LoC、ONNX [68] 的 309,366 LoC)和 NPU 驱动程序(例如 NVDLA [79] 的 631,063 LoC)在内的整个 NPU 软件堆栈相比,TCB 的总大小NPU 监视器较小。

DISCUSSION

Multiple Secure Domains

sNPU 设计灵活,可扩展以支持多个安全域。然而,本文重点关注两个硬件领域(安全和普通),因为它与 TrustZone 等当前的移动系统架构保持一致。增加每个 NPU 核心的 ID 位可以实现更安全的域,但它会带来硬件资源使用量增加的代价,特别是在scratchpad中。平衡所需的安全域数量与相关的硬件成本至关重要。

除了硬件定义域之外,sIOPMP 还支持单个硬件定义域内的多个软件定义域。 NPU 监视器可以检查和隔离不同安全 ML 任务之间的 NPU 资源和系统内存。虽然软件定义域引入了一些检查开销,但它不会影响在安全域外运行的 ML 任务。

Memory Encryption

当前的 NPU TEE 还采用内存加密 [2]、[37]、[57]、[75]、[95]、[113] 来防止物理攻击。 NPU在DRAM中的所有数据都是密文,具有加密和完整性保护。当数据加载到 NPU 缓存或scratchpad时,内存加密引擎会将数据解密为明文。一些先前的工作已经设计了专门针对 NPU 访问模式的完整性方案。另一方面,sNPU 主要关注 NPU 内结构(例如scratchpad和 NoC)的隔离,即使使用 DRAM 加密,这些结构仍然不受保护。因此,sNPU通过解决多任务场景中针对内部结构的攻击来补充加密的NPU TEE。

Using a compromised NPU to attack CPU-side resources

NPU 在 SoC 中的集成通常需要与 CPU 共享硬件资源,例如统一内存和系统缓存(如果存在)。一个妥协的NPU 可能会对这些共享资源中的数据和代码执行攻击。例如,最近披露的一个漏洞[64]表明,通过利用CPU和GPU之间的统一内存,攻击者可以在存在内存标记扩展(MTE)的情况下实现内核代码执行。针对这一安全挑战,sNPU引入了NPU Guarder,旨在严格规范NPU的访问行为(例如禁止NPU访问CPU拥有的敏感数据和代码)。

Compared with other TEE designs for ML accelerators

先前的研究提出了 ML 加速器的替代 TEE 设计,重点关注可信 I/O 总线、最小化软件 TCB 并实现内存加密。 CRONUS [46]提出了一种名为 MicroTEE 的基于软件的 TEE 架构,它将一个整体 enclave 划分为多个微 enclave。每个微飞地都封装了异构计算任务中的一种特定类型的计算。 CRONUS主要强调TEE的故障隔离以及适用于各种硬件加速器的基于软件的设计。 AccShield [87]旨在在CPU和TPU之间建立混合TEE。它提供强大的端到端机密性和完整性保护,特别是对于不可信的 PCI-e 连接。确保 PCI-e 通道的安全对于离散加速器至关重要。其他 GPU TEE [9]、[45]、[106] 专注于定制可信 I/O 总线和 MMIO 接口,这限制了正常世界的 GPU 控制。另一方面,sNPU 主要关注 ML 加速器中内部结构的隔离,例如scratchpad和 NoC。此外,与其他专注于离散加速器的TEE设计不同,sNPU针对的是集成NPU,它与CPU共享统一的内存空间。因此,像安全 PCIe 通道这样的保护与我们的设计是正交的。

CONCLUSION

本文提出了一种集成 NPU 的综合 TEE 设计:sNPU。首先,它使用基于图块的转换和检查实现了强隔离并减轻了 NPU 的内存检查开销。其次,它对利用 NoC 和scratchpad等 NPU 内资源的新攻击面进行分类,并专门针对这些资源提出了细粒度的隔离机制。第三,它最大限度地减少了 NPU 堆栈的软件 TCB。我们在 FPGA 中实现了一个原型,并在各种现实世界的人工智能工作负载上对其进行了评估。