异常的流程:

首先: 在硬件上阶段: 这里是4大步3小步

然后是 异常处理: 这里主要是保存现场,进行异常处理

然后是 异常返回: 主要指 恢复现场, 再跳转回去。

首先硬件上:

4大步3小步。

第一大步: 当异常发生时,会将 CPSR的内容保存到目前模式的SPSR中,不知道需不需要手动执行。

第二大步: 第一小步,硬件会自动的设置 异常的类型,主要是设置 CPSR的 0-4 位,第二小步, 然后切换到arm 状态下,就是硬件自动设置 CPSR的 第5位 为0 , 第三小步,同时cpu 会自动的关闭CPSR的 中断, 也就是设置I位。

第三大步: 在进入异常处理之前,硬件会自动的将当前的PC的值减4 放到LR中。(它的作用是,将来会将LR的值,赋值到PC中,这里在赋值到PC中,LR的值, 会由于异常的类型的不同,计算的方法也不同)。

第四大步: 硬件会自动的跳到 中断向量表,中断向量表只是保存了一个 跳转的地址。cpu 根据异常的类型跳转到 固定的内存地址。

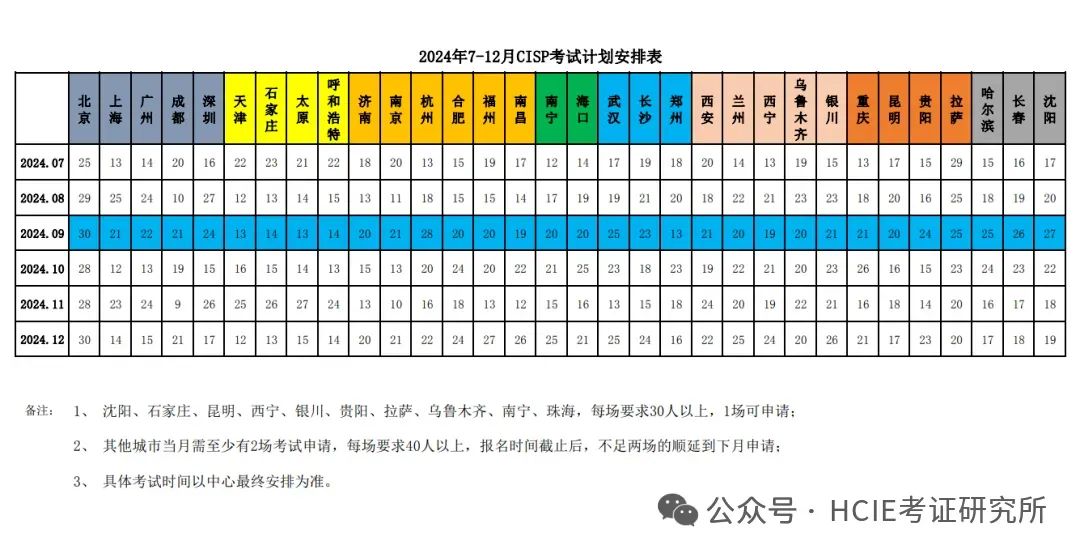

异常向量表如图

异常处理:

保存现场,进行处理。

在异常处理的最开始, 需要先要保存现场,

STMFD SP_excep!, {R0 – R12, LR_excep}这是将所有的寄存器全都保存到了栈中 。

包括 LR的值。

然后就开始进行 中断处理了。

注意: 这里的栈 , 是对应的异常模式的栈。

然后是异常的返回

首先是将 保存在栈中的 现场 全部恢复到 寄存器中

然后将SPSR 恢复到 CPSR中。

然后将 LR的值, 赋值到PC中,这里 有一个如何计算的问题。这里就是在 返回地址的修正。

对于 中断的话,是这样的。

SUBS PC,LR_irq,#4 ; 一般中断

SUBS PC,LR_fiq,#4 ; 快速中断这是因为,当中断处理时, PC的值已经更新了,所以PC指向的是, 当前指令,往下数3条指令,硬件会自动的 将PC-4的值,保存到LR中,我们之前已经将LR保存到栈中,现在又从栈中取出了LR的值, 现在还要再-4 才能赋值到PC中。

对于SWI 异常来说,当异常发生时,PC的值还未更新,它指向的是,当前指令的向下两条指令,由于硬件自动的将PC-4 保存到LR中了,所以这里就不用动了。指令如图:

MOV PC, LR_svc其他的异常就可以先不看了。

在进行 寄存器恢复的时候,使用的命令。

LDMFD SP_excp!, {r0-r12, pc}^注:SP_excep为对应异常模式下SP,^符号表示恢复SPSR_excep到CPSR。

中断向量表 可以通过协处理器, 定位到 0xFFFF0000 处。

至于 中断做什么 可以由我们指定了。