目录

- 开发板介绍

- 下载仓库

- 工程设计

- 工程构建

- 构建流程

- 工程测试

- Hello World

- LED点灯

- Memory测速

- 替换BIOS

- 开发板信息

开发板介绍

手头目前只有一个购买的BoChenK7开发板,后续会用它来进行LiteX FPGA SoC的构建

测试可能会包括:

- LED:本篇文章

- DDR

- SPI Flash

- SD Card

- Ethernet以太网

- HDMI视频输入输出

- PCIe

下载仓库

LiteX有一个生态库叫做litex-boards,里面包含了上百种开发板(比如Xilinx、Digilent等品牌)

若是你手中有现成的开发板,可以直接使用litex-boards仓库:https://github.com/litex-hub/litex-boards

而我目前手头的是BoChenK7开发板我自己作了一个litex-boards-vacajk仓库:https://github.com/vacajk/litex-boards-vacajk

BoChenK7开发板在Python代码中的名称为:bochen_kintex7_base

litex-boards-vacajk仓库依赖LiteX开发环境,环境搭建方法可以跳转:【LiteX】使用Python实现FPGA SoC构建的开源工具

# 激活conda环境

conda activate <your conda env name>

# 进入litex环境目录

cd ~/Study/litex/env/litex

# 下载仓库

git clone git@github.com:vacajk/litex-boards-vacajk.git

# 安装仓库

cd litex-boards-vacajk

pip install --editable .

工程设计

bochen_kintex7_base开发板的基础配置文件:litex-boards-vacajk/litex_boards_vacajk/targets/bochen_kintex7_base.py

默认情况会开启如下配置:

- --cpu-type=vexriscv

- --with-led-chaser

其他默认不开启的配置包括:

- --with-sdram

- --with-spi-flash

- --with-sdcard

- --with-ethernet

- --with-etherbone

- --with-video-terminal

- --with-video-framebuffer

- --with-video-colorbars

工程构建

# 加载vivado开发环境

$ source ~/Xilinx/Vitis/2021.1/settings64.sh

# 找一个工程目录(如果使用python -m的方法,在哪里运行都无所谓)

$ cd ~/Study/litex/env/litex-boards-vacajk/litex_boards_vacajk

# 编译BIOS、综合、布局、布线、生成bitstream(我们使用默认配置即可实现Hello World和LED点灯的测试)

$ python -m litex_boards_vacajk.targets.bochen_kintex7_base --build

# 编译完成时的log(最后一步为生成bitstream)

Creating config memory files...

Creating bitstream load up from address 0x00000000

Loading bitfile bochen_kintex7_base.bit

Writing file ./bochen_kintex7_base.bin

Writing log file ./bochen_kintex7_base.prm

===================================

Configuration Memory information

===================================

File Format BIN

Interface SPIX4

Size 16M

Start Address 0x00000000

End Address 0x00FFFFFF

Addr1 Addr2 Date File(s)

0x00000000 0x001B35CB Aug 17 20:13:58 2024 bochen_kintex7_base.bit

0 Infos, 0 Warnings, 0 Critical Warnings and 0 Errors encountered.

write_cfgmem completed successfully

# quit

INFO: [Common 17-206] Exiting Vivado at Sat Aug 17 20:13:59 2024...

构建流程

作为第一个工程,这里简单介绍以下LiteX的整体构建流程(自己摸索总结)

TODO:详细介绍

- 运行Python脚本

- 所有LiteX的IP模块都是由Python编写并封装成类

- 运行Python脚本时如果发现有语法、连接错误问题,直接会被Python解释器报错

- 打印SoC结构

- 编译BIOS

- 生成Verilog

- 综合、布局、布线、生成bitstream

工程测试

连接JTAG(USB)、UART(USB)、电源(USB)到BoChenK7开发板

# 查看USB转串口设备名

$ ls /dev/ttyUSB*

/dev/ttyUSB0

# +x属性到USB转串口设备

$ sudo chmod +x /dev/ttyUSB0

提前打开新的BASH Shell,使用litex_term打开串口监听

# BASH B

$ cd ~/Study/litex/env/litex-boards-vacajk/litex_boards_vacajk

$ litex_term /dev/ttyUSB0

打开litex_term后,再进行FPGA bitstream下载

# BASH A

$ cd ~/Study/litex/env/litex-boards-vacajk/litex_boards_vacajk

$ python -m litex_boards_vacajk.targets.bochen_kintex7_base --load

Hello World

查看BASH A中的litex_term命令行

__ _ __ _ __

/ / (_) /____ | |/_/

/ /__/ / __/ -_)> <

/____/_/\__/\__/_/|_|

Build your hardware, easily!

(c) Copyright 2012-2024 Enjoy-Digital

(c) Copyright 2007-2015 M-Labs

BIOS built on Aug 17 2024 20:11:57

BIOS CRC passed (6edd64b6)

LiteX git sha1: 35498b468

--=============== SoC ==================--

CPU: VexRiscv @ 100MHz

BUS: wishbone 32-bit @ 4GiB

CSR: 32-bit data

ROM: 128.0KiB

SRAM: 8.0KiB

--============== Boot ==================--

Booting from serial...

Press Q or ESC to abort boot completely.

sL5DdSMmkekro

Timeout

No boot medium found

--============= Console ================--

litex>

这个命令行控制窗口的打印我们就当它是Hello World了

如果想在其中添加一些自定义log,可以修改C代码:litex/litex/soc/software/bios/main.c

LED点灯

我们的构建中默认添加了LedChaser模块,对接了开发板上的8个LED

上电时,该模块会自动运行流水灯

TODO:照片

我们可以在litex_term命令行中对LED等进行控制

litex> help

leds - Set Leds value

# 查看LEDk控制命令:leds <value>

litex> leds

leds <value>

# 控制LED亮灭

litex> leds 0x55

Settings Leds to 0x55

litex> leds 0xAA

Settings Leds to 0xaa

litex> leds 0xff

Settings Leds to 0xff

litex> leds 0x00

Settings Leds to 0x0

litex>

Memory测速

除了上述的Hello World外,我们还能通过litex_term命令行作一些其它测试

# help查看所有命令

litex> help

LiteX BIOS, available commands:

leds - Set Leds value

flush_cpu_dcache - Flush CPU data cache

crc - Compute CRC32 of a part of the address space

ident - Identifier of the system

help - Print this help

serialboot - Boot from Serial (SFL)

reboot - Reboot

boot - Boot from Memory

mem_cmp - Compare memory content

mem_speed - Test memory speed

mem_test - Test memory access

mem_copy - Copy address space

mem_write - Write address space

mem_read - Read address space

mem_list - List available memory regions

# 查看SoC固件名称

litex> ident

Ident: LiteX SoC on Bochen Kintex7 Base 2024-08-17 20:11:56

# 查看SoC的Memory Map

## ROM:放BIOS程序固件

## SRAM:放BIOS程序固件及运行时程序,空余一些Memory可以作测试

## CSR:SoC寄存器空间

litex> mem_list

Available memory regions:

ROM 0x00000000 0x20000

SRAM 0x10000000 0x2000

CSR 0xf0000000 0x10000

# 测试SRAM读写速度

## 因为SRAM中包含了一些BIOS程序、变量等代码,我们只能取中间一小段对读写带宽进行测试

## 测试命令:mem_speed 0x10001000 0x400

## 测试范围:0x10001000~0x100013FFF

litex> mem_speed 0x10001000 0x400

Memspeed at 0x10001000 (Sequential, 1.0KiB)...

Write speed: 154.7MiB/s

Read speed: 84.9MiB/s

SoC运行速率为100MHz,总线带宽为32bit,理论最大带宽为32/8*100=400MB/s

mem_speed是32bit CPU软件读写SRAM带宽测试,利用率 154.7/400=38.7%,还不错

替换BIOS

之前在仿真时已经测试过替换BIOS的功能:【LiteX】【仿真】使用litex_sim在Python环境中实现FPGA SoC仿真测试

编译demo程序

# --build-path=build/bochen_kintex7_base:指向编译目录,该文件夹中包含了gateware和software子目录

# --mem=rom:告诉编译工具demo.bin运行在rom中(启动地址会和bios.bin相同)

$ cd ~/Study/litex/env/litex-boards-vacajk/litex_boards_vacajk

$ litex_bare_metal_demo --build-path=build/bochen_kintex7_base --mem=rom

构建烧录程序

# BASH A

$ cd ~/Study/litex/env/litex-boards-vacajk/litex_boards_vacajk

# 将demo.bin替换bios.bin,构建FPGA SoC

$ python -m litex_boards_vacajk.targets.bochen_kintex7_base --integrated-rom-init=demo.bin --build

# 下载bitstream到FPGA

$ python -m litex_boards_vacajk.targets.bochen_kintex7_base --integrated-rom-init=demo.bin --load

串口查看demo.bin运行

# BASH B

$ cd ~/Study/litex/env/litex-boards-vacajk/litex_boards_vacajk

$ litex_term /dev/ttyUSB0

LiteX minimal demo app built Aug 17 2024 21:16:24

Available commands:

help - Show this command

reboot - Reboot CPU

led - Led demo

donut - Spinning Donut demo

helloc - Hello C

litex-demo-app> helloc

Hello C demo...

C: Hello, world!

litex-demo-app> donut

Donut demo...

$@@@$$$$$$$

$@@@@$$$###*****##$$

#$$@@@$$$#**!=;===!**#$$$#

#$$@@@@@$$##*=:~:;;==*!*#$$$$#

*#$$$@@@@$$$##*=-,,--~=***#$$@@$$

!*#$$$$@@@@$$$$#*!....~:;!!*#$$@@@$#

=!*###$$$$$$$$$$$$$$##*,~;~=!*#$$$$$$#=

;=!*####$$$$$$$$$$$$$$$########$$$$$$##

~==!***####$$$$$$$$$$$$$$$$$$$$$$$$$$#*!

:;==!!**######$$$$$$$$$$$$$$$$$$$####*=

~;===!!****##########$$#$$########**!=

~:;;==!!!!*****###############***!!=;

.~:;;===!!!!!!**************!!!!==;~

,~::;;;;====!!!!!!!!!!*!!!=====;~

.,~~:;;;;;;;======!!;==;;:::~,

,--::::;:;;;;;:;;::::~-.

litex-demo-app>

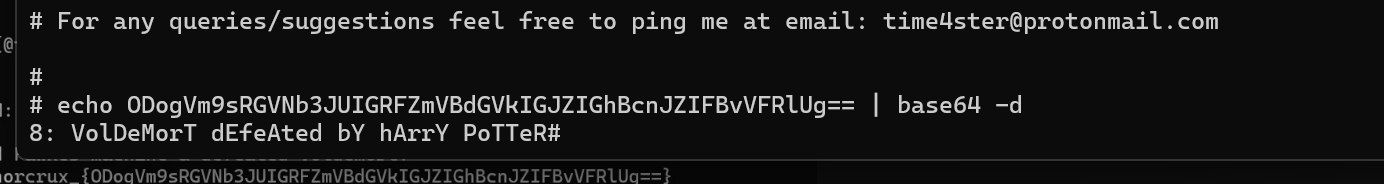

开发板信息

BoChenK7开发板的接口如下图,还是比较丰富的