- JTAG (Joint Test Action Group) 是一种串行通信协议。对于典型的串行通信,总线较少,线路数通常为1到4条,数据是以位为单位依次传输的。

- 笔记中大部分图片来自JTAG标准介绍UP的视频

- IEEE 1149.1,通常称为JTAG(Joint Test Action Group),是一个标准化的测试方法,用于对集成电路(IC)和电路板进行测试和调试。该标准定义了在芯片上设置的测试访问端口(TAP),通过串行扫描链控制芯片内部的寄存器,从而测试和调试芯片或电路板。

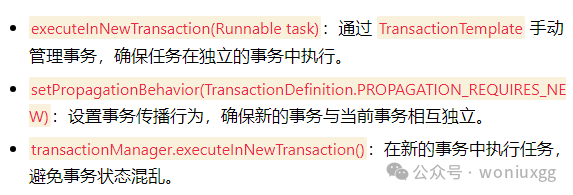

边界扫描寄存器

- 符合 JTAG 标准的芯片,如许多微处理器、微控制器、FPGA、CPLD 以及一些复杂的数字芯片,通常都包含边界扫描寄存器。

- 内部蓝色的方框:边界扫描寄存器通过将芯片的每个 I/O 引脚与一个可控的寄存器单元相连接,提供了一种强大的测试和调试机制。它能够有效地检测和定位电路板中的故障,并且广泛应用于集成电路和 PCB 的生产测试与调试过程中。

IEEE1149.1

IEEE 1149.1,也称为标准测试访问端口和边界扫描架构(Standard Test Access Port and Boundary-Scan Architecture),是由电气和电子工程师协会(IEEE)制定的一个标准。这个标准通常也被称为 JTAG(Joint Test Action Group),因为它是在一个名为 JTAG 的行业工作组的推动下开发的。IEEE 1149.1 广泛应用于电子行业中复杂集成电路和电路板的测试与调试。它通过定义标准的测试接口和边界扫描架构,提供了一种高效、灵活的测试方法,极大地提高了生产和维护的效率。

IEEE 1149.1 标准的主要内容:

-

测试访问端口(TAP):

- IEEE 1149.1 定义了一种标准的测试访问端口(Test Access Port, TAP),这个端口包括一组引脚:TDI(Test Data In,测试数据输入)、TDO(Test Data Out,测试数据输出)、TMS(Test Mode Select,测试模式选择)、TCK(Test Clock,测试时钟)和可选的 TRST(Test Reset,测试复位)。

- TAP 用于在芯片内部访问测试和调试功能,包括边界扫描寄存器、指令寄存器等。

-

边界扫描架构:

- 标准定义了一种边界扫描架构,允许对集成电路(IC)引脚进行测试,而无需直接访问内部节点。通过在每个 I/O 引脚上附加一个边界扫描单元(Boundary Scan Cell),可以通过串行数据传输对引脚状态进行检查和控制。

- 这种架构极大地简化了对复杂电路板的测试,尤其是在高密度或多层电路板上。

-

状态机(TAP 控制器):

- IEEE 1149.1 标准定义了一种有限状态机,称为 TAP 控制器,用于控制测试过程中的状态转换。TAP 控制器有 16 个状态,通过 TMS 信号控制状态的转移,实现对芯片内部的测试和调试操作。

- 更多可参考嵌入式系统Linux内核开发实战指南

- 根据状态转移图示链接,TRST可选就是因为通过对TMS连续赋值5个1,TAP 控制器将回到复位状态。

-

指令寄存器和数据寄存器:

- 标准还定义了指令寄存器和数据寄存器的结构。指令寄存器用于选择芯片内部的测试模式,而数据寄存器则用于传输测试数据和结果。边界扫描寄存器、ID 寄存器(用于识别芯片)等都属于数据寄存器。

JTAG 的 TMS (Test Mode Select) 引脚是 JTAG 接口中的一个关键控制信号,用于控制和管理 JTAG 状态机的状态转换。JTAG 协议使用一个有限状态机(Finite State Machine, FSM),称为 TAP (Test Access Port) 控制器来管理各种测试操作。TMS 信号通过控制 TAP 状态机的状态,决定 JTAG 接口当前处于哪种操作模式。

TMS 的主要功能与作用:

-

TAP 状态机有 16 个不同的状态,例如 Test-Logic-Reset、Run-Test/Idle、Shift-DR、Shift-IR 等。TMS 信号决定了状态机的下一步状态。

当 JTAG 时钟(TCK)信号上升沿时,根据 TMS 信号的高低,状态机会从一个状态转移到另一个状态。 -

TMS 信号可以选择数据寄存器操作(DR 操作)和指令寄存器操作(IR 操作)。通过适当的 TMS 序列,用户可以进入特定的模式以执行诸如数据移位、测试逻辑复位或运行测试等操作。

测试操作流程

3.1. 进入测试模式

- 首先,通过TMS引脚的序列将TAP控制器置于Test-Logic-Reset状态,以确保控制器处于已知的初始状态。

- 通过TMS的特定信号序列,将TAP控制器转换到Run-Test/Idle状态,准备进行测试。

3.2. 选择指令寄存器(IR)或数据寄存器(DR)

- TAP控制器根据TMS信号的控制,进入Shift-IR或Shift-DR状态。

- 在Shift-IR状态,TDI上的数据会移入指令寄存器(IR),这决定了下一步要执行的操作(如边界扫描、旁路模式等)。

- 在Shift-DR状态,TDI上的数据会移入选定的数据寄存器,如边界扫描寄存器、旁路寄存器等。

3.3. 执行测试指令

- 当指令寄存器(IR)加载完成后,TAP控制器进入Update-IR状态,更新当前的测试指令。

- 然后,通过TAP控制器的状态转换,执行加载到指令寄存器中的指令。例如:

- 边界扫描测试(Boundary-Scan Test): 执行完整的边界扫描链数据移位,检测IC引脚的逻辑状态。

- 旁路测试(Bypass Test): 跳过芯片内核,只测试外部连接的其他芯片。

- 内置自测试(BIST): 执行芯片内部的自测试程序。

3.4. 读取测试结果

- 通过TAP控制器的控制,可以进入Shift-DR状态,将测试结果从数据寄存器(如边界扫描寄存器)移出,通过TDO引脚读取。

- 根据TAP控制器的状态转换,测试结果数据可以从目标寄存器中顺序移出,供测试设备分析。

3.5. 完成测试并复位

- 测试完成后,TAP控制器可以通过TMS信号转换回Test-Logic-Reset状态,复位TAP控制器以准备下一次测试。

旁路寄存器

-

旁路寄存器(Bypass Register)是 IEEE 1149.1(JTAG)标准中的一种特殊寄存器,它的主要作用是在不需要对某个芯片进行测试时,为数据提供一条快速的“旁路”路径,从而使数据能够绕过不参与测试的芯片,并快速传递到下一个芯片或目标芯片。

-

旁路寄存器是一个非常简单的寄存器,它只有 1 位(比特)的长度。当选择旁路寄存器时,输入的数据(通过 TDI 引脚进入)会直接通过这个单比特寄存器,并立即从 TDO 引脚输出。

-

当多个芯片串联在同一个 JTAG 链中时,旁路寄存器允许不需要测试的芯片将数据直接传递给下一个芯片,而不必通过完整的边界扫描寄存器链。这样可以减少不必要的延迟,显著提高测试速度。

-

当 TAP 控制器的状态机进入旁路模式(通过加载旁路指令进入这个模式)时,旁路寄存器被选中作为活动的数据寄存器。此时,芯片的边界扫描寄存器和其他测试逻辑被旁路,数据可以快速通过。

-

假设有三个芯片 A、B 和 C 串联在同一个 JTAG 链中,如果只需要测试芯片 B和 C,而不需要测试 A ,那么可以在芯片 A 中激活旁路寄存器,使得它们的 TDI 数据直接通过旁路寄存器传递给 B。

IEEE1149.4

IEEE 1149.4 标准,全称为混合信号测试总线标准(Standard for a Mixed-Signal Test Bus),是继 IEEE 1149.1(JTAG)标准之后制定的,专门用于支持混合信号(包括模拟和数字信号)的电路测试。该标准扩展了原有的 JTAG 边界扫描标准,使其不仅适用于数字信号,还可以测试和诊断模拟信号通道。

- IEEE 1149.4 标准特别适用于包含数字和模拟模块的集成电路,如模数转换器(ADC)、数模转换器(DAC)、电源管理芯片和音频处理器等。

IEEE 1149.4 的主要内容

-

扩展的测试总线架构:

- IEEE 1149.4 在 IEEE 1149.1 的基础上增加了对模拟信号的支持。它引入了新的引脚和结构来支持模拟信号的测试,

并且与原有的 JTAG 数字测试功能兼容。

- IEEE 1149.4 在 IEEE 1149.1 的基础上增加了对模拟信号的支持。它引入了新的引脚和结构来支持模拟信号的测试,

-

新增引脚:

- AT1 和 AT2: IEEE 1149.4 标准引入了两个专门用于模拟信号测试的引脚,称为 Analog Test Pin 1 (AT1) 和 Analog Test Pin 2 (AT2)。这些引脚用于在芯片内部和外部设备之间传输模拟测试信号。

- AT1 和 AT2 引脚可以在芯片内部切换,以连接到需要测试的模拟电路部分,从而进行信号传输或测量。

-

模拟边界扫描单元(Analog Boundary Module, ABM):

-

IEEE 1149.4 引入了模拟边界扫描单元,用于管理模拟信号的测试。这些单元能够控制信号的传输路径,并执行基本的模拟测试操作,如电压测量或信号注入。

-

IEEE 1149.4 标准还包括机制来隔离或连接特定的模拟电路部分,使得测试过程更加灵活和精确。通过控制 ABM 单元,测试设备可以选择性地对电路中的特定部分进行操作,而不影响其他部分的正常工作。

-

IEEE1149.5

- IEEE 1149.5 标准是关于模块测试和维护总线标准(Standard for Module Test and Maintenance Bus, MTM-Bus)的规范,旨在为系统级测试提供一种标准化的接口和协议。该标准主要应用于大型电子系统中的模块化测试和维护,尤其是在高复杂度的系统中。

IEEE1149.6

IEEE 1149.6 标准,全称为用于测试高级数字网络的边界扫描标准(Standard for Boundary-Scan Testing of Advanced Digital Networks),是对 IEEE 1149.1 标准的扩展,专门用于支持高速信号和 AC 耦合信号的测试。

- 随着高速数字信号(如千兆以太网、PCI Express 等)的广泛应用,传统的 IEEE 1149.1 标准在测试这些信号时显得力不从心,特别是在测试 AC 耦合信号链路时(1149.1的PAD之间通过导线链接,而芯片间可能是复杂的电路结构链接,直流信号无法通过这些电路,AC 耦合信号直流隔离,高频响应)。

- IEEE 1149.6 是对 IEEE 1149.1 的扩展,因此它与 IEEE 1149.1 保持兼容。当多个芯片连接在一起形成复杂的高速信号链路时,IEEE 1149.6 提供了测试这些链路完整性和信号质量的方法,确保多芯片系统的可靠性。

驱动器(Driver)和接收器(Receiver)

在 IEEE 1149.6 标准中,驱动器(Driver)和接收器(Receiver)是用于测试高速数字信号和 AC 耦合链路的重要组件。IEEE 1149.6 扩展了传统的 IEEE 1149.1 标准,以适应这些高速信号的测试需求,并特别关注驱动器和接收器在差分信号和 AC 耦合信号链路中的行为。

驱动器 (Driver)

驱动器 是负责在链路上传输测试信号的电路组件。它在 IEEE 1149.6 测试过程中扮演重要角色,确保信号能够正确地发送到目标设备,并通过链路传输。

功能:

-

高频信号生成:

- 驱动器能够产生适合测试的高频信号,以模拟正常工作条件下的高速数字信号。这些信号必须足够快,以便测试系统能够检测到在 AC 耦合链路或差分信号链路中可能发生的问题。

-

差分信号驱动:

- 在差分信号链路中,驱动器需要同时驱动两个相互关联的信号线(如差分对)。IEEE 1149.6 的驱动器设计支持这种模式,以确保差分信号的正确性和完整性。

-

AC 耦合信号驱动:

- 驱动器需要能够在 AC 耦合链路上有效工作。它必须生成信号,能够穿过耦合电容器,并在接收器端保持足够的信号强度和完整性,以便进行正确的测试和接收。

-

直流偏置控制:

- 在某些应用中,驱动器还需要控制直流偏置电平,以确保信号能够正确地通过 AC 耦合链路,而不会受到偏置问题的影响。

接收器 (Receiver)

接收器 是负责接收链路上传输信号的组件。在 IEEE 1149.6 中,接收器需要具有检测和处理高速信号的能力,尤其是在这些信号通过 AC 耦合链路后可能发生衰减或失真的情况下。

- 延迟匹配和信号完整性测试:

高速信号的延迟匹配和完整性对于系统的可靠性至关重要。IEEE 1149.6 提供了方法来测试信号延迟,并确保信号在高速传输时保持完整。

IEEE1500

- IEEE 1500 标准,全称为嵌入式核心测试标准(Standard for Embedded Core Test, SECT),是一项专门为复杂系统级芯片(System-on-Chip, SoC)设计的测试标准。随着芯片集成度的提高,SoC 内部通常包含多个嵌入式核心(如处理器、存储器、专用功能模块等),这些核心的测试和验证变得越来越复杂。IEEE 1500 标准旨在为这些嵌入式核心提供一种统一的测试结构和方法,以提高测试的效率和可重复性。

IEEE1687

IEEE1838

IEEE1149.10

![【题解】【一题多解】—— [NOIP1998 普及组] 三连击](https://i-blog.csdnimg.cn/direct/e27d016705c64932ba65dd18e1f166c4.jpeg#pic_center)